**ABSTRACT**

Title of Document: ULTRA SMALL ANTENNA AND LOW

POWER RECEIVER FOR SMART DUST

WIRELESS SENSOR NETWORKS

Bo Yang

Doctor of Philosophy, 2009

Directed By: Professor Neil Goldsman

Department of Electrical and Computer

Engineering

Wireless Sensor Networks have the potential for profound impact on our daily lives. Smart Dust Wireless Sensor Networks (SDWSNs) are emerging members of the Wireless Sensor Network family with strict requirements on communication node sizes (1cm³) and power consumption (< 2mW during short on-states). In addition, the large number of communication nodes needed in SDWSN require highly integrated solutions. This dissertation develops new design techniques for low-volume antennas and low-power receivers for SDWSN applications. In addition, it devises an antenna and low noise amplifier co-design methodology to increase the level of design integration, reduce receiver noise, and reduce the development cycle.

This dissertation first establishes stringent principles for designing SDWSN electrically small antennas (ESAs). Based on these principles, a new ESA, the F-Inverted Compact Antenna (FICA), is designed at 916MHz. This FICA has a

significant advantage in that it uses a small-size ground plane. The volume of this FICA (including the ground plane) is only 7% of other state-of-the-art ESAs, while its efficiency (48.53%) and gain (-1.38dBi) are comparable to antennas of much larger dimensions. A physics-based circuit model is developed for this FICA to assist system level design at the earliest stage, including optimization of the antenna performance. An antenna and low noise amplifier (LNA) co-design method is proposed and proven to be valid to design low power LNAs with the very low noise figure of only 1.5dB.

To reduce receiver power consumption, this dissertation proposes a novel LNA active device and an input/ouput passive matching network optimization method. With this method, a power efficient high voltage gain cascode LNA was designed in a 0.13μm CMOS process with only low quality factor inductors. This LNA has a 3.6dB noise figure, voltage gain of 24dB, input third intercept point (IIP3) of 3dBm, and power consumption of 1.5mW at 1.0V supply voltage. Its figure of merit, using the typical definition, is twice that of the best in the literature. A full low power receiver is developed with a sensitivity of -58dBm, chip area of 1.1mm², and power consumption of 2.85mW.

# ULTRA SMALL ANTENNA AND LOW POWER RECEIVER FOR SMART DUST WIRELESS SENSOR NETWORKS

By

Bo Yang

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2009

Advisory Committee: Professor Neil Goldsman, Chair/Advisor Dr. Quirino Balzano Professor Martin C. Peckerar Professor Shuvra S. Bhattacharyya Professor Ellen Williams © Copyright by Bo Yang 2009

# Acknowledgements

It is a pleasure to thank those who made this dissertation possible.

First and foremost, I am heartily thankful to my advisor, Prof. Neil Goldsman, for the great opportunity he offered me to work with him and for guiding me through the research. His vision for this interdisciplinary cutting-edge technology, his encouragement, his support, and his supervision had led me through the entire research project. It would have been next to impossible to write this dissertation without his help and guidance. In addition, his enthusiasm for his career will continuously inspire me in the rest of my life. I am truly grateful to Dr. Quirino Balzano, my co-advisor, whose broad vision and industry experience in wireless portable devices, guidance, and pleasant personality have made this research experience both rewarding and joyful. What I learned from him has not only been about research, but also about professional life. I would also like to thank Prof. Martin Peckerar, who was a committee member at my Master's defense and doctoral proposal exam, as well as the instructor of my analog circuit and device physics courses. His passion for both research and educating students and junior researchers will have an impact in my future career. My appreciation also goes to Prof. Shuvra Bhattacharyya, who was a committee member at my dissertation proposal exam. I would also like to thank Prof. Ellen Williams for kindly consenting to join the defense committee and review this dissertation.

I have been fortunate to collaborate with many brilliant and supportive people through the years. In particular, I would like to thank Dr. Xi Shao for his valuable discussions on antenna and electromagnetic problems. I also thank Dr. Thomas Salter,

Dr. Todd Firestone, and Mr. Donald M. Witters, Jr., for providing testing instruments. I have appreciated the co-operation with several Smart Dust project team members: Dr. Zynep Dilli, Mr. Bo Li, Dr. Thomas Salter, Dr. Chung-Ching Shen, Ms. Datta Sheth, Dr. Felice Vanin, Mr. Shaun Simmons, and Ms. Yiming Zhai. I also thank Prof. Pamela Abshire, Dr. Akin Akturk, Dr. Siddarth Potbhare, Prof. Ohmar Ramahi, Dr. John Rodgers, and Dr. Bai Yun for very profitable discussions. My appreciation also goes to Mr. Jay Renner, Mr. Shyam Mehrotra, Mr. Bryan Quinn, Mr. Joe Kselman, and Mr. Jay Pyle for technical support.

Next, I would like to thank my family. I thank my parents for providing me the best education that I could ever have and teaching me be optimistic during difficult times. I want to thank my husband, Tao, for his love and encouragement from college times onward.

Lastly, I offer my regards and blessings to all of those who supported me in any respect during the completion of this project.

# Table of Contents

| Acknowledgements                                                            | ii    |

|-----------------------------------------------------------------------------|-------|

| Table of Contents                                                           | iv    |

| List of Tables                                                              | vi    |

| List of Figures                                                             | . vii |

| Chapter 1 Introduction                                                      | 1     |

| 1.1 Motivation                                                              | 1     |

| 1.2 Contributions                                                           | 2     |

| 1.3 Thesis Structure                                                        | 7     |

| Chapter 2 Design Philosophy for Smart Dust Wireless Sensor Networks (SDWSN) | ) 9   |

| 2.1 Smart Dust Wireless Sensor Networks (SDWSN)                             | . 10  |

| 2.1.1 The Concepts of WSN and SDWSN                                         | . 10  |

| 2.1.2 Smart Dust Requirements                                               | . 11  |

| 2.2 Design Challenges                                                       | . 12  |

| 2.2.1 Low Power                                                             | . 13  |

| 2.2.2 Low Cost                                                              | . 13  |

| 2.2.3 Low Form Factor                                                       | . 14  |

| 2.3 Design Trade-Offs                                                       | . 14  |

| 2.4 State of the Art                                                        | . 17  |

| 2.4.1 Direct Conversion Receiver                                            | . 17  |

| 2.4.2 Low IF Receiver                                                       | . 19  |

| 2.4.3 Super-Regenerative Receiver                                           | . 20  |

| 2.4.4 Proposed Receiver Architecture: Direct Demodulation Receiver (DDR)    | . 22  |

| 2.5 Receiver Design Goals                                                   | . 23  |

| 2.5.1 Sensitivity Requirements                                              | . 24  |

| 2.5.2 Receiver Budget                                                       | . 27  |

| 2.6 Conclusion                                                              | . 28  |

| Chapter 3 Scalable Highly Efficient Electrically Small Antennas (ESA)       | . 29  |

| 3.1 ESA State of the Art                                                    | . 30  |

| 3.2 The Need for ESA in Smart Dust System                                   | . 37  |

| 3.3 Design Guidelines for ESAs                                              | . 39  |

| 3.3.1 Antenna Height                                                        | . 39  |

| 3.3.2 Antenna Loss                                                          | . 40  |

| 3.3.3 Antenna Volume                                                        | . 41  |

| 3.4 Innovative ESAs: F-Inverted Compact Antennas (FICAs)                    | . 42  |

| 3.4.1 Design Origins                                                        | . 43  |

| 3.4.2 Innovative ESAs                                                       | . 45  |

| 3.4.3 Principle of Operation                                                | . 50  |

| 3.4.4 Using Baluns in ESA Tests                                             |       |

| 3.4.5 Simulation and Measurements                                           | . 55  |

| 3.4.6 Antenna on a Live Radio                                               | . 64  |

| 3.4.7 FICA Parametric Study                                                 | . 66  |

| 3.5 Ground Plane Effect for ESA and FICA                                    | .71   |

| 3.6 FICA Circuit Model                                              | 73        |

|---------------------------------------------------------------------|-----------|

| 3.7 Scaling FICA to Other Frequencies                               | 80        |

| 3.8 Conclusion                                                      | 83        |

| Chapter 4 Low Power Low Noise Amplifier Optimization                | 85        |

| 4.1 Introduction                                                    | 86        |

| 4.1.1 Existing LNA Design and Optimization Methods                  | 86        |

| 4.1.2 Cascode LNA Design Space Exploration                          | 88        |

| 4.2 Optimizing Low Power LNA Sizing and Biasing                     |           |

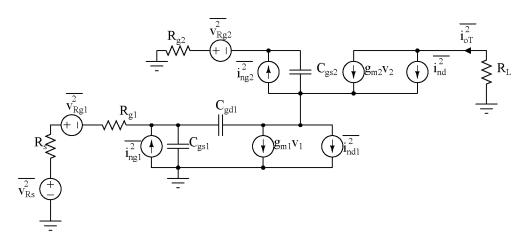

| 4.2.1 Cascode LNA Transistor Optimization Modeling                  | 90        |

| 4.2.2 Systematic Investigation of Transistor Sizing and Biasing     |           |

| 4.3 Optimizing Matching Networks                                    | 103       |

| 4.3.1 Voltage Gain Oriented Design                                  | 103       |

| 4.3.2 Voltage Gain and Noise Figure Trade-Offs                      | 107       |

| 4.4 Optimizing Input Matching Networks                              | 110       |

| 4.4.1 Input Matching Network Design Guideline for Unilateral Circ   | cuits 110 |

| 4.4.2 Input Matching Network Design Guideline for Bilateral Circu   | its 113   |

| 4.5 Optimizing Output Matching Circuit                              | 120       |

| 4.6 A 2.2GHz LNA Design Example                                     | 121       |

| 4.7 Conclusion                                                      |           |

| Chapter 5 Antenna and Low Noise Amplifier (LNA) Co-Design           | 127       |

| 5.1 Introduction                                                    | 128       |

| 5.2 FICA Circuit Model                                              |           |

| 5.3 Optimum Noise Matching Using Antenna-LNA Co-Design              | 132       |

| 5.4 Conclusion                                                      |           |

| Chapter 6 Low Power Receiver for Smart Dust Wireless Sensor Network | ks 138    |

| 6.1 Introduction                                                    | 139       |

| 6.2 Receiver Circuitry                                              |           |

| 6.2.1 Demodulator                                                   |           |

| 6.2.2 Auxiliary Amplifier                                           |           |

| 6.2.3 Comparator                                                    |           |

| 6.3 Layout and Experimental Results                                 |           |

| 6.4 Transceiver Design and Results                                  |           |

| 6.5 Conclusion                                                      | 178       |

| Chapter 7 Summary and Future Work                                   |           |

| 7.1 Research Summary                                                |           |

| 7.2 Future Work                                                     |           |

| 7.2.1 Radio Units for SDWSN at Tens of GHz                          |           |

| 7.2.2 System Integration                                            |           |

| 7.2.3 New SDWSN Radio with Advanced Technology                      |           |

| Appendix A                                                          |           |

| Appendix B                                                          |           |

| Bibliography                                                        | 191       |

|                                                                     |           |

# List of Tables

| Table 1.1 | Antenna performance summary (NA=Not Available)                               | 3   |

|-----------|------------------------------------------------------------------------------|-----|

| Table 1.2 | Literature results shown in Fig. 1.1 and Fig. 1.2                            |     |

| Table 1.3 | Summary of receiver performance                                              | 7   |

| Table 2.1 | Wireless personal area network (WPAN) IEEE standards                         | 10  |

| Table 2.2 | Path loss (dB) for 2.2GHz SDWSN communication                                | 25  |

| Table 3.1 | Antenna performance summary (NA=Not Available)                               | 64  |

| Table 3.2 | Variables used in parametric simulation                                      | 67  |

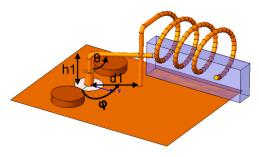

| Table 3.3 | Resonance frequency (fc) of FICA for different h1, d1, $\theta$ , and $\phi$ | 68  |

| Table 3.4 | Values used in coil parametric study                                         | 69  |

| Table 3.5 | Gain of chip antenna assembled on different PCBs                             | 73  |

| Table 3.6 | Measured FICA input impedance at resonance                                   | 77  |

| Table 4.1 | Literature results shown in Fig. 4.28                                        | 125 |

| Table 6.1 | Simulation parameters used in Fig. 6.4                                       | 146 |

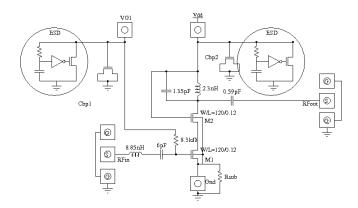

| Table 6.2 | Component values used in Fig. 6.12                                           | 156 |

| Table 6.3 | Comparator types and characteristics                                         | 159 |

| Table 6.4 | Sizes of transistors in Fig. 6.16                                            | 162 |

| Table 6.5 | Summary of receiver performance                                              | 173 |

| Table 6.6 | Component parameters in Fig. 6.25. (W/L in µm/µm)                            | 176 |

| Table 6.7 | Transceiver operation status vs. control bits                                | 176 |

|           | =                                                                            |     |

# List of Figures

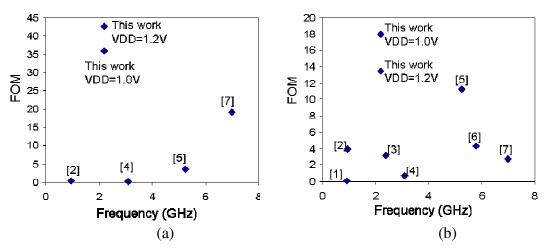

| Fig. 1.1  | FoM of LNAs. References in this figure can be found in Table. 1.24                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2  | FoM $(FoM2 = (Gain \cdot f) / (F - 1) / P_{dc})$ of LNAs. References in this                                          |

|           | figure can be found in Table. 1.26                                                                                    |

| Fig. 2.1  | SDWSN design tradeoffs                                                                                                |

| Fig. 2.2  | Block diagram of a direct conversion receiver                                                                         |

| Fig. 2.3  | Block diagram of low-IF receiver20                                                                                    |

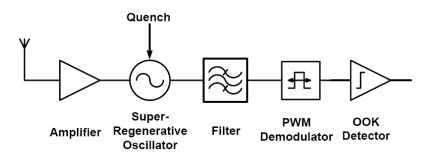

| Fig. 2.4  | Block diagram of super-regenerative receiver [Otis05]21                                                               |

| Fig. 2.5  | Block diagram of direct demodulation receiver (DDR) for OOK23                                                         |

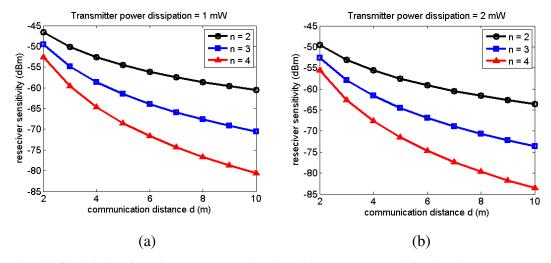

| Fig. 2.6  | Sensitivity of receiver vs. communication distance d and modification                                                 |

|           | index n. Left: transmitter dissipates 1mW. With 40% efficiency,                                                       |

|           | effectively transmitted power is 0.4mW. Right: transmitter dissipates                                                 |

|           | 2mW. With 40% efficiency, effectively transmitted power is 0.8mW26                                                    |

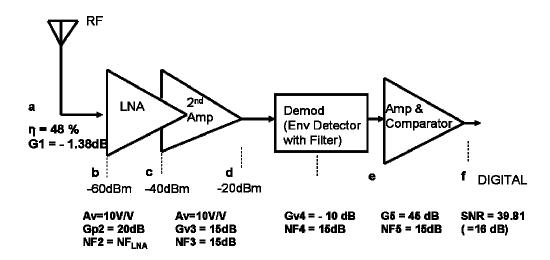

| Fig. 2.7  | OOK receiver block diagram with gain and noise estimations27                                                          |

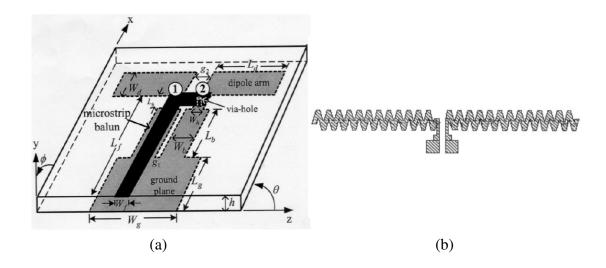

| Fig. 3.1  | Printed dipole antennas: (a) printed dipole antennas on PCB [Chuang03],                                               |

|           | (b) printed dipole on silicon substrates [Lin04]31                                                                    |

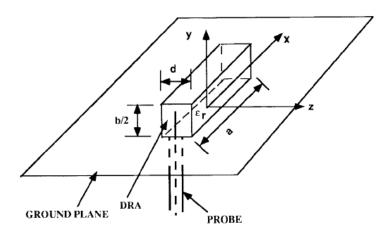

| Fig. 3.2  | Rectangular dielectric resonance antenna placed on a ground plane                                                     |

|           | [Mongia97]32                                                                                                          |

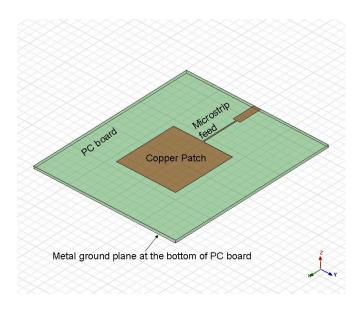

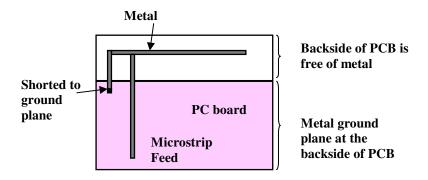

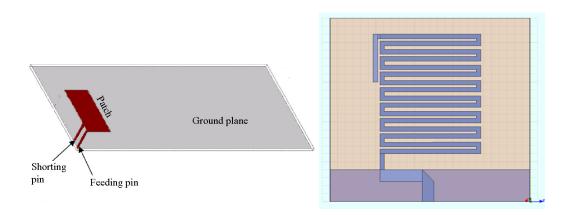

| Fig. 3.3  | Microstrip patch antennas                                                                                             |

| Fig. 3.4  | Diagram of an inverted-F antenna (IFA)34                                                                              |

| Fig. 3.5  | Planar Inverted-F antennas (PIFA) (left) [Boyle06] and meander line PIFA                                              |

|           | (right) [Pham04]35                                                                                                    |

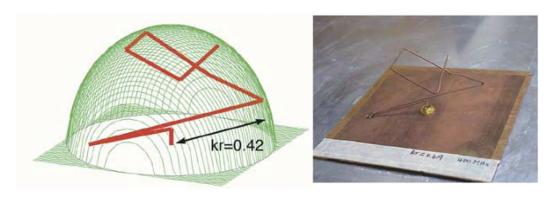

| Fig. 3.6  | Genetic algorithm antennas [Choo05]. Left: theoretical design. Right:                                                 |

|           | photo of implemented antenna                                                                                          |

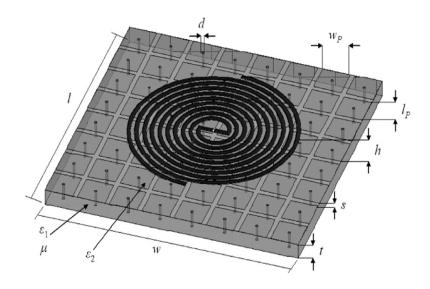

| Fig. 3.7  | A spiral antenna with electromagnetic band-gap (EBG) structures                                                       |

|           | [Bell04]37                                                                                                            |

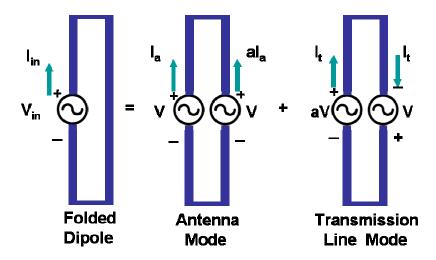

| Fig. 3.8  | Operation principles of folded dipole antennas                                                                        |

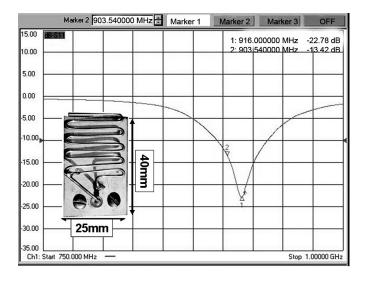

| Fig. 3.9  | Measured S11 of the wired meander line with no dielectric loading. The                                                |

|           | antenna is made with 1mm diameter copper wires. The antenna height is                                                 |

|           | 8mm (0.024 $\lambda$ ). The ground plane is 25mm $\times$ 40mm (0.076 $\lambda \times$ 0.122 $\lambda$ at             |

|           | 916MHz). The bandwidth is 40MHz, about 4.4% at 916MHz46                                                               |

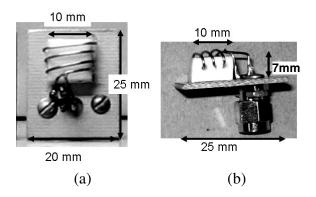

| Fig. 3.10 | Top view (a) and side view (b) of the dielectric loaded FICA antenna. The                                             |

|           | size of the ground plane is $20\text{mm} \times 25\text{mm}$ ( $0.06\lambda \times 0.08\lambda$ at $916\text{MHz}$ ). |

|           | The height of the antenna is 7mm. The dielectric load is a Teflon block                                               |

|           | with size $10\text{mm} \times 10\text{mm} \times 6\text{mm}$ , and a relative dielectric constant of                  |

|           | 2.247                                                                                                                 |

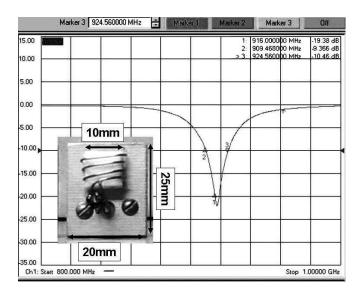

| Fig. 3.11 | Measured S11 of the wired FICA with Teflon dielectric loading. The                                                    |

|           | geometry of the FICA is shown in detail in Fig. 3.10. The bandwidth is                                                |

|           | 15MHz at -10dB, which is around 1.6% at 916MHz48                                                                      |

| Fig. 3.12 | Photographs of (a) side view and (b) top view of the 916MHz FICA. The                                                 |

|           | total volume (including ground plane) is 8mm $\times$ 20mm $\times$ 25mm (0.06 $\lambda$ $\times$                     |

|           | $0.076\lambda \times 0.024\lambda$ )50                                                                                |

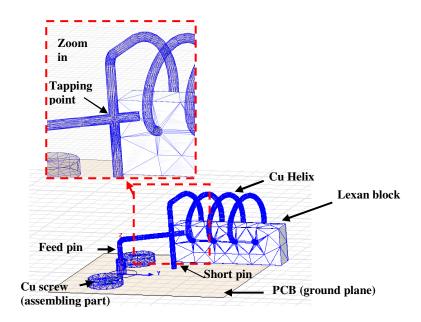

| Fig. 3.13 |                                                                                                                       |

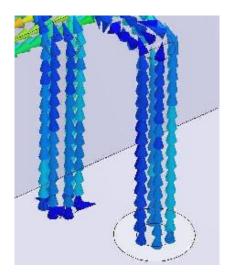

| Fig. 3.14 | Current density distribution on FICA wires52                                                     |

|-----------|--------------------------------------------------------------------------------------------------|

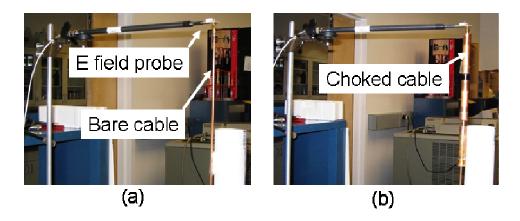

| Fig. 3.15 | Near field measurement construction54                                                            |

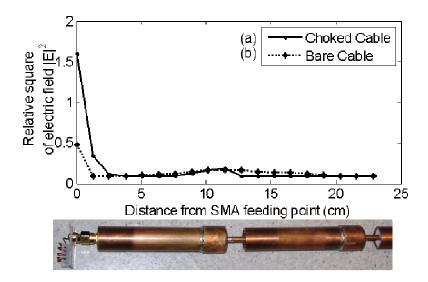

| Fig. 3.16 | Top: Near electric field measurement results of antennas fed by different                        |

|           | cables. (a) Field measured with choked cable. (b) Field measured with a                          |

|           | simple coaxial cable without RF chokes. Bottom: Photo of AUT fed by                              |

|           | choked cable55                                                                                   |

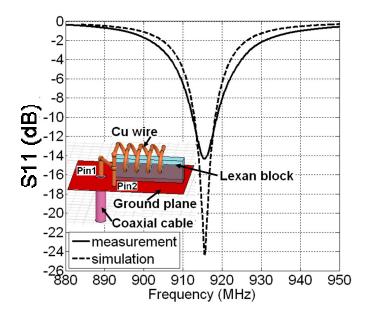

| Fig. 3.17 | Simulated and measured S11 of the FICA. Simulation: center frequency is                          |

|           | 915MHz; -3dB bandwidth is 16.8MHz. Measurement: center frequency is                              |

|           | 915.2MHz; -3dB bandwidth is 22.4MHz. Embedded plot: models used in                               |

|           | HFSS. Pin1: feeding pin. Pin2: shorting pin. Ground plane size: 20mm ×                           |

|           | 2 5 m m                                                                                          |

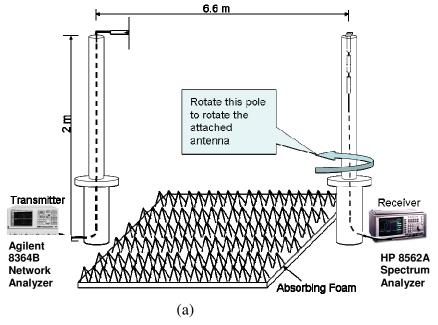

| Fig. 3.18 | Experimental settings for radiation pattern test. (a) Diagram of the setting.                    |

| _         | (b) Setting in an open field. (c) Setting inside an anechoic chamber58                           |

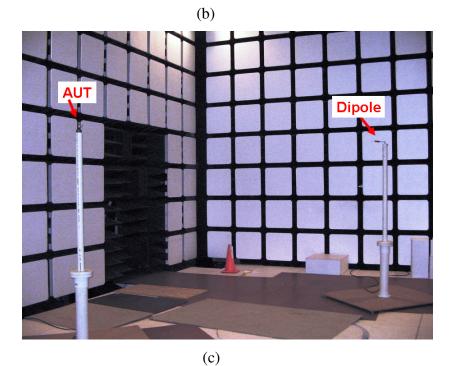

| Fig. 3.19 | (a) $E_{\phi}$ and $E_{\theta}$ defined in the FICA XY plane. (b) Measured and simulated         |

|           | radiation pattern (gain) of the antenna on the XY plane60                                        |

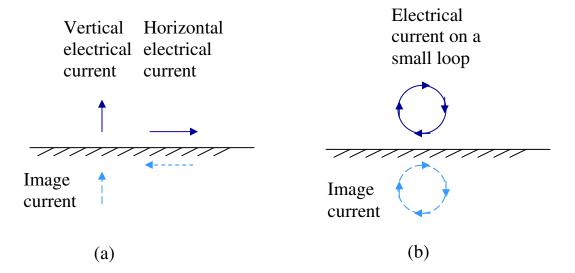

| Fig. 3.20 | Image current. (a) Image current of vertical and horizontal electrical                           |

|           | current over a ground plane. (b) Image current of electrical current on a                        |

|           | small loop over a ground plane62                                                                 |

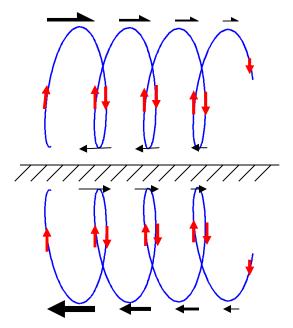

| Fig. 3.21 | Electrical current and its image current along the helix of FICA63                               |

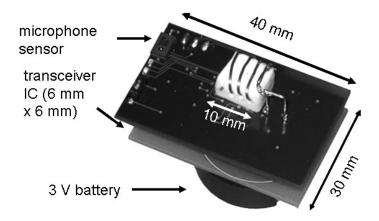

| Fig. 3.22 | Sensor node used in field measurements65                                                         |

| Fig. 3.23 | Geometric representation of some analyzed parameters67                                           |

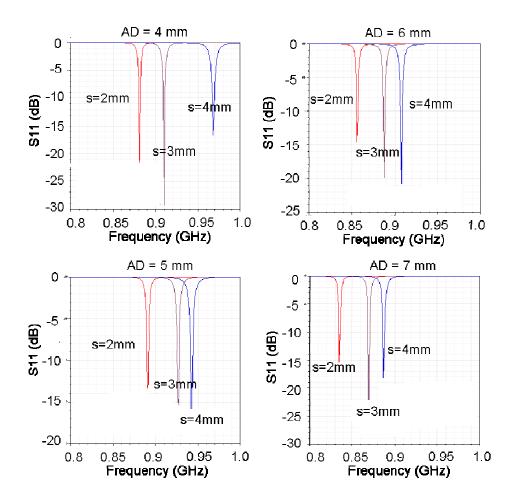

| Fig. 3.24 | Simulated S11 with different spacing s. AD and N are adjusted                                    |

|           | simultaneously such that the length of the wire from the tapping point to                        |

|           | the open end is roughly constant. Other parameters in the analysis have the                      |

|           | default values in Table 3.2                                                                      |

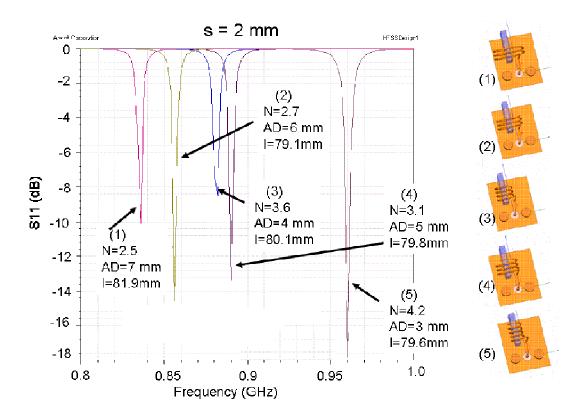

| Fig. 3.25 | Simulated S11 with different major diameters for the coil and $s = 2mm$ .                        |

|           | AD and N are adjusted simultaneously such that the length of the wire                            |

|           | from the tapping point to the open end is roughly constant. Other                                |

|           | parameters in the analysis have the default values in Table 3.271                                |

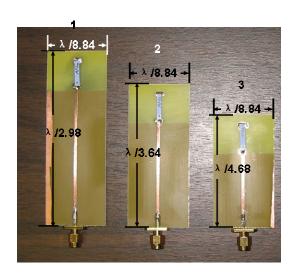

| Fig. 3.26 | Commercial 916MHz chip antenna assembled on PCBs of different sizes.                             |

|           | From left to right: Chip antenna on PCB1; Chip antenna on PCB2; Chip                             |

|           | antenna on PCB373                                                                                |

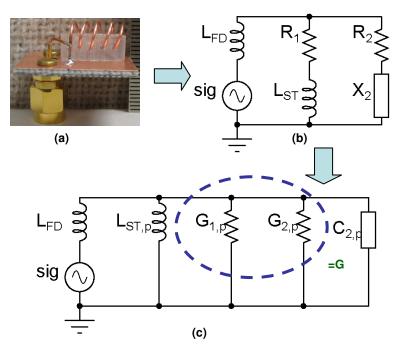

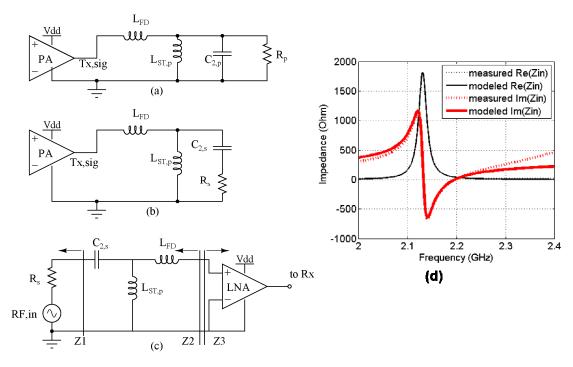

| Fig. 3.27 | FICA circuit. (a) Photo of FICA; (b) circuit model of FICA; (c) equivalent                       |

|           | circuit of (b)75                                                                                 |

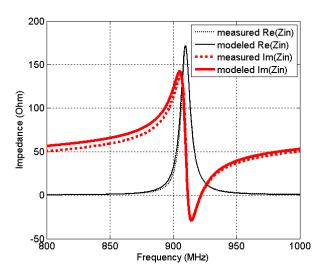

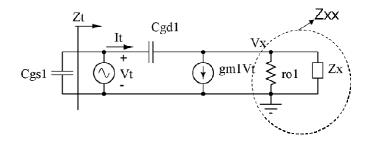

| Fig. 3.28 | Measured Zin and modeled Zin. Ground plane size: 20mm × 25mm79                                   |

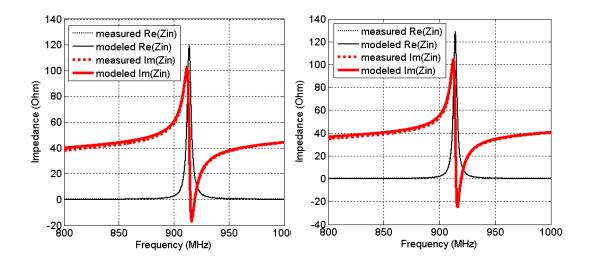

| Fig. 3.29 | Measured Zin and modeled Zin. Ground plane size: left: $60 \text{mm} \times 75 \text{mm}$ ;      |

|           | right: 76.2mm × 95.3mm80                                                                         |

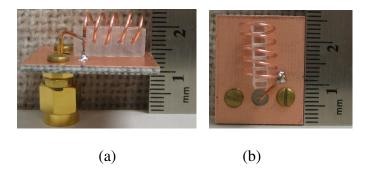

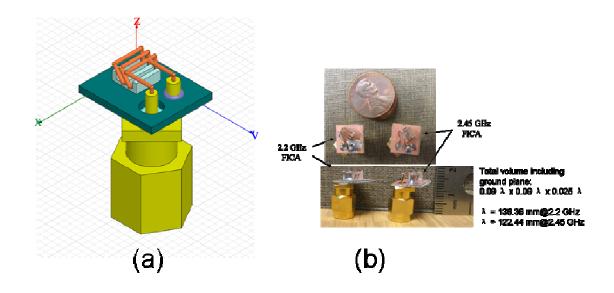

| Fig. 3.30 | Diagram (a) and photograph (b) of FICA at 2.2GHz and 2.45GHz81                                   |

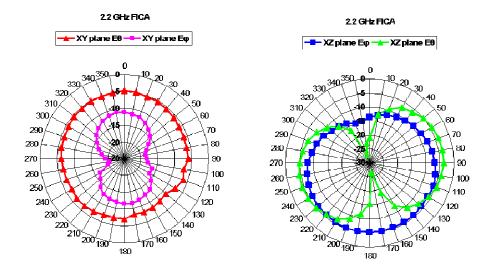

| Fig. 3.31 | Measured gain of a 2.2GHz FICA. Left: $E_{\phi}$ and $E_{\theta}$ on XY plane. Right: $E_{\phi}$ |

|           | and $E_{\theta}$ on XZ plane. Coordinates are defined in Fig. 3.19 and Fig. 3.30.82              |

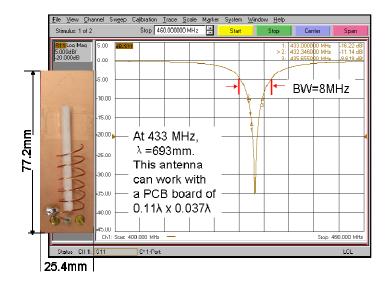

| Fig. 3.32 | Measured S11 of FICA scaled to 433MHz83                                                          |

| Fig. 4.1  | Design flow of low noise amplifier (LNA)90                                                       |

| Fig. 4.2  | (a) $g_m/I_D$ - IC plot for 0.13 $\mu$ m CMOS. (b) $V_{GS}$ - IC plot for 0.13 $\mu$ m           |

|           | CMOS93                                                                                           |

| Fig. 4.3  | Normalized $obj(V_{GS}, W)$ versus bias $V_{GS}(V)$ and transistor width $W(\mu m)$ . (a)         |

|-----------|---------------------------------------------------------------------------------------------------|

| T         | Analytical model (4.8 b). (b) Cadence simulation94                                                |

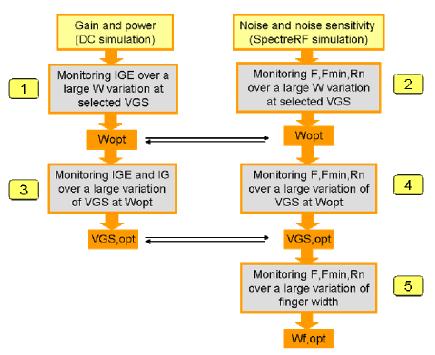

| Fig. 4.4  | Design flow for transistor biasing and sizing in Cadence simulation.                              |

|           | Intrinsic Gain Efficiency: $IGE = g_{ml}(g_{m2}r_{o1}r_{o2} + r_{o1} + r_{o2}) / I_D$ . Intrinsic |

| D: 4.5    | Gain: $IG = g_{ml}(g_{m2}r_{o1}r_{o2} + r_{o1} + r_{o2})$                                         |

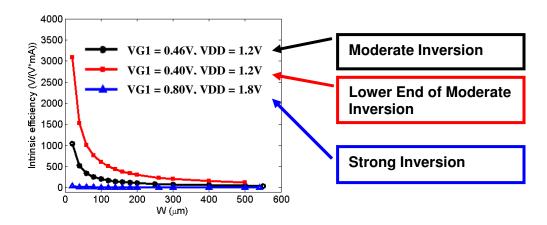

| Fig. 4.5  | Cascode transistor intrinsic gain efficiency vs W at different gate biasing                       |

| E' 4.6    | levels                                                                                            |

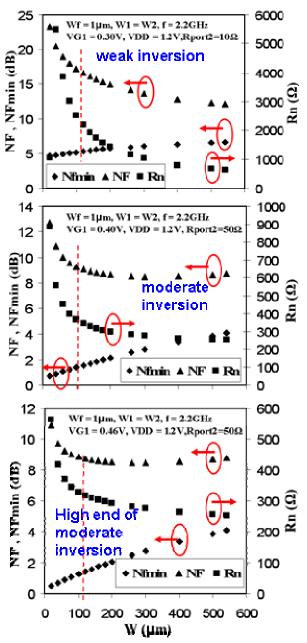

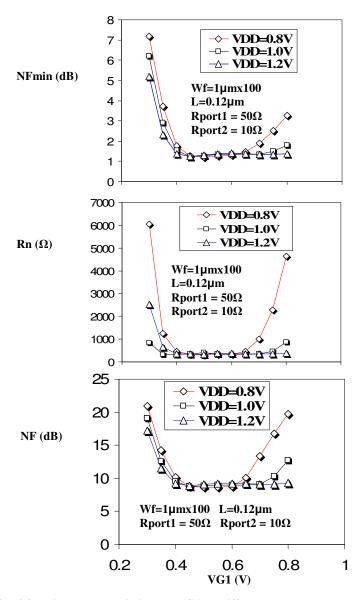

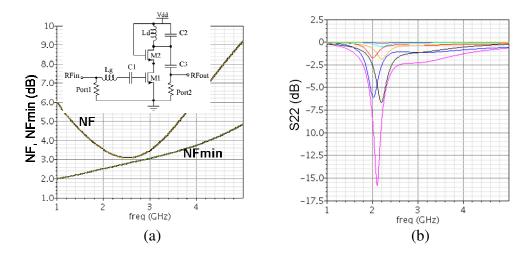

| Fig. 4.6  | NF, NFmin, and Rn vs. W for cascode transistors. Top: weak inversion                              |

|           | region. Middle: moderate inversion region. Bottom: moderate inversion                             |

| D: 4.7    | region with higher VG1                                                                            |

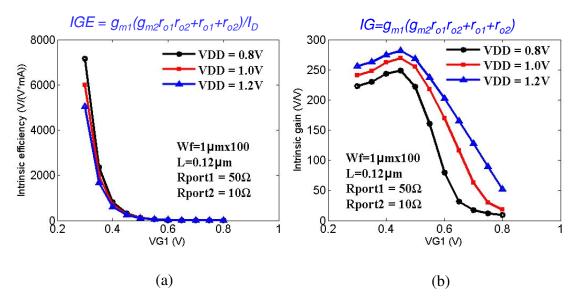

| Fig. 4.7  | (a) Intrinsic gain efficiency (IGE) and (b) intrinsic gain (IG) of cascode                        |

|           | transistors vs. VG1 at different supply voltage levels. Transistor sizes are                      |

| T' 40     | $W/L = 100/0.12 \mu m$                                                                            |

| Fig. 4.8  | Noise characteristics vs. VG1 at different supply voltage levels. Transistor                      |

|           | sizes are W/L = $100/0.12\mu m$ . Top: minimum achievable noise figure                            |

|           | NFmin. Middle: noise sensitivity factor Rn. Bottom: overall noise figure                          |

|           | NF                                                                                                |

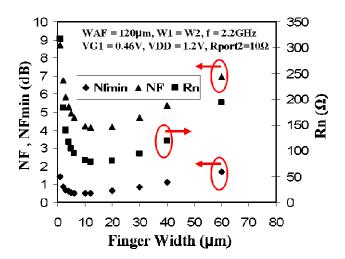

| Fig. 4.9  | NFmin, NF, and Rn vs. transistor finger width. Transistor sizes are W/L =                         |

|           | $120/0.12\mu m$ . Biasing condition is VG1 = 0.46V. Supply voltage is                             |

|           | 1.2V                                                                                              |

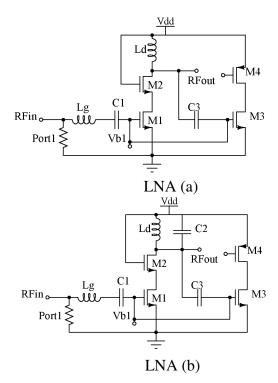

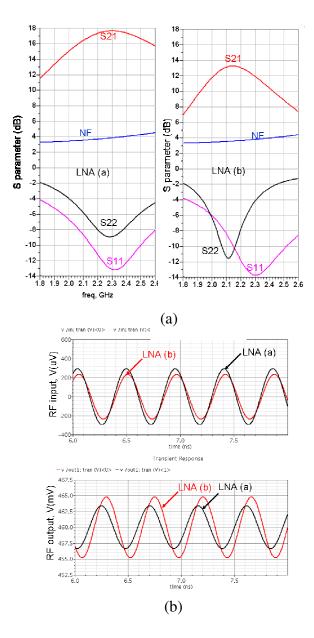

| Fig. 4.10 | LNA cascaded with common source stage and current source load. LNAs                               |

|           | (a): designed for maximum power gain, (b): for maximum voltage                                    |

|           | gain105                                                                                           |

| Fig. 4.11 | Simulated power gain and voltage gain of LNAs designed for high power                             |

|           | gain or high voltage gain. The difference of RF input in LNAs (a) and (b)                         |

|           | is because the RF input is the AC voltage from the gate of M1 to the                              |

|           | ground, not from port1 to ground. Due to the capacitive voltage                                   |

|           | amplification (section 4.4.1), these voltages differ slightly106                                  |

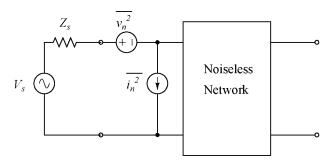

| Fig. 4.12 | Two-port network for noise analysis                                                               |

| Fig. 4.13 | (a) NF and NFmin for Rload = $10\Omega$ to $1M\Omega$ . Curves for different Rload                |

|           | values collapse into one NF and one NFmin plot. (b) S22(dB) for different                         |

|           | values of Rload. Since we only demonstrate the insensitivity of NF to                             |

|           | Rload, the particular Rload value for each curve in panel (b) is not                              |

|           | important, and these are not labeled due to space limitations110                                  |

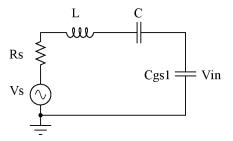

| Fig. 4.14 | LC series circuit for LNA input matching network111                                               |

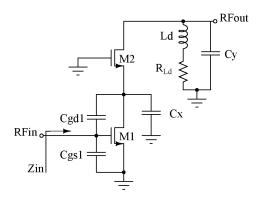

| Fig. 4.15 | Input impedance calculation for a Cascode LNA with LC tank load. Cx =                             |

|           | Cgb1 + Cgs2 + Cbs2, $Cy = Cgd2 + Cdb2 + CL$                                                       |

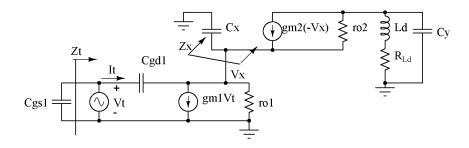

| Fig. 4.16 | Small signal model for cascode LNA114                                                             |

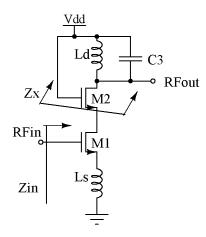

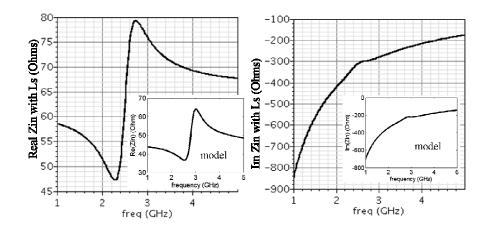

| Fig. 4.17 | Primary panels: Cadence simulation results for real and imaginary parts of                        |

|           | $Z_x$ in Fig. 4.16. Insets: Analytical model (4.23) of real and imaginary parts                   |

|           | of $Z_x$ in Fig. 4.16                                                                             |

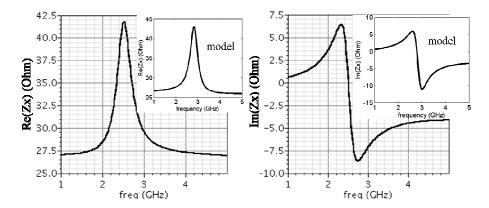

| Fig. 4.18 | Small signal circuit for input impedance calculation of cascode LNA115                            |

| Fig. 4.19 | Input impedance of cascode LNA with lossy LC resonance tank. Primary                              |

|           | panels: real and imaginary Zin from Cadence simulation. Insets: analytical                        |

|           | results according to (4.24)                                                                       |

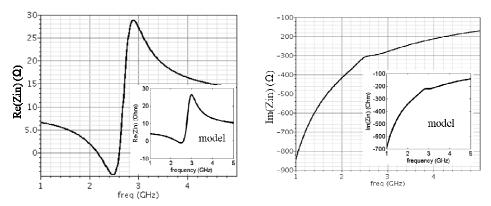

| Fig. 4.20 | Cascode LNA with source degeneration                                                              |

| Fig. 4.21          | Input impedance of Cascode LNA with Ls. Primary panels: real and                   |

|--------------------|------------------------------------------------------------------------------------|

|                    | imaginary parts of Zin from Cadence simulation. Insets: real and                   |

|                    | imaginary parts of Zin according to (4.28)120                                      |

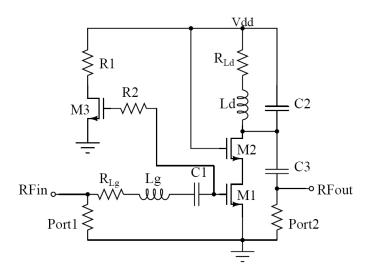

| Fig. 4.22          | Simplified 2.2GHz LNA schematic121                                                 |

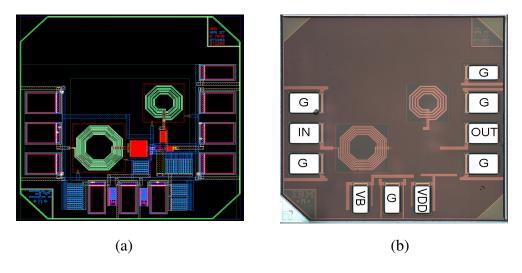

| Fig. 4.23          | Layout and die microphoto of 2.2GHz LNA using 0.13µm IBM8RFLM                      |

| _                  | technology122                                                                      |

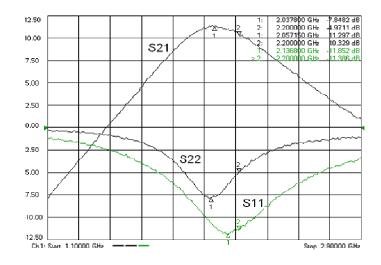

| Fig. 4.24          | Measured LNA S-parameters                                                          |

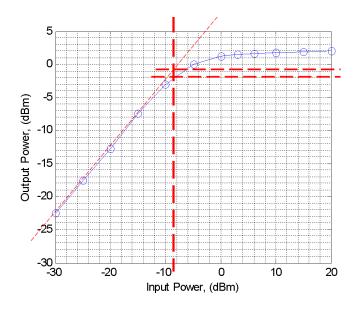

| Fig. 4.25          | Measured LNA P-1dB point                                                           |

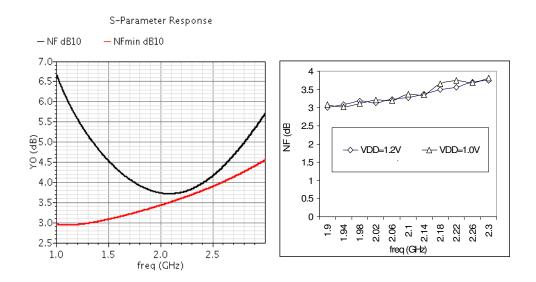

| Fig. 4.26          | (a) Simulated and (b) measured noise figure for the LNA123                         |

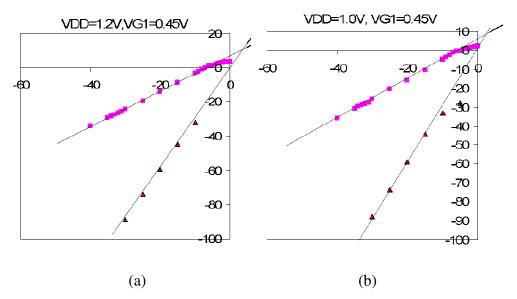

| Fig. 4.27          | IIP3 measurement for LNA biased at different levels. (a): VDD = 1.2V,              |

| C                  | IIP3 = 5dBm. (b): VDD = 1.0V, IIP3 = 3dBm                                          |

| Fig. 4.28          | FoM of LNA computed (a) using (4.29), (b) using (4.30)125                          |

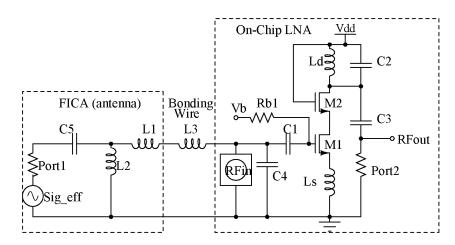

| Fig. 5.1           | Simplified cascode LNA topology128                                                 |

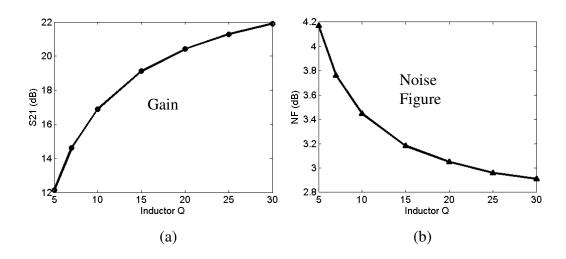

| Fig. 5.2           | Simulated (Cadence) gains and noise figures for a LNA with different               |

| C                  | inductor quality factors                                                           |

| Fig. 5.3           | FICA model for (a and b) transmitter, (c) receiver, and (d) observed               |

| <b>6</b> , -, -, - | results131                                                                         |

| Fig. 5.4           | Antenna and LNA co-design                                                          |

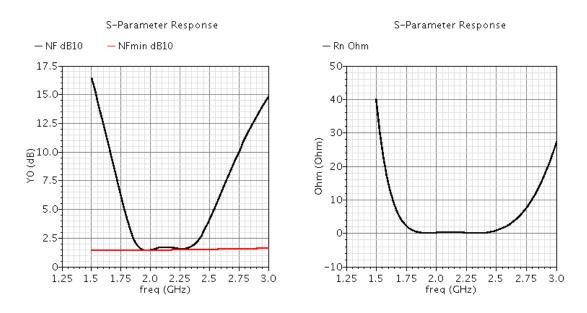

| Fig. 5.5           | Simulated antenna and LNA co-design result. Left: NF and NFmin. Right:             |

| υ                  | Rn                                                                                 |

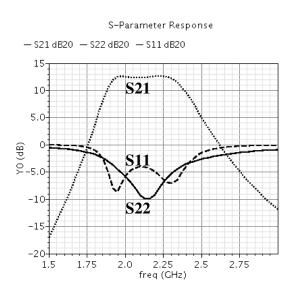

| Fig. 5.6           | Simulated S parameter for antenna and LNA co-design in Fig. 5.4. Dotted            |

| <b>6</b> , -, -, - | line: S21. Dashed line: S11. Solid line: S22                                       |

| Fig. 5.7           | FoM $(FoM = (Gain \cdot f) / (F - 1) / P_{dc})$ of LNAs. References in this figure |

| <b>6</b> , -, ,    | can be found in Table. 1.2                                                         |

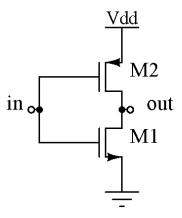

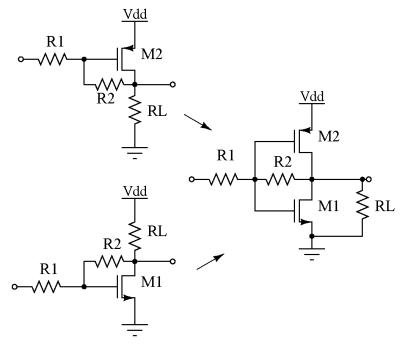

| Fig. 6.1           | Inverter amplifier using current reusing technique for higher gain and             |

| <i>6</i>           | lower power consumption                                                            |

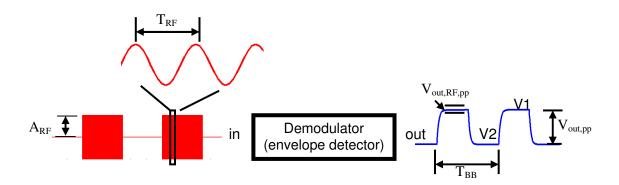

| Fig. 6.2           | Demodulations of envelope detector in a direct demodulation receiver               |

| 8                  | (DDR)                                                                              |

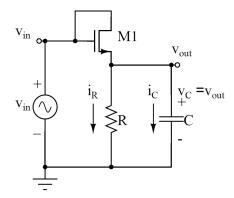

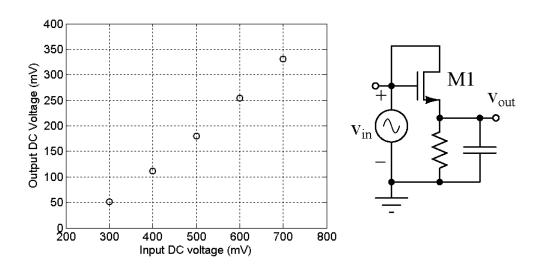

| Fig. 6.3           | Schematic of diode-connected NMOS envelope detector145                             |

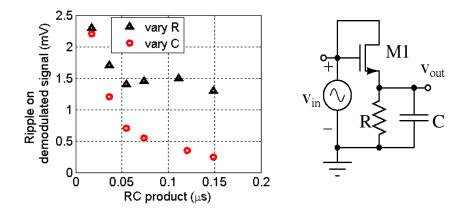

| Fig. 6.4           | Envelope detector output voltage ripple as a function of R and C146                |

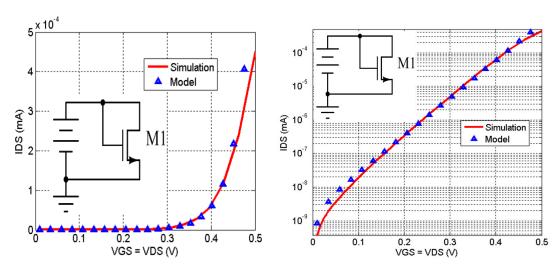

| Fig. 6.5           | I-V curve of diode-connected NFET in subthreshold region. Triangles:               |

| <b>6</b>           | Analytical model according to Eq.(6.7). Red solid line: Simulation results         |

|                    | from Cadence. Left: Linear coordinates. Right: Log coordinates148                  |

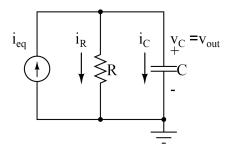

| Fig. 6.6           | Equivalent circuit of a peak detector149                                           |

| Fig. 6.7           | Vin and Vout plot of Eq. (6.10), solved by MATLAB151                               |

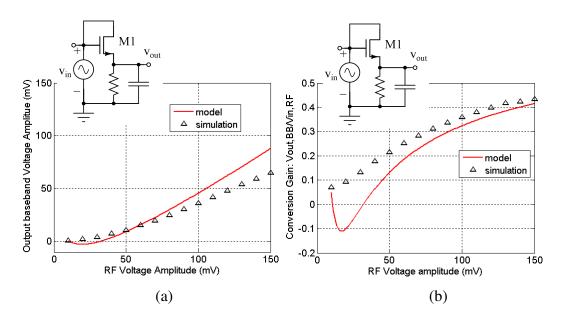

| Fig. 6.8           | Cadence simulation and analytical model of a diode-connected envelope              |

| <i>6</i>           | detector. (a) Output voltage of the envelope detector and (b) conversion           |

|                    | gain of the envelope detector                                                      |

| Fig. 6.9           | Simulated envelope detector performance without ripple remover154                  |

| Fig. 6.10          | Envelope detector with ripple removing low pass filter154                          |

| Fig. 6.11          | Simulated envelope detector performance with ripple remover155                     |

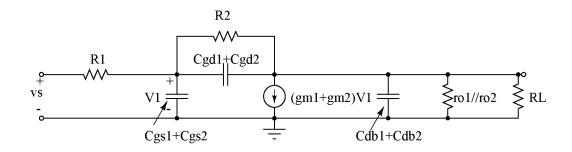

| Fig. 6.12          | Schematic of the auxiliary amplifier                                               |

| Fig. 6.13          | The current reusing technique employed in the feedback amplifier157                |

| Fig. 6.14          | Small signal model of one stage of the feedback amplifier157                       |

| Fig. 6.15          | DC output voltage of envelope detector vs. DC input voltage160                     |

| 5. 0.13            | 2 c carpar volumes of enverope detector volume in the compact volume.              |

| m 11                                                                        |              |

|-----------------------------------------------------------------------------|--------------|

| Table 6.4                                                                   | 161          |

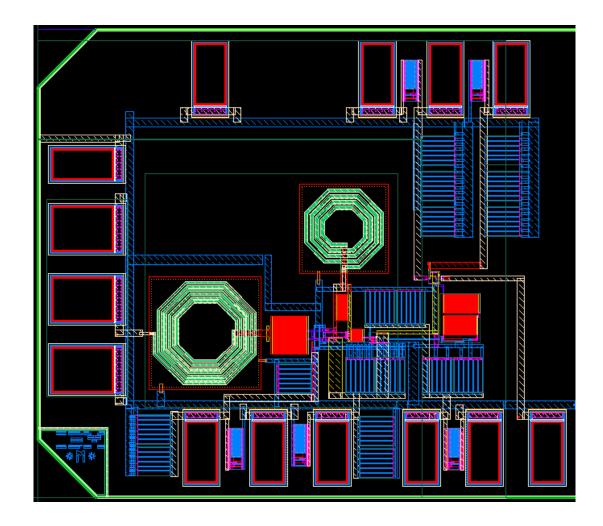

| Fig. 6.17 Layout of full OOK receiver using 0.13µm technology               | 163          |

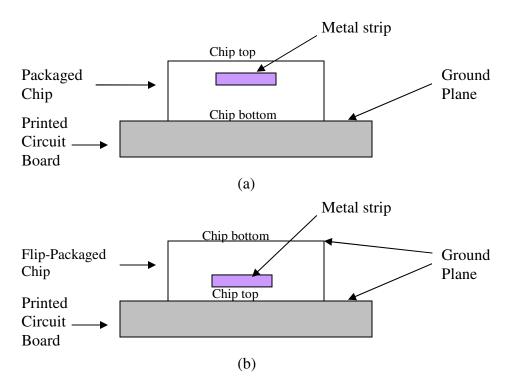

| Fig. 6.18 Cross sectional plots of (a) a microstrip line formed in normal   | packaging,   |

| and (b) a triplate line formed in flip-chip packaging                       | 165          |

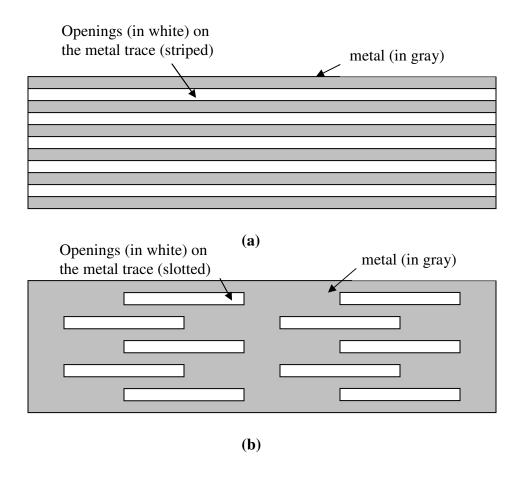

| Fig. 6.19 A wide metal strip being (a) striped and (b) slotted              | 170          |

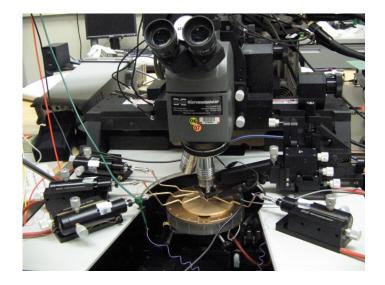

| Fig. 6.20 Receiver test bench                                               | 171          |

| Fig. 6.21 Microphoto of the receiver                                        | 171          |

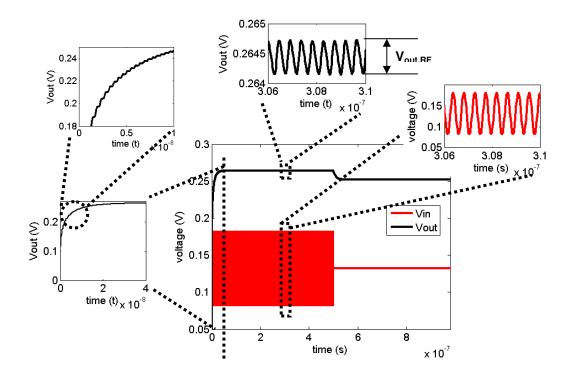

| Fig. 6.22 Transient testing results of receiver                             | 172          |

| Fig. 6.23 Full OOK transceiver system schematic                             | 174          |

| Fig. 6.24 Transmitter schematic of on-off-keying system, from [Zha09]       | and [Salter  |

| 09]                                                                         | 175          |

| Fig. 6.25 RF switch schematic for the OOK transceiver                       | 176          |

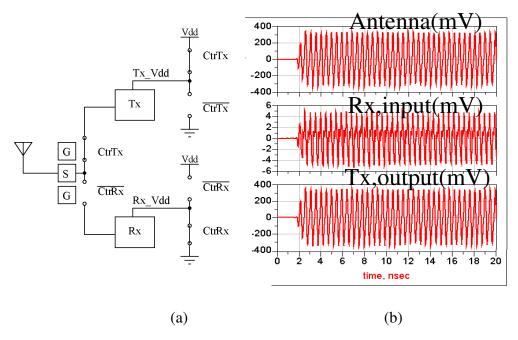

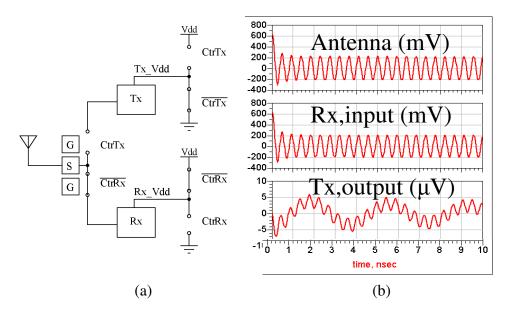

| Fig. 6.26 Simulated results for full transceiver system with transmitter on | 177          |

| Fig. 6.27 Simulated results for full transceiver system with receiver on    | 177          |

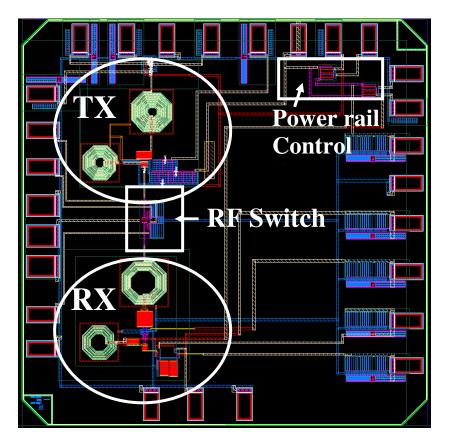

| Fig. 6.28 Layout of full low power OOK transceiver                          | 178          |

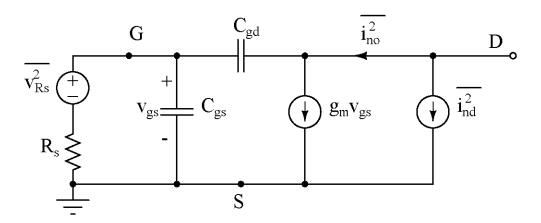

| Fig. A.1 The small circuit model for an intrinsic transistor including di   | rain current |

| noise                                                                       | 184          |

| Fig. B.1 The small signal circuit model for the optimum noise is            | impedance    |

| derivation                                                                  | 186          |

# Chapter 1 Introduction

#### 1.1 Motivation

In the past decade, research and applications on Wireless Sensor Networks (WSNs) have developed very rapidly. In WSNs, wires for short range communications are eliminated. A large number of wireless communication nodes are spread out over a selected area to form a communication sensing and control network. This technology has found application in a number of fields, such as the monitoring of building humidity, temperature, and light control, patient movement tracking, and data collection for hazard prevention. WSN radio units require low power, low cost, low profile electronic circuits, antennas, batteries, and sensors.

Smart Dust WSNs (SDWSN) are members of the WSN family. The unique constraint of SDWSN is the lower tolerance on radio size and power consumption. For example, WSN radios available on the market typically have a size on the order of 20 to 30cm<sup>3</sup>. Most often, two to four AA batteries are necessary to power each unit. However, in SDWSN, the target radio size is 1cm<sup>3</sup> or less. Reducing unit volume while maintaining performance is a very difficult and challenging task due to antenna size and radio power dissipation limitations. It is imperative to provide innovative solutions for efficient ultra small antennas and ultra low power receivers to

cope with these challenges in SDWSN. This dissertation advances new design techniques for small antennas and low power receivers. The resulting system has the potential to be used in ultra low profile, low power SDWSN and effectively satisfy the strict size and power requirements.

#### 1.2 Contributions

The original contributions of this dissertation are briefly listed below:

• Invention of ultra low profile, highly efficient 916MHz/2.2GHz/2.45GHz electrically small antennas.

Ultra small smart sensor network transceivers, such as in Smart Dust applications, have a total volume of less than one cubic centimeter, including the transceiver integrated circuit, battery, sensor, antenna, and ground plane. The millimeter or centimeter scale dimensions are often a small fraction of a quarter wavelength ( $\lambda$ ) at the operating frequency. This work introduces a novel low profile 916MHz F-inverted Compact Antenna (FICA) with a volume of  $0.024~\lambda \times 0.06\lambda \times 0.076\lambda$ , including the ground plane. The radiation efficiency is 48.53% and the peak gain is -1.38dBi. The antenna performance is summarized in Table.1.1, where its key attributes are provided and it is compared with other works. The designed antenna can be scaled to higher operating frequencies, such as the 2000 to 2500MHz bands, with comparable performance and volume reduction. This work is presented in detail in chapter 3.

Table 1.1 Antenna performance summary (NA=not available). 1

|              | [Choo05]                       | [Chen05]             | [Ojefors05]                    | This work<br>#1        | This work<br>#2              | This work #3                 |

|--------------|--------------------------------|----------------------|--------------------------------|------------------------|------------------------------|------------------------------|

| Type of ESA  | Genetic                        | PIFA                 | IFA                            | IFMLWA                 | FICA 1                       | FICA2                        |

|              | Algorithm                      |                      |                                | (section               | (section                     | (section                     |

|              |                                |                      |                                | 3.4.2.1)               | 3.4.2.2)                     | 3.4.2.3)                     |

| Ground plane | $0.11 \lambda \times$          | 0.2 λ×               | $0.176 \lambda \times$         | $0.08  \lambda \times$ | $0.06  \lambda \times$       | $0.06  \lambda \times$       |

| size         | 0.11 λ                         | 0.26 λ               | $0.208 \lambda$                | 0.12 λ                 | $0.076 \lambda$              | $0.076  \lambda$             |

| Antenna      | 0.11 λ                         | 0.026 λ              | 0.04 λ                         | 0.024 λ                | 0.021 λ                      | 0.024 λ                      |

| Height       |                                |                      |                                |                        |                              |                              |

| Antenna      | $1.3 \times 10^{-3} \lambda^3$ | $1.4 \times 10^{-3}$ | $1.7 \times 10^{-3} \lambda^3$ | 2.23×10 <sup>-4</sup>  | $1 \times 10^{-4} \lambda^3$ | $9 \times 10^{-5} \lambda^3$ |

| Volume       |                                | $\lambda^3$          |                                | $\lambda^3$            |                              |                              |

| Bandwidth    | 2.1%                           | 2.26%                | 8.3%                           | 4.4%                   | 1.6%                         | 2.45%                        |

|              | (-3dB)                         | (-10dB)              | (-10dB)                        | (-10dB)                | (-10dB)                      | (-3dB)                       |

| Gain (dBi)   | NA                             | 0.75                 | -0.7                           | NA                     | NA                           | -1.38                        |

| Efficiency   | 84%                            | NA                   | 52%                            | NA                     | NA                           | 48.53%                       |

| Operating    |                                |                      |                                |                        |                              |                              |

| frequency    | 394                            | 1946                 | 2400                           | 916                    | 916                          | 916                          |

| (MHz)        |                                |                      |                                |                        |                              |                              |

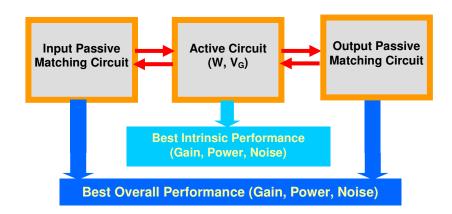

# Proposal of algorithmic optimization guidelines for low noise amplifier design.

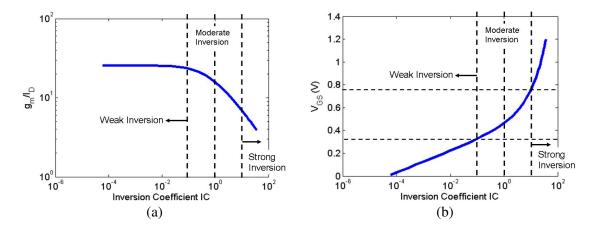

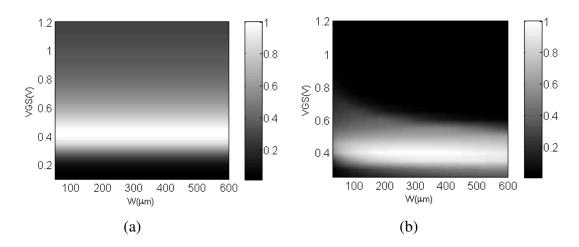

This work presents a novel low power cascode low noise amplifier (LNA) optimization method. This procedure includes active device and input/output passive matching network optimization. A new performance function  $g_m/I_DF$  is used when optimizing active devices, where  $g_m$  is the transconductance that is related to gain,  $I_D$  is the drain current of transistors that is related to power consumption, and F is the noise factor of the transistors. Managing this performance function helps to achieve optimized design. It is demonstrated through an analytical model and by simulation tools that  $g_m/I_DF$  reaches its maximum value in the moderate inversion region. Passive matching networks

<sup>&</sup>lt;sup>1</sup> [Choo05] does not provide gain, and [Chen05] does not provide efficiency. Therefore, there are NA entries in this table. For IFMLWA (Inverted-F Meander Line Wire Antenna, section 3.4.2.1) and FICA(F-inverted Compact Antenna, section 3.4.2.2 and 3.4.2.3), we did not have the opportunity to measure the gain and efficiency. Therefore, these numbers are absent from Table 1.1.

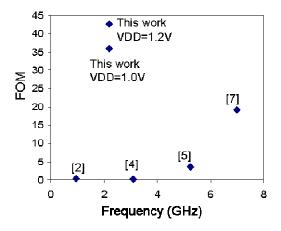

are designed for maximum voltage gain, which can be used directly to evaluate the overall receiver signal to noise ratio. Using the proposed optimization technique, a power efficient high voltage gain cascode LNA has been designed and fabricated in a 0.13µm CMOS standard digital process without the need of high quality factor inductors. This LNA has a noise figure of 3.6dB, a voltage gain of 24dB, an IIP3 (input third intercept point) of 3dBm, and power consumption of 1.5mW with 1.0V supply voltage. The Figure of Merit (FoM, defined in equation (1.1)) of this LNA is compared to other designs in Fig. 1.1 to illustrate its superior performance.

$$FoM_{LNA} = \frac{Gain \cdot IIP3 \cdot f}{(F-1) \cdot P_{dc}}$$

(1.1)

In the above equation, Gain is the voltage gain; f is the operation frequency; F is the noise factor;  $P_{dc}$  is the quiescent power consumption; IIP3 is the input third intercept point.

Details of this method and the LNA circuit are discussed in chapter 4.

Fig. 1.1 FoM of LNAs. References in this figure can be found in Table. 1.2.

Table 1.2 Literature results shown in Fig. 1.1 and Fig. 1.2.

|                               | Notes           | Freq. | Gain  | Pdc   | IIP3  | F-1   |

|-------------------------------|-----------------|-------|-------|-------|-------|-------|

|                               |                 | (GHz) | (V/V) | (mW)  | (mW)  |       |

| [1]                           | [Gatta01]       | 0.93  | 7.5   | 21.6  |       | 0.603 |

| [2]                           | [Wang,JSSC06]   | 0.96  | 4.5   | 0.72  | 0.095 | 1.5   |

| [3]                           | [Mou,TCASII05]  | 2.4   | 17.8  | 15    |       | 0.9   |

| [4]                           | [Bevilacqua 04] | 3.1   | 2.9   | 9     | 0.21  | 1.5   |

| [5]                           | [Nguyen,MTT05]  | 5.25  | 10.6  | 12    | 0.32  | 0.41  |

| [6]                           | [Kim03]         | 5.8   | 6.68  | 7.2   |       | 1.24  |

| [7]                           | [Fujimoto02]    | 7     | 2.78  | 13.8  | 6.9   | 0.51  |

| This work 1                   | Vdd = 1.2 V     | 2.2   | 17.8  | 2.544 | 3.16  | 1.14  |

| This work 2                   | Vdd = 1.0 V     | 2.2   | 15.8  | 1.5   | 2     | 1.29  |

| This work (codesign, Chap. 5) | Vdd = 1.2 V     | 2.2   | 18.0  | 2.0   |       | 0.413 |

<sup>--:</sup> Not provided in the referred publication.

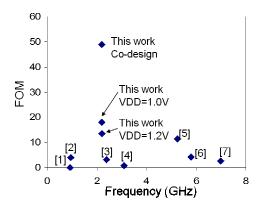

## • Creation of an antenna and front-end radio co-design methodology.

The noise figure and impedance matching strongly affect the receiver sensitivity. The typical quality factor of a spiral on-chip inductor is around 5 to 10, which is a limiting factor to improvements in the noise figure and sensitivity. This work introduces a new design methodology for antenna and low noise amplifier co-design, which utilizes the high Q inductors of the antenna as part of the input matching network of the LNA. Designs adapting this new method are shown to have a lower noise figure and better sensitivity. In addition, the noise sensitivity factor is also low, which enables circuits to function properly across process variations. The Figure of Merit ( $FoM2 = (Gain • f)/(F - 1)/P_{dc}$ ) of this co-designed LNA is shown in Fig. 1.2. As Fig. 1.2 shows, the antenna and LNA co-design approach further improves the

performance of the LNAs over those that do not use the co-design method.

This co-design method is presented in detail in chapter 5.

Fig. 1.2 FoM2 ( $FoM2 = (Gain \bullet f) / (F - 1) / P_{dc}$ ) of LNAs. References in this figure can be found in Table. 1.2.

# Design of a low power 2.2 GHz on-off keying receiver for Smart Dust Wireless Sensor Networks.

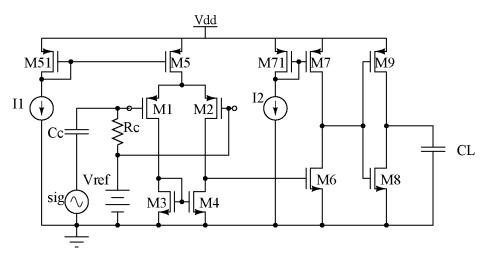

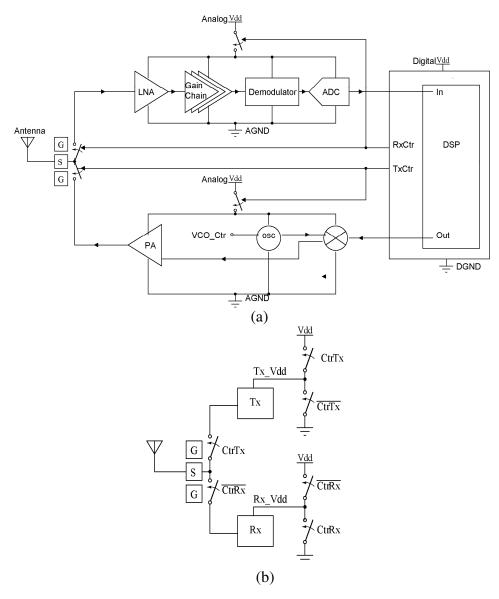

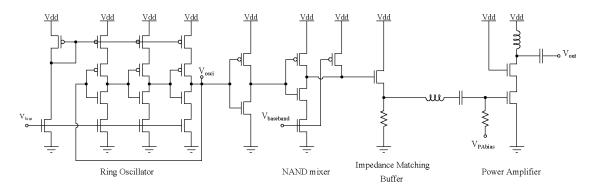

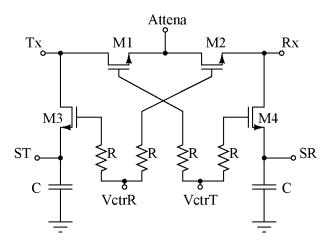

A low power receiver is critical to ensure endurance of transceiver nodes over a long time span. The power consumption of analog/RF front-end circuits is typically several orders of magnitude higher than that of digital circuits. Chapter 6 presents a complete ultra low power, low cost, low form factor receiver for SDWSN. This system uses the novel Direct Demodulation Receiver architecture introduced in chapter 2. The Direct Demodulation Receiver has a low noise amplifier, an auxiliary amplifier, a demodulation block, and a one channel analog-digital converter. Different low power integrated circuit design techniques have been applied in each of these design blocks. The demodulator is a critical block in the receiver. To exemplify this

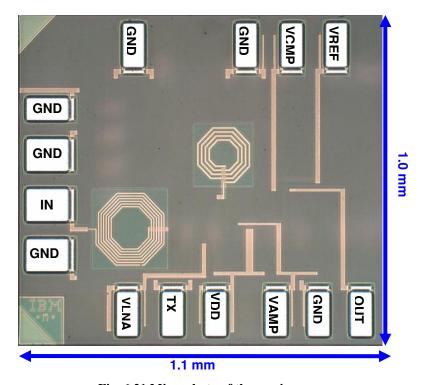

point, this work develops its behavior model and conversion gain. The receiver is fabricated using a  $0.13\mu m$  CMOS technology. With a 1.2V power supply, this receiver has a sensitivity of -58dBm, a data rate of 10kbps-2Mbps, a chip area of  $1.0mm \times 1.1mm$ , and power consumption of 2.85mW. The performance of this receiver and comparison with other works are summarized in Table 1.3. Details of this receiver and a low power transceiver system design for SDWSN are discussed in chapter 6.

Table 1.3 Summary of receiver performance.

| Features                | [Morici09] | [Retz09]        | [Hafez07]       | This work |

|-------------------------|------------|-----------------|-----------------|-----------|

| Technology              | 90nm       | 0.18µm          | 0.13µm          | 0.13µm    |

|                         |            | RFCMOS          |                 | Digital   |

|                         |            |                 |                 | CMOS      |

| Availability of high Q  | None       | Yes             | None            | None      |

| inductor in this        |            |                 |                 |           |

| technology (determines  |            |                 |                 |           |

| the cost)               |            |                 |                 |           |

| External component      | None       | None            | None            | None      |

| Supply Voltage (V)      | 1.2        | 1.8~3.6         | 1.2             | 1.2       |

| Power Consumption       | 3.6        | 12.6~25.2       | 7.2             | 2.85      |

| (mW)                    |            | (receiver only) |                 |           |

|                         |            | 30.24~60.48     |                 |           |

|                         |            | (full receiver) |                 |           |

| Data Rate (kbps)        |            |                 |                 | 10 ~ 2000 |

| Carrier Frequency (GHz) | 2.45       | 2.4             | 2.45            | 2.2       |

| Die Area (mm2)          | 0.12       | 5.9             |                 | 1.1       |

| Sensitivity (dBm)       |            | -96             | -97 (simulated) | -58       |

<sup>--:</sup> Not provided in the referred publication.

## 1.3 Thesis Structure

This thesis is organized as follows. Chapter 2 introduces the design challenges for the Smart Dust Wireless Sensor Network antenna and circuitry. Performance criteria are derived in this chapter. The unique, ultra low profile, highly efficient, electrically small antenna is presented in chapter 3. A novel low noise amplifier

design and its optimization guidelines are proposed in chapter 4. The new antenna and low noise amplifier co-design methodology is introduced in chapter 5. The design of a low power 2.2GHz on-off keying receiver suitable for SDWSN is discussed in chapter 6. Chapter 7 concludes this thesis and suggests future work.

# Chapter 2 Design Philosophy for Smart Dust Wireless Sensor Networks (SDWSN)

This chapter explores the design philosophy and the state of art of Smart Dust Wireless Sensor Networks (SDWSN). Low cost, low power, and low volume requirements are the main hardware design challenges in SDWSN. This chapter discusses the design trade-offs in detail and proposes a Direct Demodulation Receiver (DDR) architecture as the low power receiver design most suitable for SDWSN. The performance requirements for each block are briefly studied in this chapter. The design details for the blocks are discussed in later chapters in this thesis.

This chapter is organized as follows. Section 2.1 introduces Smart Dust Wireless Sensor Networks and their requirements. Section 2.2 discusses the design challenges of SDWSN. Section 2.3 discusses some SDWSN design trade-offs. Section 2.4 reviews the state of art, and proposes a Direct Demodulation Receiver (DDR) for SDWSNs. Section 2.5 presents the gain, the design criteria, and provides budget calculations for this DDR. Section 2.6 summarizes this chapter.

## 2.1 Smart Dust Wireless Sensor Networks (SDWSN)

# 2.1.1 The Concepts of WSN and SDWSN

A Wireless Sensor Network, or WSN, is a low power multi-hop wireless communication network composed of energy sources (i.e., batteries), sensors, antennas, RF transceivers, micro controllers, and user interfaces. Many WSNs follow the IEEE 802.15.4 standard (proposed in the mid 2000's) [IEEE standard], which is a fairly new standard in the IEEE 802.15 group. It features a low data rate, long battery life, and low complexity communication. Table 2.1 is a summary of the IEEE standards for wireless personal area networks(WPAN). To achieve optimal performance for the WSN, multiple tradeoffs have to be made between power consumption, communication protocols, and wireless communications.

Table 2.1 Wireless personal area network (WPAN) IEEE standards.

|             | 802.15.1          | 802.15.3                                                                              | 802.15.4                                                    |

|-------------|-------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|

|             | (Bluetooth)       | (High Rate)                                                                           | (Low Rate)                                                  |

| Application | Bluetooth         | portable imaging and multimedia                                                       | ZigBee                                                      |

| Band        | 2.4GHz            | 2.4GHz                                                                                | 868MHz, 915MHz,<br>2.4GHz                                   |

| Data Rate   | 1Mbps             | 11, 22, 33, 44, 55Mbps.                                                               | 20, 40, 250kbps                                             |

| Comm. Range | 100m              | 1~10m                                                                                 | 1~10m                                                       |

| Mod/Demod   | GFSK <sup>1</sup> | QPSK <sup>2</sup> , DQPSK <sup>3</sup> , 16-<br>QAM <sup>4</sup> , 32-QAM, 64-<br>QAM | BPSK <sup>5</sup> , PSSS <sup>6</sup> , O-QPSK <sup>7</sup> |

GFSK<sup>1</sup>: Gaussian Frequency Shift Keying OPSK<sup>2</sup>: Quadrature Phase Shift Keying

DQPSK<sup>3</sup>: Differential Quadrature Phase Shift Keying

QAM<sup>4</sup>: Quadrature Amplitude Modulation

BPSK<sup>5</sup>: Binary Phase Shift Keying

PSSS<sup>6</sup>: Parallel Sequence Spread Spectrum Keying O-QPSK<sup>7</sup>: Offset Quadrature Phase Shift Keying

The concept of "Smart Dust" was conceived in 1991 [Cook06]. "Smart Dust" is a member of the WSN family, with strict requirements on radio size and power consumption; the system does not need to follow existing communication standards. Each wireless sensor node, or "mote", is assumed to have a compact volume in the range of cubic millimeters to centimeters (the size of grains of "smart dust" at the low end), which contains one or more sensors, computation units, power supplies, and communication blocks [Cook06]. When used in large numbers, the "motes" form an autonomous wireless sensor network: the motes sense the environment and communicate with each other over short distances (typically around 10m) using multiple hops. Such intelligent wireless sensor networks can be used in managing large inventories, monitoring product quality, monitoring environmental conditions for crop growth, monitoring patients in hospitals, building virtual keyboards, and in many other application [Warneke01].

# **2.1.2 Smart Dust Requirements**

With devices continuously scaling down in size, low power, low cost, high device density, high speed digital and radio frequency analog circuits are becoming available [Abidi04]. In addition, technology advances in MEMS (Microelectromehanical systems), energy scavenging, and long lasting batteries have made wireless sensor motes a reality instead of science fiction.

Various research groups have made progress in designing and fabricating "Smart Dust" hardware over the last decade. Pioneering works include the "Smart Dust" project led by Dr. Pister and Dr. Kahn at University of California, Berkeley

[Kahn99], the "PicoRadio" project led by Dr. Rabaey at University of California, Berkeley [Rabaey02, 06], and the "WiseNET" project led by Dr. Vittoz at the Swiss Center for Electronics and Microtechnology Inc (CSEM) [Porret01]. Commonly accepted SDWSN features realized by these works are (but are not limited to):

- Low power consumption: The average power consumption is  $100\mu W$  for up to one year. The on-state power consumption goal is 2mW. Duty cycles are on the order of 1%.

- Low form factor: around 1cm<sup>3</sup> in volume and unobtrusive to the environment.

- Low cost: less than US \$1 for each mote.

- Low communication range: 1 to 10m.

- Low data rates: bit rate is on the order of kbps.

- BER (Bit Error Rate): less than 10<sup>-4</sup>.

- Transmitted power: less than 1mW.

- Packet lengths: between 20 bits for the control packets to 200 bits for typical data packets, with a maximum packet length of 500 bits.

- Noise Figure: around 20dB.

## 2.2 Design Challenges

Among the above requirements, achieving low power, low cost, and low form factor are the major objectives and challenges in the SDWSN transceiver front-end circuit design. In this section, we explain the importance of these three design endeavors. In the next section, we discuss the design trade-offs.

#### 2.2.1 Low Power

A SDWSN requires that each "mote" in the network function properly from one to ten years. It is very costly and not advisable to change batteries on each of the large number of "motes" during their lifetimes. The circuitry power is determined by the power density and the size of the energy source. Available energy sources currently include Lithium (non-rechargeable or chargeable), Alkaline, NiMH, Zinc-Air batteries, solar cells, and energy scavenging devices. For a 1cm<sup>3</sup> volume Smart Dust node, the average power consumption provided by a Lithium battery is around  $100\mu W/cm^3 \times 1~cm^3 = 100\mu W$ , if the battery lifetime is up to 1 year [Rabaey02]. This extremely low power supply level seriously challenges the SDWSN transceiver design, because the available power supply is directly related to the signal strength, noise level, sensitivity, communication distance, carrier frequencies, etc.

## **2.2.2** Low Cost

Deploying a large number of Smart Dust nodes in WSNs is feasible only if the cost of each node is trivial. In order to minimize this cost, the unit hardware demands a very high level of integration. For example, receiver architectures free of bulky external filters, such as Direct Conversion Receivers (DCR), are preferable to heterodyne receivers. The latter typically have high quality factor (Q) Surface Acoustic Wave (SAW) filters that are very difficult to achieve with on-chip devices, requiring additional fabrication and assembly costs. In addition, RF, analog, and digital circuits should be consolidated into a single die to increase the level of integration. The die area should also be minimized to reduce cost.

Present market available WSN hardware, such as TelosB [Crossbow]<sup>2</sup>, have not quite achieved the 1 US\$ cost goal. It is urgent to break this cost barrier to make affordable hardware for SDWSN applications.

### 2.2.3 Low Form Factor

As already discussed, to deploy a large scale SDWSN and reduce the cost, maximal integration and minimum chip area are necessary. In addition to the cost related to the low form factor requirement, Smart Dust motes used in some scenarios, such as security surveillance, monitoring, or defense applications, need to be inconspicuous. A total node volume (including sensor, antenna, battery, circuitry, etc.) of 1cm<sup>3</sup> or less is appropriate. Accordingly, the area of the chip package should be about 1cm<sup>2</sup>.

# 2.3 Design Trade-Offs

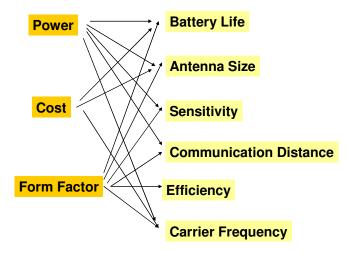

The tradeoffs between SDWSN hardware power, cost, form factor constraints, and performance are shown in Fig. 2.1.

\_

<sup>&</sup>lt;sup>2</sup> TelosB uses TI, CC2420 as its radio.

Fig. 2.1 SDWSN design tradeoffs.

To reduce cost, die area must be minimized. With 0.13µm technology, capacitors up to a few tens of pF and inductors of between a few hundreds of pH to a few nH are feasible on a chip. Due to design rule limitations and electromagnetic (EM) noise coupling, inductors cannot be arranged in a compact fashion. Multiple inductors must be arranged far enough from other components to minimize harmful EM coupling. It is essential to limit the total number of inductors and to use only small value inductors and capacitors. However, with small inductors and capacitors, transceivers can only work at high frequencies. This negatively affects receiver sensitivity and power consumption, as explained below.

It is well known that for CMOS transistors, the minimum intrinsic noise factor  $F_{min}$  is proportional to the ratio of the operating frequency  $\omega$  to the unity gain frequency  $\omega_T(2.1)$  [Lee03].

$$F_{\min} = 1 + \frac{2}{\sqrt{5}} \frac{\omega}{\omega_T} \sqrt{\gamma \delta (1 - c^2)} \qquad (2.1)$$

Terms in the square root above are constants that will be explained in detail in chapter 4. The intrinsic noise factor of transistors increases with operating frequency. To achieve reasonably low noise figures at higher frequencies,  $\omega_T = g_m/C_{gs}$  needs to be large.  $g_m$  is the transconductance, which is proportional to power consumption.  $C_{gs}$  is the gate source parasitic capacitance. Therefore, more power is needed to have same receiver noise level at higher operating frequencies.

In addition, receivers at higher frequencies radiate and receive less power. We can define the effective aperture of receiving antenna as  $A_e \equiv G\lambda^2/4\pi$ , where G is the antenna gain and  $\lambda$  is the wavelength [Stutzman98]. Consider two half wavelength dipole antennas A and B, with  $\lambda_A = 0.5\lambda_B$ ; the operating frequency of A is twice that of B. Since the gain of half wavelength dipoles is constant regardless of the operating frequency:

$$A_{e,A} = 1/4 A_{e,B} (2.2)$$

If A and B are exposed to the same incident time-average power density  $P_{av}$ , then the received power levels  $P_{r,A}$  and  $P_{r,B}$  of antennas A and B, respectively, are

$$P_{r,A} = A_{e,A}P_{av} = 1/4A_{e,B}P_{av} = 1/4P_{r,B}.$$

(2.3)

To retrieve the signal over the same communication distance, we can either increase the receiver sensitivity by 6dB, or quadruple the transmitted power. Either way, higher power consumption is required.

Considering frequency, power, cost, and performance trade-offs, the bands used for Smart Dust are 902 to 928MHz in North America, and 2.4 to 2.485GHz through most of the world (Japan, China, Europe, etc.). Due to noise and interference in the very crowded 2.4GHz band (Bluetooth and ZigBee are in this band), this work

studies and designs SDWSN receivers at 2.2GHz. It is easy to transfer the design to the 2.4GHz band. Form factors at this frequency may reach the 1cm<sup>3</sup> goal with some effort (chapter 3). This choice of band does not violate Federal Communications Commission (FCC) regulations at 2.2GHz, because the radiated signal strength is very low (less than 1 mW), and the communication distance is short (less than 10 meters). In particular, "the FCC has reserved the 2110-2150MHz and 2160-2200MHz bands for future emerging technologies on a co-primary basis with fixed services" [NTAIA97].

To successfully design a SDWSN that balances requirements among power consumption, cost, form factor, sensitivity, communication distance, operating frequency, antenna size, efficiency, etc., we next review the state of the art and present a proposed architecture.

### 2.4 State of the Art

Since the emergence of WSN, many research groups have made substantial progress in designing SDWSN units over the last decade [Kahn99] [Rabaey02,06] [Porret01]. This section reviews the state of the art in SDWSN receivers, focusing on low power, low cost, and low form factor.

## 2.4.1 Direct Conversion Receiver

Traditionally, heterodyne architecture has been widely used in high-performance receivers. However, as discussed in section 2.2, highly selective filters must be used for both the image rejection filter and the intermediate frequency (IF) filter, which requires bulky external components, such as SAW filters. These high Q

filters inevitably increase both form factor and cost, and are not practical for integration with on-chip CMOS technologies. Direct conversion receiver (DCR) architectures (also called zero-IF or homodyne) are adopted by designers for WSN applications, because they are free of bulky high performance filters [Abidi95] [Razavi97].

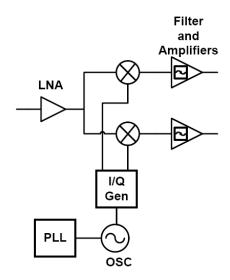

Fig. 2.2 shows a block diagram of a DCR, where the RF input is in-phase/quadrature (I/Q) mixed with its own frequency. The output has zero-intermediate frequency (IF). The image is the signal itself. Therefore, both the image rejection filter and the low IF filter are eliminated. All subsequent baseband processing is performed at very low frequency due to the zero-IF scheme. This is suitable for low power, low form factor applications. In addition, this architecture can be applied to any demodulation scheme with I/Q signals. DCRs have been widely used in WSNs [Darabi00] [Porret01] [Jarvinen05] [Nguyen06].

Fig. 2.2 Block diagram of a direct conversion receiver.

However, DCR requires many circuit blocks, such as phase locked loops (PLLs), oscillators, mixers, etc., which increase power consumption and circuit complexity. For example, the 915MHz receiver front-end circuit for the ZigBee standard reported in [Nguyen06] consumes 3.6mW alone, excluding the power consumption of PLLs and voltage controlled oscillators (VCOs). If this power were considered, the communication node would be well above the 1-2mW power budget.

In addition to more power consumptions, in order to achieve accurate frequency control, a DCR often needs an external crystal oscillator, which reduces the receiver integration level. Furthermore, additional techniques (i.e., digital calibration) need to be applied to solve well-known DCR problems, such as (1) DC offset, (2) even-order distortion, (3) flicker noise, (4) I/Q mismatch, and (5) local oscillator (LO) leakage, which degrade signal the noise ratio (SNR) of the receiver if left untreated. To solve these problems without adding additional circuits, low IF receivers can be used.

#### 2.4.2 Low IF Receiver

If we change the down converted signal from zero-IF to a low-IF, the DC offset problem in the DCR is eliminated. Although a low-IF receiver reintroduces the image problem, the image rejection requirement is much relaxed. This type of low-IF receiver is often a choice for low power WSN applications [Kluge06] [Choi03][Sheng03].

Fig. 2.3 is the block diagram of a low IF receiver. The incoming signal is first amplified by a LNA, and then down-converted to a low IF signal through I/Q mixers.

This low IF signal is then demodulated after channel selection filters and limiting amplifiers. The choice of IF involves many tradeoffs: If the IF is too low, 1/f noise becomes important, which reduces the signal to noise ratio. In addition, PLL locking time is longer if an integer-N frequency synthesizer PLL is used. If the IF is too high, then the circuit blocks after the mixers, such as channel selection filters, need to be high Q and consume more power. Low-IF architecture has comparable complexity to DCR, and consumes about the same amount of power as DCR.

Fig. 2.3 Block diagram of low-IF receiver.

#### 2.4.3 Super-Regenerative Receiver

To further decrease the power consumption level and form factor, simpler receiver architectures with fewer circuit blocks should be considered. One of these simple, low power receivers is the super-regenerative receiver, which was invented by Armstrong in 1922 [Lee03]. The super-regenerative receiver is essentially an oscillator that is turned off periodically by a "quench" signal to remove the saturation effect. This very low power and highly efficient super-regenerative receiver was revisited recently in [Otis05]. An example of a highly integrated super-regenerative

OOK receiver for WSN applications is presented in [Otis05], and its block diagram is in Fig. 2.4.

Fig. 2.4 Block diagram of super-regenerative receiver [Otis05].

In the super-regenerative receiver, an isolation amplifier provides matching to the antenna. It also isolates the oscillator and the antenna to prevent the signal from being re-transmitted from the oscillator in receiving mode. The detector oscillator samples the RF input as its initial condition. In OOK demodulation, by periodically applying the quenching to the oscillator, the oscillator will be activated when seeing sampling bit-1, and deactivated when reading sampling bit-0. The oscillation envelope is detected by a nonlinear filter. A pulse width demodulator then removes the oscillator sampling tone, leaving a raw OOK signal for an OOK detector.

Due to the minimum number of active components and very simple architecture, this OOK consumes only  $400\mu W$ , and has a sensitivity of -100.5dBm at 5kbps for BER =  $10^{-3}$ . However, in this circuit, the free running frequency of the oscillator is set by a bulk acoustic wave (BAW) resonator, which is not common in standard CMOS technologies, and increases fabrication and assembling costs. For this

reason, we do not consider this architecture in the SDWSN CMOS receiver design in this work.

Nevertheless, the concept of "going back to fundamental simple receiver architectures" has motivated us to propose a direct demodulation receiver architecture, which is described in the next section.

### 2.4.4 Proposed Receiver Architecture: Direct Demodulation Receiver (DDR)

Since a SDWSN uses low data throughput, we can pick up receiver architectures and modulation/demodulation schemes that are suitable for low data rates. WSN IEEE Standards employ BPSK, O-QPSK, GPSK, etc. as modulation/demodulation methods for low data rate applications (Table 2.1), but do not specify methods for SDWSNs. In fact, frequency shift keying (FSK), binary frequency shift keying (BFSK), amplitude shift keying (ASK), and on-off keying (OOK) may all be good candidates for SDWSN.

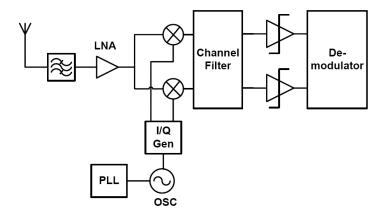

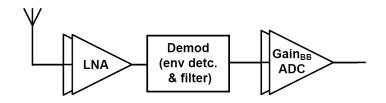

ASK is commonly used in broadcast radios and television audio. Due to its susceptibility to noise and need of a highly linear power amplifier (PA), ASK is not used in today's wireless systems. However, a simple ASK modulation/demodulation method, the on-off keying (OOK) method was used in this SDWSN project, since there is only one channel in this network. In OOK systems, PA linearity is not important. We propose a direct demodulation receiver (DDR) for this OOK modulation/demodulation method. The block diagram of this OOK receiver is shown in Fig. 2.5. It has only 3 function blocks: input gain stage, demodulation stage, and output gain stage.

Fig. 2.5 Block diagram of direct demodulation receiver (DDR) for OOK.

For an OOK transceiver, power is cycled to turn on the transmitter when sending bit-1, and turn it off when sending bit-0. To retrieve the signal, a straightforward way is to apply an envelope detector or amplitude detector in the demodulation block. A DDR should amplify the received RF signal to a level that can be processed by the envelope/amplitude detector. This may require additional amplifying stages after the LNA. After filtering, shaping, and further amplifying of the demodulated signal, the digital stream is ready to be processed by baseband digital circuits.

The proposed receiver architecture is simple and requires very few circuit components while demanding no external parts except for an antenna. It is therefore suitable for low power, highly integrated applications, such as SDWSNs.

## 2.5 Receiver Design Goals

For very small input signals, the receiver needs to meet certain gain and noise specifications to function properly. This section studies first the receiver sensitivity requirements. Then, it estimates the gain and noise budget for each block of the SDWSN DDR.

## 2.5.1 Sensitivity Requirements

Receiver sensitivity is the minimum detectable signal over a bandwidth, which is defined as [Razavi97]:

$$P_{Min,Sig} \mid_{dBm} = P_{Source} \mid_{dBm/Hz} + 10\log BW + NF \mid_{dB} + SNR_{out} \mid_{dB}$$

(2.4)

$P_{Min,Sig}$  is the minimum detectable signal in dBm.  $P_{Source}|_{dBm/Hz}$ =-174dBm/Hz is a constant, which is the source resistance noise power per unit bandwidth. BW is bandwidth in Hertz.  $SNR_{out}$  is is the signal to noise ratio measured at the output of the receiver. The minimum  $SNR_{out}$  is determined by the required Bit Error Rate (BER). For OOK with  $BER = 10^{-4}$ ,  $SNR_{out} = 16dB$ . NF is the noise figure of the receiver, which is the ratio of the total equivalent noise power at the input to the noise power of the source resistance (in dB). Ideally, if the system is noise free, then NF is 0dB. In reality, NF is often much larger than 0dB. For WSN, the achievable NF is around 20dB according to [Porret01]. Eqn. (2.4) tells us that over a unity bandwidth, the minimum detectable signal of the receiver must be higher than the thermal noise level of the system by at least the sum  $NF \mid_{dB} + SNR_{out} \mid_{dB}$ . For receivers with larger noise factors and requiring higher  $SNR_{out}$ ,  $P_{Min,Sig}$  is larger. Weaker incoming signals cannot be detected.

The power available at the input of a receiver in free space is defined in (2.5) [Kraus88]:

$$P_r = P_t \frac{G_t G_r \lambda^2}{(4\pi d)^2} \tag{2.5}$$

In (2.5)  $G_r$  and  $G_t$  are the receiving and transmitting antenna gains.  $P_r$  and  $P_t$  are received and transmitted power.  $\lambda$  is the wavelength of the transmitter and the

receiver. *d* is the distance between them. As it will be seen in chapter 3, low profile antennas designed for this work have a gain of -1.38dBi. The wavelength at 2.2GHz is 0.1364m.

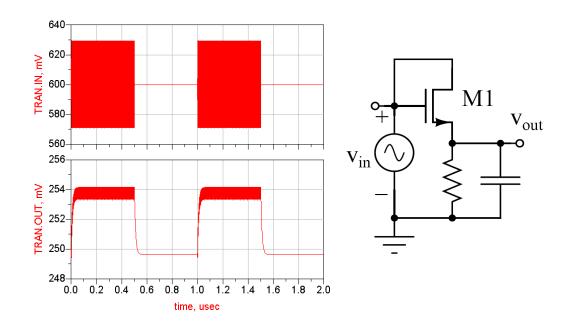

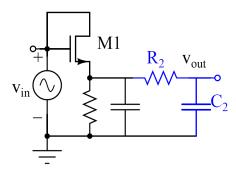

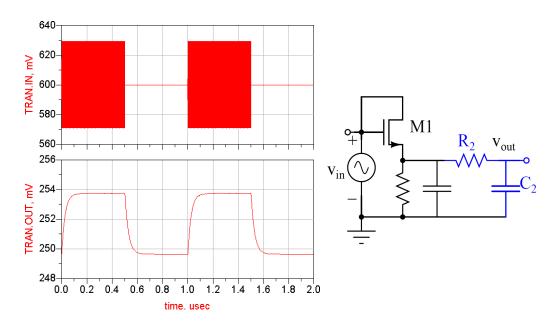

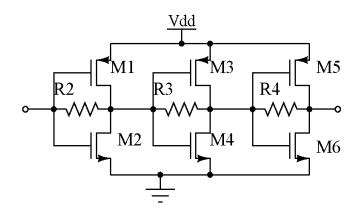

For non-ideal communication environments, such as an indoor environment, an additional attenuation factor is introduced to (2.5) [Rappaport96]. Eqn (2.5) becomes