#### ABSTRACT

Title of dissertation: ENHANCING POWER EFFICIENT DESIGN

TECHNIQUES IN DEEP SUBMICRON ERA

Junjun Gu, Doctor of Philosophy, 2011

Dissertation directed by: Professor Gang Qu

Department of Electrical and Computer Engineering

Excessive power dissipation has been one of the major bottlenecks for design and manufacture in the past couple of decades. Power efficient design has become more and more challenging when technology scales down to the deep submicron era that features the dominance of leakage, the manufacture variation, the on-chip temperature variation and higher reliability requirements, among others. Most of the computer aided design (CAD) tools and algorithms currently used in industry were developed in the pre deep submicron era and did not consider the new features explicitly and adequately.

Recent research advances in deep submicron design, such as the mechanisms of leakage, the source and characterization of manufacture variation, the cause and models of on-chip temperature variation, provide us the opportunity to incorporate these important issues in power efficient design. We explore this opportunity in this dissertation by demonstrating that significant power reduction can be achieved with only minor modification to the existing CAD tools and algorithms.

First, we consider peak current, which has become critical for circuit's reliabil-

ity in deep submicron design. Traditional low power design techniques focus on the reduction of average power. We propose to reduce peak current while keeping the overhead on average power as small as possible. Second, dual  $V_t$  technique and gate sizing have been used simultaneously for leakage savings. However, this approach becomes less effective in deep submicron design. We propose to use the newly developed process-induced mechanical stress to enhance its performance. Finally, in deep submicron design, the impact of on-chip temperature variation on leakage and performance becomes more and more significant. We propose a temperature-aware dual  $V_t$  approach to alleviate hot spots and achieve further leakage reduction. We also consider this leakage-temperature dependency in the dynamic voltage scaling approach and discover that a commonly accepted result is incorrect for the current technology.

We conduct extensive experiments with popular design benchmarks, using the latest industry CAD tools and design libraries. The results show that our proposed enhancements are promising in power saving and are practical to solve the low power design challenges in deep submicron era.

# ENHANCING POWER EFFICIENT DESIGN TECHNIQUES IN DEEP SUBMICRON ERA

by

## Junjun Gu

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2011

Advisory Committee:

Professor Gang Qu, Chair/Advisor

Professor Manoj Franklin

Professor Kazuo Nakajima

Professor Martin Peckerar

Professor Lourdes G. Salamanca-Riba

© Copyright by Junjun Gu 2011

## Dedication

To my parents and friends

#### Acknowledgments

First and foremost I'd like to thank my advisor, Professor Gang Qu for guiding me into a qualified researcher and influencing me into a nicer person. As an advisor, he is both strict to push for a more solid work, and liberal to allow student's self-innovation. As a collaborator, he teaches me how to better communicate with partners and always recognize other people's efforts. He also makes me realize that a patient listener and a timely offer of help is what constitutes a good friend, as what he is to me. I will always cherish my four-year experience with him, which I believe will impact me life long.

I would like to thank Professor Kazuo Nakajima, with whom I took three courses with, and Professor Martin Peckerar for serving on my proposal committee and giving me valuable comments for my work. I would also like to thank Professor Manoj Franklin and Professor Lourdes G. Salamanca-Riba for agreeing to serve on my thesis committee and spending their time reviewing my manuscript.

I would like to thank Dr. Lin Yuan, a former student of Professor Gang Qu. I've worked with him on several projects and those are very pleasant collaboration. He introduces practical problems from industrial perspective and gets me more familiar with standard industry flow and simulation tools. I enjoy lots of inspiring discussions with him. I would also like to thank Dr. Yi-Min Jiang, my supervisor when I was doing my summer intern. Through the interactive meetings with him during the three months, I was able to apply my parallel computing knowledge learned from graduate seminar and speed up the core engine of their tool. He also

encouraged me to take the initiative to resort others for help instead of struggling with everything by myself.

My PhD years would not have been so memorable without my friends. Jing Wu, previously my labmate for over one year, is someone I can always trust and talk to. Besides, she is such a lovely person to enjoy off-work time with. We went to the gym together, ate together and hung out together. I will always remember the happy moments with her. Sangkyo Han, my former labmate, is also a fun person. We enjoyed Chinese buffet or Korean BBQ together from time to time. I also respect his optimism about difficulties and life.

I would also like to acknowledge help and supports from Ms. Tracy Chung, Ms. Melanie Prange, Ms. Maria Hoo and Ms. Vivian Lu and the staff members at ECE Help Desk. Their professional technical supports have made my work efficient and smooth.

At last, I owe my deepest thanks to my parents who have always stood by me and guided me through my career. I am really proud to have such great parents.

## Table of Contents

| Lis | st of ' | Tables  |                                                            | vii  |

|-----|---------|---------|------------------------------------------------------------|------|

| Lis | st of 1 | Figures |                                                            | viii |

| Lis | st of . | Abbrev  | riations                                                   | ix   |

| 1   | Intro   | oductio | on                                                         | 1    |

|     | 1.1     | Challe  | enges in Deep Submicron Era                                | . 2  |

|     | 1.2     | Existi  | ng Work on Power Efficient Design                          | . 4  |

|     | 1.3     |         | Challenges and Opportunities for Power Efficient Design    |      |

|     | 1.4     | Key C   | Contributions                                              | . 9  |

| 2   | Prel    | iminary | V                                                          | 15   |

|     | 2.1     |         | Fundamentals                                               |      |

|     | 2.2     |         | Efficient Design Techniques for CMOS Circuits              |      |

|     |         | 2.2.1   | Dynamic power minimization                                 |      |

|     |         | 2.2.2   | Leakage power minimization                                 |      |

|     | 2.3     | Summ    | nary                                                       |      |

| 3   | Fini    | te Stat | e Machine Synthesis Technique for Peak Current Reduction   | 24   |

|     | 3.1     |         | ed Works                                                   |      |

|     | 3.2     | Prelin  | ninaries                                                   | . 30 |

|     |         | 3.2.1   | Finite State Machine Synthesis                             | . 30 |

|     |         | 3.2.2   | Peak Current Reduction by Re-Encoding                      |      |

|     |         | 3.2.3   | FSM Re-Engineering for Low Power                           | . 33 |

|     | 3.3     | Two I   | Basic Techniques for peak current reduction                |      |

|     |         | 3.3.1   | State Re-Encoding                                          | . 35 |

|     |         | 3.3.2   | State Replication                                          | . 37 |

|     | 3.4     | Simul   | taneous State Replication and Re-Encoding                  | . 39 |

|     |         | 3.4.1   | Overview of the Approach                                   |      |

|     |         | 3.4.2   | Initial Construction of $S$ and $SP$                       | . 41 |

|     |         | 3.4.3   | The Most Constrained Transition and the Least Constraining |      |

|     |         |         | Solution                                                   |      |

|     |         | 3.4.4   | Update $S$ and $SP$                                        |      |

|     | 3.5     |         | rative Example for SSRR                                    |      |

|     |         | 3.5.1   | Initial Construction of $S$ and $SP$                       |      |

|     |         | 3.5.2   | The First Iteration                                        |      |

|     |         | 3.5.3   | The Second Iteration                                       |      |

|     | 0.0     | 3.5.4   | Result Evaluation                                          |      |

|     | 3.6     | -       | rimental Results                                           |      |

|     | 3.7     | Sumn    | nary                                                       | . 56 |

| 4  | Imp    | roving Dual $V_t$ Technology by Simultaneous Gate Sizing and Mechanical |     |  |

|----|--------|-------------------------------------------------------------------------|-----|--|

|    | Stre   | ss Optimization                                                         | 58  |  |

|    | 4.1    | Preliminaries                                                           | 61  |  |

|    |        | 4.1.1 Power Consumption in CMOS Circuits                                | 62  |  |

|    |        | 4.1.2 Delay Model                                                       | 62  |  |

|    |        | 4.1.3 Gate Sizing, Dual $V_t$ and Mechanical stress Techniques          | 63  |  |

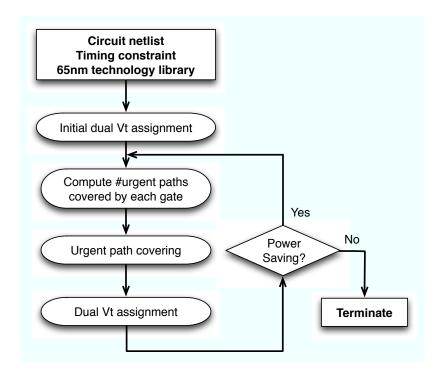

|    | 4.2    | Urgent Path Guided Power Optimization                                   | 68  |  |

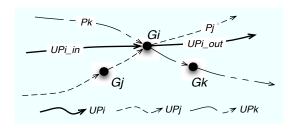

|    |        | 4.2.1 Compute number of urgent paths each gate covers                   | 70  |  |

|    |        | 4.2.2 Urgent path covering                                              | 74  |  |

|    | 4.3    | Experimental Results                                                    | 76  |  |

|    | 4.4    | Summary                                                                 | 81  |  |

| 5  | Enh    | ancing Dual- $V_t$ Design by Considering On-Chip Temperature Variation  | 85  |  |

|    | 5.1    | Challenges of Temperature-Aware Dual- $V_t$ Design                      | 87  |  |

|    | 5.2    | Related Work                                                            | 90  |  |

|    | 5.3    | Leakage and Temperature Models                                          | 92  |  |

|    |        | 5.3.1 Leakage and Power Model                                           | 92  |  |

|    |        | 5.3.2 Temperature Model                                                 | 93  |  |

|    | 5.4    | Temperature-Aware Dual- $V_t$ Design                                    | 95  |  |

|    |        | 11                                                                      |     |  |

|    |        | 5.4.2 Terminologies                                                     |     |  |

|    |        | 5.4.3 Raise $V_t$ in Hot Regions                                        |     |  |

|    |        | 5.4.4 Reduce $V_t$ for Timing Closure                                   |     |  |

|    |        | 5.4.5 Update of Steady-State Temperature and Iteration of Procedure 1   |     |  |

|    | 5.5    | Experimental Results                                                    |     |  |

|    | 5.6    | Summary                                                                 | 105 |  |

| 6  |        | ancing DVS Technique for Real-Time Systems by Incorporating Temperate   |     |  |

|    |        |                                                                         | 106 |  |

|    | 6.1    | Modeling Temperature-Leakage Interdependency                            |     |  |

|    |        | 6.1.1 Existing Models                                                   |     |  |

|    |        | 6.1.2 The Proposed Model                                                |     |  |

|    | 6.2    | DVS Scheduling for Total Energy Minimization                            |     |  |

|    |        | 6.2.1 Current DVS Approaches                                            |     |  |

|    |        | 6.2.2 Optimal Solution for A Single Task                                |     |  |

|    |        | 6.2.3 Online DVS Heuristic for Multiple Tasks                           |     |  |

|    | 6.3    | Experimental Results                                                    |     |  |

|    | 6.4    | Summary                                                                 | 127 |  |

| 7  | Con    | onclusion and Future Works 12                                           |     |  |

| A  | List   | of publications                                                         | 132 |  |

| Bi | bliogi | raphy                                                                   | 134 |  |

## List of Tables

| 3.1 | Comparison between $POW3$ encoding and state register re-encoding [70] for circuit $ex5_n$                                                      | . 33  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.2 | Initial Working Set and Solution Pool for FSM in Fig. 3.5                                                                                       |       |

| 3.3 | S and $SP$ at the end of the first iteration                                                                                                    |       |

| 3.4 | Comparison of different encoding techniques on the 39 circuits that $PSV$ has not reached minimal by $POW3$                                     |       |

| 4.1 | Comparison of input pin capacitances for different inverters                                                                                    | . 64  |

| 4.2 | Comparison of leakage power for different inverters                                                                                             | . 64  |

| 4.3 | Comparison of gate delay for different inverters                                                                                                | . 64  |

| 4.4 | Drive current improvement and leakage power increase via mechanical                                                                             |       |

|     | stress                                                                                                                                          | . 67  |

| 4.5 | Number of cells for each benchmark circuit after synthesis                                                                                      | . 77  |

| 4.6 | Power consumption comparison among dual $V_t$ only (D), dual $V_t$ com-                                                                         |       |

|     | bined with gate sizing (D+S), combined dual $V_t$ and gate sizing fur-                                                                          |       |

|     | ther incorporating mechanical stress (D+S+Str)                                                                                                  | . 82  |

| 4.7 | Power consumption comparison between approaches with and with-                                                                                  |       |

|     | out the guidance of urgent paths                                                                                                                | . 83  |

| 4.8 | Power consumption comparison between sensitivity-based approach                                                                                 |       |

|     | and urgent path guided approach                                                                                                                 | . 84  |

| 5.1 | Comparison in power consumption between the levelization-based dual- $V_t$ assignment algorithm and our temperature-aware enhancement technique | . 103 |

| 5.2 | Comparison in cell temperature between the levelization-based dual-                                                                             | . 100 |

| 0.2 | $V_t$ assignment algorithm and our temperature-aware enhancement                                                                                |       |

|     | technique                                                                                                                                       | . 103 |

| 6.1 | Thermal parameters for a single core processor                                                                                                  | . 123 |

| 6.2 | Mean absolute error over sufficient sampling points                                                                                             |       |

| 6.3 | Randomly generated task sets                                                                                                                    |       |

| 6.4 | Comparison of total energy consumption                                                                                                          | . 126 |

| 6.5 | Impact of different initial temperatures                                                                                                        | . 126 |

## List of Figures

| 2.1        | Leakage power in deep submicron technology node                                                                                            | 16       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

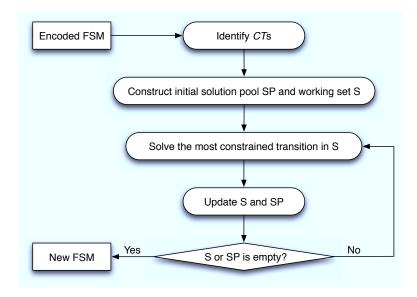

| 3.1<br>3.2 | State replication applied on circuit $ex5$ Overview of the simultaneous state replication and re-encoding ap-                              | 34       |

| 2.2        | proach                                                                                                                                     | 40       |

| 3.3        | Solving the most constrained CT with the least constraining solution.                                                                      | 44       |

| 3.4        | Update code information                                                                                                                    | 47       |

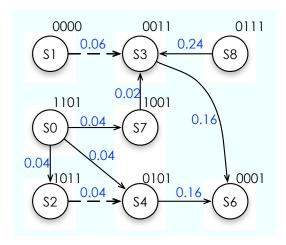

| 3.5        | Part of a 14-state FSM already encoded                                                                                                     | 48<br>51 |

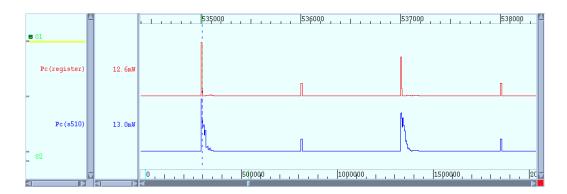

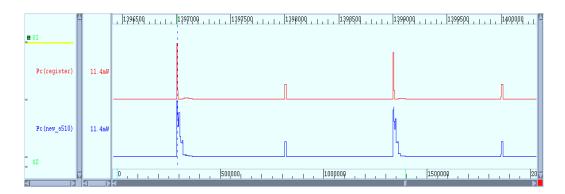

| 3.6<br>3.7 | Power waveform in circuit s510 encoded by $POW3$ and $SR$                                                                                  | 53       |

| 3.8        | Power waveform in circuit s510 encoded by $SSRR$                                                                                           | 54       |

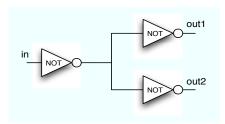

| 4.1<br>4.2 | One inverter fans out to two inverters                                                                                                     | 65       |

|            | ical stress                                                                                                                                | 69       |

| 4.3        | One gate covers the urgent paths of the other two gates                                                                                    | 72       |

| 4.4        | Compute #urgent paths each gate covers by forward and backward                                                                             |          |

| , _        | traveral                                                                                                                                   | 73       |

| 4.5        | Update #urgent paths each gate covers                                                                                                      | 75       |

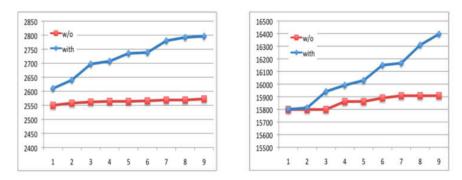

| 4.6        | Number of high $V_t$ cells in des3 and pci_bridge32                                                                                        | 80       |

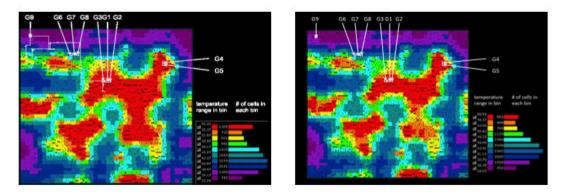

| 5.1        | Temperature profile of the AES design using the dual- $V_t$ algorithm proposed in [111] (left) and after our temperature-aware enhancement |          |

|            | approach (right).                                                                                                                          | 88       |

| 5.2        | Nine cells extracted from AES design using the dual- $V_t$ algorithm proposed in [111]                                                     | 88       |

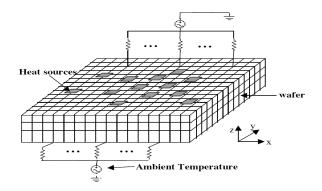

| 5.3        | 3-D mesh model for heat conduction on chip [96]                                                                                            | 94       |

| 5.4        | Selecting an MIS of low $V_t$ cells from the hot region                                                                                    | 99       |

| 5.5        |                                                                                                                                            | 100      |

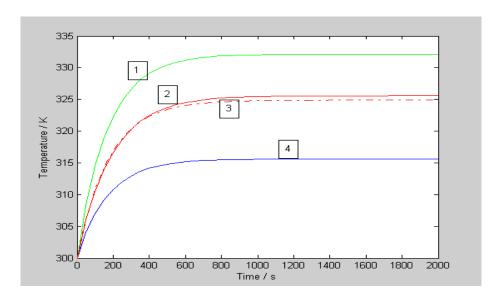

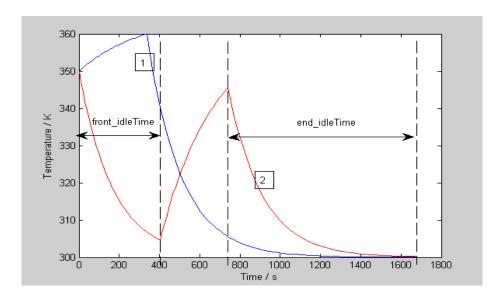

| 6.1        | Temperature predicted by using different power models                                                                                      | 107      |

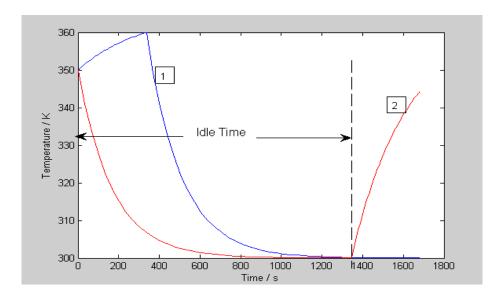

| 6.2        | Temperature curve of traditional DVS (curve 1) and optimal DVS for a single task (curve 2)                                                 |          |

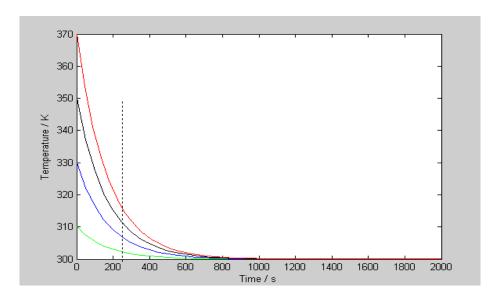

| 6.3        | Temperature behavior during sleep mode under different starting                                                                            |          |

|            | temperatures                                                                                                                               |          |

| 6.4        | Online DVS scheduler for energy minimization.                                                                                              | 120      |

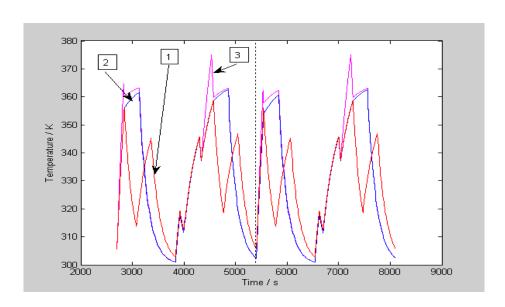

| 6.5        | Temperature curve of traditional DVS (curve 1) and optimal DVS                                                                             | 100      |

| 66         | based on proposed policy for multiple tasks (curve 2)                                                                                      |          |

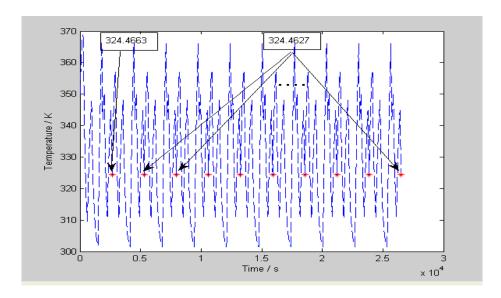

| 6.6<br>6.7 | Ending temperature of each period under TDVS                                                                                               |          |

| 0.1        | Transient temperature eurves                                                                                                               | 140      |

#### List of Abbreviations

IC Integrated Circuit

EDA Electronic Design Automation

DFM Design For Manufacturability

DVS Dynamic Voltage Scaling

SCE Short Channel Effect

DIBL Drain-Induced Barrier Lowering

CMOS Complementary metal-oxide-semiconductor

MTCMOS Multithreshold-voltage CMOS VTCMOS Variable Threshold CMOS DTMOS Dynamic Threshold CMOS

DGDT-MOS Double-gate Dynamic Threshold SOI CMOS

DVS Dynamic Voltage Scaling

SRAM Static Random Access Memory DPM Dynamic Power Management

FSM Finite State Machine TSV through-silicon-via

TTSV Thermal-through-silicon-via

MFC micro-fluidic channel

### Chapter 1

#### Introduction

Over the past several decades, the continuous downsizing of transistors and related frabrication processes have been the key driving force for the blooming of semiconductor and integrated circuit (IC) industry. The number of transistors integrated on a single die roughly doubles in every 18 months, enabling the implementation of much faster and more sophisticated systems that permeate daily life, from portable computing devices and wireless communication systems to high-end products used in scientific computing and large data centers.

However, the delivery of advanced silicon solutions has to rely on the availability of electronic design automation (EDA), design technologies, as well as effective verification methodologies at all levels of abstraction [1]. With semiconductor industry entering deep submicron era, many challenges are imposed on EDA and IC design community. This thesis focuses on the challenges related to power and energy efficiency. Specifically, we investigate how to enhance several state-of-the-art power efficient design techniques so that further power/energy savings can be achieved and other critical issues can be alleviated at the same time. The keyword in this statement is to "enhance". That is, we are not developing new techniques. Instead, we will incorporate new requirements and information in the deep submicron design to improve the performance of existing power optimization techniques without

introducing major changes to these EDA tools.

#### 1.1 Challenges in Deep Submicron Era

The design challenges in deep submicron domain can be generally classified as follows [2]:

- Signal Integrity: The much higher operating frequency along with the scaling and integration of mixed-signal and RF components bring ever larger noise and interference to the circuit signals. Emerging issues include noise headroom, large numbers of capacitively and inductively coupled interconnects, supply voltage IR drop and ground bounce and substrate coupling. These issues may cause false switching, delay variation or timing failures [6, 7].

- Power Management: High power densities worsen the thermal impact on circuit performance and reliability, while decreasing supply voltages worsen noise margin and leakage current. Under 45nm technology and beyond, leakage power starts to dominate dynamic power. As a result, the focus of research and EDA tool development has shifted to the reduction of leakage and total power consumption, particularly subthreshold leakage.

- Reliability and Resilience: Due to the much lower supply voltage, the gate oxide thickness has to be reduced to maintain circuit performance. However, with the continuous scaling, gate oxide breakdown is expected to arise. In addition, the much higher direct current densities in deep submicrometer design can lead to Joule heating and electromigration effect. Other issues such

as single-event upset can also become a serious reliability concern. Evidently, automatic insertion of robustness into design is becoming a new trend.

- Manufacturing Variability: Advanced ICs with high functionality, low power consumption and extreme reliability are pushing the manufacturing process to the limit. Slight manufacturing variations can significantly affect performance and yield. Interconnecting manufacturing-related disciplines with design process can provide a possible solution. A popular research topic known as design for manufacturability (DFM) has emerged.

- Design Productivity: To avoid the exponential increase of design complexity and thus design cost, design productivity has to be improved with technology scaling. The implied needs for design productivity reside in verification, embedded software design, and automated methods for analog/mixed-signal design and test. For instance, design verification is one of the major bottlenecks in the design process. One current practice, the partial verification process provides only a small fraction of coverage. A potential breakthrough relies on the shift from such ad hoc verification method to more structured and formal processes.

Each of the design challenges demands substantial research efforts. This thesis focuses on the challenge of power management. In the remaining of this chapter, we first review the state-of-the-art power efficient design techniques. Next we explore the new challenges and opportunities facing low power design in deep submicron domain. Finally we conclude with the overview of the thesis and the key contribu-

tions.

### 1.2 Existing Work on Power Efficient Design

In this section, we briefly describe the most relevant work on power efficient design. Detailed survey of the current state-of-the-art power efficient design methodologies can be found in Chapter 2.

Extensive researches on power efficient design have been performed at all design levels. To reduce dynamic power, various dynamic power management techniques [33] such as clock gating and dynamic voltage scaling can be applied at system level. Clock gating uses a hierarchical clocking scheme with conditional clocks that turn off sections of the chip that are not needed on a cycle-by-cycle basis [34]. Dynamic voltage scaling scales down the supply voltage when the workload is not intensive [32]. At logic synthesis level, precomputation method is proposed which adds combinational logic in front of the original circuit to precompute the output logic values of a subset of input cases so that part of the circuit could be turned off in the succeeding clock cycle [36]. Path equalization makes all signal paths from input to output of the same length to minimize spurious switching activities [37]. Local transformations like re-factoring, re-mapping, phase assignment and pin swapping seek to have gates with high switching activity fan out to nets with small capacitance [37]. Finite state machine encoding also matters because the hamming distance between two codes determines the number of switchings [39]. At circuit level, static voltage scaling can be applied, where critical units and non-critical units are powered by higher and lower supply voltages, respectively [29, 30]. Transistor sizing is also effective in that it reduces load capacitance [38].

To minimize leakage power, varieties of techniques are also proposed at different design levels. At system level, dynamic  $V_t$  scaling technique will automatically adjust threshold voltage depending on the current workload [24, 25]. Less leakage will be consumed by increasing  $V_t$  when workload is small. At logic synthesis level, approaches like input vector control takes advantage of transistor stacking effect and selects an optimal input vector to minimize subthreshold leakage in standby mode [16, 17]. At circuit level, multithreshold-voltage CMOS (MTCMOS) reduces standby leakage power by inserting high  $V_t$  devices in between power/ground line and low  $V_t$  circuitry. The low  $V_t$  circuitry will be cut off from power/ground during standby mode by the high  $V_t$  devices to reduce leakage [18, 19]. Dual  $V_t$  technique assigns high  $V_t$  to transistors on non-critical paths, while maintaining the performance by preserving low  $V_t$  to transistors on critical paths [112]. Variable threshold CMOS (VTCMOS) employs self-substrate bias circuit and applies a reverse body bias in standby mode to increase threshold voltage and cut off leakage current [41, 20]. Similarly, dynamic threshold CMOS is also able to alter threshold voltage by connecting the gate and body together [21, 22].

## 1.3 New Challenges and Opportunities for Power Efficient Design

All the challenges in deep submicron design we describe in Section 1.1 have impact on the power and energy efficient design methodologies developed in the past couple of decades. Among others, the dominance of leakage, the manufacture variation, the on-chip temperature variation, and higher reliability requirement highlight the new challenges. These are the features that most of the low power design methods developed in the pre deep submicron era did not consider explicitly and adequately.

The recent research advances in deep submicron design, such as the mechanisms of leakage, the source and characterization of manufacture variation, the cause and models of on-chip temperature variation, provide us the opportunity to incorporate these important issues in power efficient design. Since the late 1990's, not only have we seen many new low power techniques targeting deep submicron design, but also the growing trend of combining two or more techniques simultaneously for further power efficiency.

Meanwhile, there is another design trend known as physical synthesis that integrates physical design with high level synthesis. In deep submicron domain, design productivity requires system level specifications to sign off into reliable and predictable handoffs at physical design level. However, the growing silicon complexity makes it difficult to estimate the effects of an optimization factor on eventual design quality (speed, power, signal integrity, reliability and manufacturing variability). To avoid excessive guardbanding, the design in logic synthesis level and even system level must become more closely related to physical design. In some cases, it is accomplished by characterizing the target physical design specifications at logic or system level. In some other cases, it involves repeated iterations of synthesis stage and placement and/or routing stage to achieve design spec closure.

Finally, deep submicron design does bring many challenges and there is the need to re-visit many of the existing CAD tools and algorithms. However, from practical point of view, it is not desirable for EDA and semiconductor industry to re-design and re-development these tools. The goal of this dissertation is to demonstrate that it is feasible to modify the current CAD tools and algorithms to incorporate the new features and requirements of deep submicron design. Specifically, we will elaborate our idea and approach through the following four examples.

Peak current is one of the vital physical parameters for circuit reliability. Short-lived high current pulses can bring large voltage drops to the power line or ground bounce, both of which can impact circuit timing [57, 54, 69] or lead to logic errors[54, 69]. As the feature size continues shrinking, the metal conductors are much finer than before. This imposes an even greater challenge for designers to control the peak current in order to avoid electromigration effect [56, 64, 58]. It is known that peak current in synchronous circuits usually occurs at clock transition, when the clock tree, flip-flops, and the combinational circuits directly driven by the flip-flops switch simultaneously. A recent report based on SPICE simulation shows that peak current in a synchronous circuit is dominated by the current in state registers, which can be characterized at logic synthesis level by the maximum number of state bits switching in the same direction in the finite state machine (FSM) model. Therefore, it becomes interesting to study how to incorporate peak current reduction into the traditional average power minimization technique at logic synthesis stage.

It has been a common practice in today's industry design to combine the

multiple power optimization techniques while achieving timing closure. For example, dual  $V_t$  technique and gate sizing have been used simultaneously to leverage timing slack for leakage and dynamic power savings [79, 112, 78, 38]. However, in deep submicron design, the room for changing threshold voltage and sizing gates becomes much smaller. In addition, the timing budget becomes tighter and tighter. These significantly limit the effectiveness of low power design techniques that rely on the power versus timing tradeoff. Process-induced mechanical stress is a novel technique induced into CMOS channel that enhances carrier mobility and reduces transistor delay [87, 88, 89]. With the pre-characterized stress-enhanced cell into the library [90], we will be able to integrate mechanical stress optimization into the power optimization process.

Excessive power dissipation in a certain chip region can result in local heat accumulation and therefore hot spots. For a high-performance microprocessor chip, the hot spot temperature can be  $50^{\circ}C$  higher than other regions, which can potentially become a reliability issue. Meanwhile, since leakage current has an exponential dependency on temperature, the leakage power consumption can be much larger in high temperature region, which will in turn exacerbate heat accumulation. Traditional dual  $V_t$  technique assumes a uniform on-chip thermal distribution, which can either lead to too pessimistic or too optimistic design. Therefore it would be more accurate and effective if thermal profile can be taken into consideration during the dual  $V_t$  design procedure. Because of the interdependency between leakage and temperature, it is necessary to iteratively update thermal and power profile each time dual  $V_t$  assignment is performed. However, thermal profile can not be obtained

until the placement is performed and physical location of each cell is known. As a result, further investigation needs to be conducted for thermal-aware dual  $V_t$  techniques.

On-chip temperature does not only affect leakage, it also has impact on power optimization techniques at system level. Dynamic voltage scaling (DVS) is one of the most popular power management techniques at system level. Generally the supply voltage is scaled down so that scheduled tasks can be finished exactly at its deadline to save dynamic power and energy [124, 132]. When leakage starts to dominate dynamic power, it is believed that more total energy can be saved if tasks can be finished earlier and the system can be shut down to avoid leakage consumption [125, 128, 137, 116, 119, 120, 138]. However, the DVS policies proposed in existing works either ignore leakage power or treat leakage as a temperature-independent constant. It is therefore of first importance to propose an accurate transient temperature model that fully considers temperature-leakage interdependency in order to enhance the DVS technique.

## 1.4 Key Contributions

As illustrated in the previous section, multiple techniques should be combined to achieve further power efficiency and higher level designs must be more closely linked to physical design to improve design productivity. This thesis proposes several enhancement to traditional power optimization techniques, regarding issues of peak current, on-chip temperature and layout-dependent mechanical stress in deep

submicron domain.

• Enhancing FSM Power Efficient Design by Simultaneous State Repli-Traditional FSM power efficient design cation and State Re-encoding: targets minimization of average power consumption, particularly, dynamic power consumption. It is well known that dynamic power relates to the total switching activities (TSA) [53]. However, peak current can remain high even when average power is minimized, affecting circuit's reliability. Huang et al. [70] show a strong correlation between the peak current in a sequential circuit and the maximum number of state registers switching in the same direction upon state transitions, referred to as peak switching value (PSV). In the work presented in Chapter 3, we propose an enhanced FSM synthesis framework that takes both average power minimization and peak power reduction into consideration. The enhanced framework applies power optimization techniques state replication [74] and state re-encoding simultaneously. Starting with an already synthesized FSM with, for example, minimal average power as the synthesis target, we identify all the transitions that reach maximum PSVand put them into a working set S. Then we construct the corresponding solution pool SP that includes all the feasible codes for reducing the PSV by state replication or state re-encoding. We pick the least constraining solution from SP for the most constrained transition in S and perform an update over S and SP. We continue this procedure until either S or SP becomes empty. In the former case, it means that PSV has been reduced. In the latter, it

means that we fail to reduce PSV. Our experiments show that out of the 52 MCNC FSM benchmarks encoded by power-driven encoding algorithm POW3 [55], 39 of them are not optimal in terms of PSV. Our approach can improve 34 of them with an average 39.2% reduction, while [70] can improve 27 benchmarks with an average 24.5% reduction. Meanwhile, our approach only incur 3% overhead in TSA compared to POW3 and [70].

• Improving Dual  $V_t$  Technology by Simultaneous Gate Sizing and Mechanical Stress Optimization: Process-induced mechanical stress is used to enhance carrier mobility and drive current in contemporary CMOS technologies. Stressed cells have reduced delay but larger leakage consumption. Its efficient power/delay trading ratio makes mechanical stress an enticing alternative to other power optimization techniques. The work in Chapter 4 re-evaluates the concept of leakage minimization with multiple techniques simultaneously (dual  $V_t$ , gate sizing, and mechanical stress in our discussion). More specifically, we first balance the circuit paths as close to the timing constraint as possible (apply dual  $V_t$  in our case) and identify paths that do not have sufficient slack for further leakage reduction with high  $V_t$ . Then we repeat the following 2-step procedure: using gate sizing and/or mechanical stress to create new slacks at the cost of power overhead; using dual  $V_t$  to trade these new slacks for power saving. We introduce the concept of urgent paths to help us locate the cells that would relax as many paths as possible in the first step. The use of mechanical stress is shown to achieve 9.77% leakage and 2.79% total power savings over combined gate sizing and dual  $V_t$  approach. Moreover, the employment of urgentpath also plays a crucial role in power optimization, achieving 13.5% leakage and 5.00% total power reduction compared to the sensitivity-based approach in the existing literature.

• Enhancing Dual  $V_t$  Leakage Minimization by Considering On-Chip **Temperature Variation:** In Chapter 5, we aim to use on-chip temperature variation and coupling effects between leakage and temperature to guide further leakage reduction. The temperature profile can be obtained by 3-D mesh model [96] given the placement information and  $V_t$  assignment. The proposed temperature-aware dual  $V_t$  algorithm is a three-phase procedure. First, we obtain the temperature profile based on an initial  $V_t$  assignment. Then we repetitively adjust this initial assignment by changing as many low  $V_t$  cells as possible in hot region to high  $V_t$  (for leakage reduction), and changing as few high  $V_t$  cells as possible in cool regions to low  $V_t$  (for timing closure). Temperature profile is updated at the end of each iteration. This second phase will stop when there is little leakage savings or temperature variation becomes trivial. After the second phase, slacks tend to be distributed to cells in hot region where the change of low  $V_t$  to high  $V_t$  gives more leakage saving. In the last phase, we take advantage of slacks created from timing closure step and search for further leakage reduction. The experiment is performed on five large circuits from OpenCores [115], ranging from a few thousands to over 50K cells. We use a TSMC 65nm low-power dual- $V_t$  library with 17 base cells. The circuits are synthesized and placed by Synopsys Design Compiler and IC Compiler respectively. Synopsys Power Compiler provides leakage power evaluation and the intial  $V_t$  assignment (using dual- $V_t$  algorithm described in [111]). The results show that we are able to achieve an average of 11.2% in leakage saving and 39% reduction of cells in hot regions without timing failure.

• Enhancing DVS Technique for Real-Time Systems by Incorporating Temperature-Leakage Interdependency: In the work presented in Chapter 6, temperature-aware design approach is applied to system level. Dynamic voltage scaling (DVS) is one of the most effective techniques to reduce dynamic power for real-time systems. We first study the interdependency of temperature and leakage and how it influences DVS. We derive a temperature model in analytic form that considers the interdependency between leakage and temperature so that the transient behavior of temperature can be captured. We then re-visit DVS approaches and find that, for a single task that starts execution from time zero, scaling down the voltage to the lowest level without missing execution deadline gives the most total energy saving with the parameters in the current technology. With the presence of idle time, allocating all of it before executing the task helps cooling down the system, and thus achieves the most energy saving. However, for a set of non-preemptive real-time tasks, the same idle time distribution strategy may result in high starting temperature for the subsequent task. Based on the observation that an idle time of  $1.5 \times R \times C$  will be sufficient for the system cooling procedure,

we propose an efficient online DVS scheduling policy for total energy minimization. Experimental results show that the traditional DVS and CS-DVS approaches consume 6% and 9% more total energy, respectively.

## Chapter 2

### Preliminary

#### 2.1 Power Fundamentals

There are three major sources of power dissipation in a CMOS circuit [12]:

$$P_{total} = P_{dynamic} + P_{leakage} + P_{SC} (2.1)$$

$P_{dynamic}$  is the dynamic power,  $P_{leakage}$  is the leakage power, and  $P_{SC}$  is the short circuit power.

The dynamic power is caused by charging and discharging the parasitic capacitance in the circuit. It can be modeled as follow:

$$P_{dynamic} = \alpha C V_{dd}^2 f_{CLK} \tag{2.2}$$

where  $\alpha$  is the switching activity, which is the effective voltage transitions per clock cycle. C is the load capacitance,  $V_{dd}$  is the supply voltage, and  $f_{CLK}$  is the clock frequency.

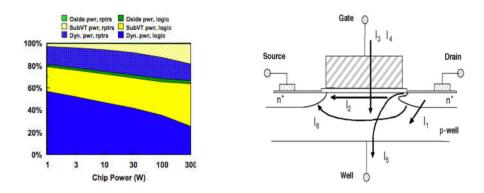

High leakage current in deep submicron era is becoming a significant contributor to power dissipation of CMOS circuits as threshold voltage, channel length, and gate oxide thickness are reduced. As indicated by the left chart in Figure 2.1, leakage power consumption can take up to 50% of the total power for 45nm technology node [5].

Figure 2.1: Left: Cumulative power allocation fractions for the logic in processor cores, for 45nm node [5]. Right: Leakage current mechanisms of deep-submicrometer transistors [105].

There are six leakage mechanisms [4], shown in the right subfigure in Figure 2.1: the reverse bias pn junction leakage  $(I_1)$ , subthreshold leakage  $(I_2)$ , oxide tunneling current  $(I_3)$ , gate current due to hot-carrier injection  $(I_4)$ , gate induced drain leakage  $(I_5)$ , and channel punchthrough current  $(I_6)$ . In long-channel devices, leakage is dominated by reverse bias pn junction leakage, while in deep submicron domain, subthreshold leakage takes the larger proportion in short-channel transistors. It is because short-channel transistors require lower power supply levels to reduce power consumption. The lower power supply levels force a reduction in threshold voltage to maintain a high drive current, which can cause substantial increase in leakage. This is commonly referred to as Short Channel Effects (SCE) [105]. Meanwhile, oxide thickness has to be reduced nearly in proportional to the channel length to maintain a reasonable SCE immunity. The decrease in oxide thickness results in increase in the electric field, which along with thinner oxide, can result in considerable leakage current flowing through the gate. As a result, the major leakage sources in deep submicron domain include subthreshold leakage and gate oxide leakage (contributed by three mechanisms of  $I_3$ ,  $I_4$  and  $I_5$ ). In current technology, gate leakage current can be largely supressed by using high-k dielectric materials, while subtheshold leakage is still a serious concern. Moreover, subthreshold leakage has an exponential dependency on temperature according to BSIM model [140].

Besides dynamic power and leakage power, the short circuit power can be kept less than 15% of the dynamic power with careful design [13] and therefore is no longer a big concern.

#### 2.2 Power Efficient Design Techniques for CMOS Circuits

Extensive researches have been performed on power efficient design at different design levels. In the following, we provide a survey on various power efficient design techniques at various design levels [105, 15].

## 2.2.1 Dynamic power minimization

Dynamic power minimization can be achieved by decreasing any of the four factors that appear in Equation 2.2.

• Dynamic Power Management: Dynamic power management (DPM) is a design methodology that dynamically reconfigures a system to provide the requested services and performances with a minimum number of active components or a minimum load on such components [33]. Clock gating is a typical example of DPM. Since the power dissipation of the clocked components in a

system is often the largest of the total power consumption, clock gating uses a hierarchical clocking scheme with conditional clocks that turn off sections of the chip that are not needed on a cycle-by-cycle basis [34]. Similarly, [35] propose to shut down the idle components of a system to save both dynamic and leakage power. However, both approaches suffer from latency penality and power overhead.

- Dynamic Voltage Scaling: Because of the quadractic dependence of the dynamic power on supply voltage, it is very effective to reduce the dynamic power if the supply voltage scales down. The operating system of a microprocessor can intelligently determine the processor speed. Then the power management unit generates the minimum voltage required for the desired speed. All devices of the microprocessor work at the same frequency under the same supply voltage. When it comes non-intensive task, the operating system scales down the supply voltage to save power [32]. Dynamic Voltage Scaling (DVS) can also fall into the category of DPM.

- Static Voltage Scaling: Static voltage scaling is also based on the quadratic dependence of the dynamic power on supply voltage [29, 30]. However, multiple supply voltages are provided. It is of the same flavor as dual  $V_t$  technique, where critical units and non-critical units are powered by higher and lower supply voltages, respectively. The differences are that the critical and non-critical units are clustered as much as possible and level converter is inserted at the interfaces of low  $V_{dd}$  to high  $V_{dd}$  units.

- Precomputation method: Precomputation method adds combinational logic in front of the original circuit. It can precompute the output logic values of a subset of input cases one clock cycle before they are required so that part of the circuit could be turned off in the succeeding clock cycle [36]. This method reduces both load capacitance and switching activity.

- Path equalization: Path equalization transforms the logic network so that all signal paths from input to output have the same length. This ensures that most gates can have aligned transitions at their inputs, thereby minimizing spurious switching activities [37]. This technique is very effective in arithmetic circuits as they have more regular structures. For those with irregular structures, gate resizing can be applied so that the delay of fast paths can be equalized to that of critical paths without affecting circuit timing.

- Local transformations: Techniques like re-factoring, re-mapping, phase assignment and pin swapping can all be classified as local transformations. They are applied on gate netlist and target the nets with large switching capacitance ( $\alpha C$ ). They seek to fan out nodes with high switching activity to the net that contributes small load capacitance [37].

- Finite State Machine encoding: State encoding is to assign a unique code to each state such that certain cost function of binary logic level can be minimized. As the 01 or 10 switching at binary logic level will result in the switchings in flip-flops, the hamming distance of two codes involved in each transition should be as small as possible to minimize dynamic power [39].

• Transistor sizing: Transistor sizing is exploited in both combinational cells and flip-flops to minimize dynamic power consumption [38]. By sizing down the transistors, load capacitances and thereby power consumption of the fanin components can be largely reduced. Sizing down flip-flops can be especially effective in reducing power as flip-flops contribute to the load of clock distribution network, which constantly involves switching activities. However, sizing down transistors can increase transistor delay, so transistor sizing needs to be carefully designed to take advantage of power-delay tradeoff.

#### 2.2.2 Leakage power minimization

As leakage power has become a major contributor to the total power dissipation in deep submicron technology, it is crucial to take leakage power minimization into consideration.

• Transistor stacking effect: The subthreshold leakage flowing through a stack of transistors is significantly smaller if more than one transistor in the stack is turned off. Because of this stacking effect, the magnitude of subthreshold leakage can be largely dependent on the applied input vector, which is propagated from primary input vector. Due to the exponential size of primary input vectors, an enumerative approach is impractical. [16] applied a random search-based approach, while [17] employed a genetic algorithm to speculate new search points with potentially improved performance. In [14], a low  $V_t$  transistor is inserted into the stack and is turned off in standby mode

to reduce subthreshold leakage.

• Multiple-threshold technologies: The threshold voltage of a transistor can be adjusted by means of channel-doping densities, gate oxide thickness, channel length and body bias. Various techniques have been proposed that take advantage of different properties of different  $V_t$  transistors: low  $V_t$  trans sistors are used to achieve high performance, while high  $V_t$  transistors can suppress subthreshold leakage power. Multithreshold-voltage CMOS (MTC-MOS) reduces standby leakage power by inserting high  $V_t$  devices in between power/ground line and low  $V_t$  circuitry. The low  $V_t$  circuitry will be cut off from power/ground during sleep mode by the high  $V_t$  devices to reduce leakage [18, 19]. MTCMOS can bring delay overhead in active mode and area overhead to the circuit. Dual  $V_t$  technique assigns high  $V_t$  to transistors in non-critical paths, while maintaining the performance by preserving low  $V_t$  to transistors on critical paths [112]. Dual  $V_t$  technique is able to suppress leakage in both active and standby modes. Variable threshold CMOS (VTCMOS) employs self-substrate bias circuit and applies a reverse body bias in standby mode to increase threshold voltage and cut off leakage current [41, 20]. However, the effectiveness of reverse body bias has been decreased as technology scales. Dynamic threshold CMOS (DTMOS) is able to alter threshold voltage dynamically by connecting the gate and body together [21]. DTMOS is only suitable for ultralow voltage circuits. Double-gate dynamic threshold SOI CMOS (DGDT-MOS) combines the advantage of DTMOS and double-gate FD SOI MOSFETs without limitations on the supply voltage [22].

- Super cutoff CMOS: Super cutoff CMOS (SCCMOS) uses an on-chip boost voltage to provide reverse bias on the sleep transistor to cut off the leakage current in standby mode [23]. Different from MTCMOS, the sleep transistor is low  $V_t$  and therefore the circuit can work at lower supply voltages.

- Dynamic V<sub>t</sub> Scaling: Dynamic V<sub>t</sub> scaling will automatically adjust threshold voltage as well as operating frequency depending on the current workload [24, 25]. When workload is small, less leakage power is consumed by increasing V<sub>t</sub>.

- SRAM Cache memory leakage reduction: Memory structures (instruction and data caches, prediction tables and translation look-aside buffers) in modern microprocessors have taken large fraction of chip areas. In deep submicron technology, caches account for a large component of leakage power consumption. Several techniques have been proposed to address this issue. Date retention gated-ground chache places an extra NMOS transistor in the leakage path from power to ground of SRAM cells. The unused portions of cache is changed into low leakage mode by turning of the extra NMOS transistor [26]. Drowsy cache [27] and Dynamic V<sub>t</sub> SRAM [28] utilizes multiple supply voltages and dynamic threshold voltages by body biasing to reduce SRAM leakage.

### 2.3 Summary

In this chapter, we first address the three major sources of power consumption in CMOS circuits: dynamic power, leakage power and short circuit power. Dynamic power has already been a major component of power consumption. With continous scaling of CMOS devices, however, leakage power starts to dominate dynamic power and becomes a emerging challenge for power efficient design. On the other hand, short circuit power can be largely suppressed in today's technology. We then review the most popular and representative techniques that minimize dynamic power and leakage power respectively. The techniques apply to various design levels. Take the dynamic power minimization techniques for example. DPM and DVS apply to system level design, requiring software support. Precomputation, path equalization, FSM encoding and local transformations belong to logic synthesis level. Transistor sizing can be categorized into circuit level.

### Chapter 3

Finite State Machine Synthesis Technique for Peak Current

#### Reduction

Peak current reduction has attracted more and more attention in circuit design at deep sub-micron technology node. Peak current is vital for circuit reliability because short-lived high current pulses can cause a metal line to fail instantaneously and large voltage drops that impact circuit timing [57, 54, 69]. As the feature size continues shrinking, the metal conductors are much finer than before. This imposes a great challenge for designers to control the peak current in order to meet the electromigration specification when the peak current occurs [56, 64, 58]. In addition, the supply voltage in today's digital circuits has been consistently scaled down to reduce power consumption. Large voltage drops caused by peak current can have a serious impact on circuit timing and may lead to timing failures and logic errors [54, 69].

In synchronous circuits, peak current usually occurs at clock transition, when the clock tree, flip-flops, and the combinational circuits directly driven by the flip-flops switch simultaneously. Many approaches at different design levels have been proposed to mitigate the large current flows at clock transitions. At system level, various clock skew scheduling algorithms are proposed to achieve more even distribution of clock arrival times [58, 59, 60, 61, 62, 63]. At physical level, many works

seek to change polarities of clock buffers so that current flows can be altered into opposite directions [64, 65, 66, 67]. Other techniques like MTCMOS [68] and flip-flop resynthesis [69] can also be applied at physical design stage to reduce peak current. Very few works happen at logic synthesis level. The only two works we are aware of are state register re-encoding approach [70] and SAT-based encoding [71].

Peak current reduction at FSM synthesis level is based on the two observations:

(i) peak current in an FSM circuit is largely dependent on peak current in state registers. This is because the state registers often have large switching current due to their large load capacitance at the fanouts. Besides, all the state registers switch simultaneously at the arrival of the clock signal (assuming a very small clock skew).

(ii) peak current in state registers are directly related to the maximum number of state bits switching in the same direction. This is because when state bits switch from one logic value to the other. The total currents in power or ground nets are the sum of the charging or discharging current in individual registers.

We focus on minimizing peak current in state registers during state transition in FSM. For a given encoded FSM, we first identify the state transitions that cause peak current, then we consider state replication and state re-encoding simultaneously to reduce the maximal number of charging and discharging on such state transitions. In state re-encoding, we aim to find a new code for a state that currently contributes to peak current. In state replication, we create a copy of a state and assign it a different code to reduce the charging and discharging on that state transition. Our proposed approach seamlessly combines these two basic techniques by the most constrained least constraining paradigm [72] and outperforms the state-

of-the-art FSM level approach [70] in reducing peak current on most of the MCNC benchmark circuits.

We have made the following contributions in peak current reduction for FSM in this article:

- This is the first work of re-encoding state for peak current reduction. Although Huang et al. use the same term in [70], our method is completely different from theirs. In fact, the solution space they consider is only a very small subset of ours.

- We have applied the *state replication* technique proposed by Yuan et al. [74] for peak current reduction. By the nature of state replication, it gives us more freedom and options to reduce the maximal charging and discharging and therefore peak current.

- We propose the simultaneous state replication and re-encoding (SSRR) algorithm that combines these two techniques by the most constrained least constraining paradigm. The algorithm takes an encoded FSM as input and produces a new encoded FSM with less peak current. Its complexity is polynomial to the number of states and the number of transitions in the FSM.

- We have implemented the power-driven state encoding algorithm POW3 [55], the only existing peak current minimization approach at FSM level [70], and our *SSRR* and apply them to the entire 52 MCNC benchmark circuits. At FSM level, *SSRR* reduces *PSV* on 34 of the 36 circuits that POW3 is unable to minimize with solutions 18.4% better than those found by [70].

The rest of the article is organized as follows. In Section 3.1, a brief survey on recent works for peak current reduction is conducted. In Section 3.2, we define the necessary terms and review the two most relevant works. The two basic techniques, state replication and state re-encoding, are illustrated using an example in Section 3.3 to show how they can be improved or tuned for our purpose. Then we discuss in details how we can combine these two techniques seamlessly to reduce peak current and total dynamic power in Section 3.4. An illustrative example is given in Section 3.5 to help understand the proposed approach. Section 3.6 reports the experimental setup and results. Section 3.7 concludes.

### 3.1 Related Works

Different approaches have been proposed to reduce peak current. For a synchronous circuit, peak current can be mostly observed at the moment of clock transitions, because clock buffers at the same level in the clock tree, flip-flops and combinational cells driven by the flip-flops can switch at the same time window. As a result, lots of charging and discharging can happen to the load capacitances of the transistors involved with these units. Varieties of clock skew scheduling approaches have been proposed [58, 59, 60, 61, 62, 63]. These works aim at finding an optimal distribution of clock arrival time so that the current pulses from neighboring units will have less overlap and accumulation. Benini et al. [58] formulated the problem of finding optimal clock latencies as an NP-complete problem, and proposed a Genetic Algorithm (GA) to solve it. GA-based technique has long run time, and the objective

function used requires pre-characterization of individual flip-flops for each circuit, which is also timing-consuming. Vittal et al. [59] formulated the problem into Integer Linear Programming (ILP) problem under the constraint of multi-domain clock skews. Both the complexity of ILP problem and extensive circuit simulations involved with the objective function also renders this approach impractical for large circuits. Huang et al. [60] accelerated this work by first applying ASAP and ALAP scheduling policies to prune the redundancies in ILP formulation, then further applying a zone-based scheduling algorithm to solve large circuits heuristically. Yu et al. [61] instead, seeks to achieve the statistically even distribution of clock skews by setting skew variance as the optimization objective, which is not linear. A heuristic that gradually tunes initial solution by peak trimming and valley filling is proposed to solve the problem. Rahimi [62] considers the load capacitances of flip-flops when spreading clock transitions. It creates a center-of-gravity constraint to help balance clock latencies around the center of the search interval. Mukherjee et al. [63] considers the impact on peak current from clock buffers, flip-flops and fanout combinational cells all at the same time by combining retiming and clock scheduling techniques.

Another group of works seek to change polarities of clock buffers by replacing them with inverters for peak current reduction and power/ground noise control [64, 65, 66, 67]. Nieh et al. [64] proposed an opposite-phase approach that changes clock buffer close to the root of clock tree into inverter, which successfully reduces peak current. However, the power/ground noises in a local area are not. Samanata et al. [65] observed that power/ground noises are sensitive to the locations of clock

buffers and proposed to replace half of the buffers in some particular locations with inverters. However, it can render the clock skew out of control. Chen et al. [66] assigns signal polarities at the leaves of clock tree, so that peak current and power/ground noises can be reduced simultaneously, and clock skew can also be kept in control. Jang et al. [67] applies buffer sizing together with polarity assignment to the minimization of power/ground noises while satisfying the clock skew constraint.

Other techniques like MTCMOS and flip-flop resynthesis are also addressed in concern of peak current. Lu et al. [68] applies Mutiple Threshold CMOS (MTC-MOS) technique by changing cells in non-critical paths to high  $V_t$  to reduce both peak current and leakage power in the circuit. Wu et al. [69] introduces long delay flip-flops to reduce peak current by flip-flop resynthesis. It is similar to traditional clock skew scheduling, however more advantageous in the sense that it is able to bypass hold time constraints. Moreover it can be applied to either logic synthesis stage or physical design stage.

However, very few peak current reduction works happen at FSM synthesis level. Since a sequential circuit can be represented by a set of finite state machines (FSM) at logic synthesis level, FSM state encoding (or re-encoding), which seeks to assign distinct binary codes to each state in the FSM, is a well know problem in sequential circuit optimization. Most early work (such as JEDI, MUSTANG, MUSE, etc.) focus on minimizing circuit area [73]. Many power-driven state encoding techniques that target at reducing the circuit switching activity have been proposed in the mid-90s. A representative work among them is the *POW3* encoding proposed by Benini and De Micheli [55]. A brief survey on power-driven state encoding can be

found in a recently published work [74], where a novel approach to re-construct FSM for low power is proposed. [70] and [71] are the only two works we are aware of that target at minimizing peak current by FSM state encoding. Huang et al. [70] consider reducing peak current using FSM synthesis technique. They first conduct SPICE simulation to show that peak current in power line  $V_{dd}$  and  $V_{ss}$  are directly related to the maximal number of simultaneous charging and discharging, respectively, in the state registers. They then propose a state re-encoding technique to reduce peak current by reducing the maximum number of state registers that switch in the same direction. Lee et al. [71] first achieves the optimal solution that minimizes peak current by formulating the state encoding into SAT problem with pseudo-Boolean expressions, then further reduces the switching power without deteriorating the minimum peak current using an efficient SAT-based heuristic.

### 3.2 Preliminaries

In this section, we give the necessary background on FSM model and then describe the two most relevant works: peak current reduction by state re-encoding [70] and FSM re-engineering for switching activity and power reduction [74].

# 3.2.1 Finite State Machine Synthesis

FSM is a popular model for sequential circuit design. We use the state transition graph (STG)  $G = (V, E, \{C_i\}, \{w_{ij}\})$  to represent an encoded FSM, where a node  $v_i \in V$  represents a state  $s_i$  (or i for short);  $C_i = c_{i0}c_{i1} \cdots c_{ik}$  is a (k+1)-bit

code assigned to state  $s_i$ ; a directed edge  $(v_i, v_j) \in E$  between nodes  $v_i$  and  $v_j$  represents a state transition from state  $s_i$  to state  $s_j$ ; and the non-negative value  $w_{ij}$  is its transition probability.

FSM synthesis consists of state minimization and state encoding. State minimization finds a functionally equivalent FSM that has the minimum number of states. State encoding assigns distinct codes to each state of the FSM such that the sequential circuit modeled by the FSM can be efficiently implemented in terms of area, performance, or power. State re-encoding is an approach to adjust the codes of certain states in order to optimize some objectives (e.g. power and performance) while the current coding scheme optimizes other objectives (e.g. area).

For a state transition  $s_i \to s_j$ , for convenience, we call  $s_i$  a previous-state of  $s_j$ ,  $s_j$  a next-state of  $s_i$ , and they are neighboring states to each other. The transition's switching activity is defined as the Hamming distance  $H(C_i, C_j)$  between their codes  $C_i$  and  $C_j$ . The total switching activity (TSA) of the encoded FSM is defined as the following weighted sum:

$$TSA = \sum_{(v_i, v_j) \in E} w_{ij} H(C_i, C_j)$$

(3.1)

Let  $p_{ij}(0 \to 1)$  denote the number of bits switching from 0 to 1 during the state transition  $s_i \to s_j$ . That is, the number of bits that have value 0 in  $C_i$  but change to value 1 in  $C_j$ . Take the state transition from 101100 to 001010 for example,  $p_{ij}(0 \to 1)$  equals one and is contributed by the second bit from the right. We can define  $p_{ij}(1 \to 0)$  similarly, which equals two and are contributed by the first

and fourth bits from the left. We denote the *peak switching value* on this transition  $psv_{ij} = \max\{p_{ij}(0 \to 1), p_{ij}(1 \to 0)\}$ . Obviously,  $psv_{ij} = \max\{1, 2\} = 2$  in this example.

The peak switching value of the entire FSM can be defined as follows:

$$Peak (0 \to 1) = \max_{(v_i, v_j) \in E} p_{ij}(0 \to 1) (3.2)$$

$$Peak (1 \to 0) = \max_{(v_i, v_j) \in E} p_{ij} (1 \to 0) (3.3)$$

$$PSV = \max_{(v_i, v_j) \in E} psv_{ij}$$

$$= \max\{Peak(0 \to 1), Peak(1 \to 0)\}$$

(3.4)

We say that a transition  $s_i \to s_j$  is a critical transition (CT) if  $p_{ij}(0 \to 1)$  or  $p_{ij}(1 \to 0)$  reaches PSV.

The value of TSA is a good indicator of the sequential circuit's average dynamic power; the values of  $Peak(0 \to 1)$  and  $Peak(1 \to 0)$  have a strong correlation with peak current at the power line  $V_{dd}$  and  $V_{ss}$ , respectively [70], which is also validated by Figure 3.7 and Figure 3.8 in Section 3.6. Therefore, we choose PSV as the main optimization objective for peak current reduction. Meanwhile, we try to keep TSA as low as possible in order to minimize average dynamic power.

# 3.2.2 Peak Current Reduction by Re-Encoding

In [70], the authors propose to consider the switching directions of the state register (either go from logic 0 to 1 or go from logic 1 to 0) to reduce the number of state registers that switch in the same direction at the same time. That is, if they decide to change the bit (that is, the switching direction) on one state register, the

code of every state in the FSM will flip at that bit position. Deciding which bit to be changed first follows greedy fashion: At each iteration, the unmarked bit that helps reduce the *peak swiching value* of the entire FSM most or reduce the number of critical transitions most with the same *peak switching value* is flipped and marked.

Table 3.1: Original codes from POW3 for circuit  $ex5_n$  (see Figure 3.1) and the new codes obtained by the state register re-encoding in [70].

| state          | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    |

|----------------|------|------|------|------|------|------|------|------|------|

| $c_0c_1c_2c_3$ | 0000 | 0100 | 0011 | 0010 | 0001 | 0101 | 0111 | 0110 | 1110 |

| $d_0d_1d_2d_3$ | 0101 | 0001 | 0110 | 0111 | 0100 | 0000 | 0010 | 0011 | 1011 |

For example, Table 3.2.2 gives the original codes  $c_{i0}c_{i1}c_{i2}c_{i3}$  for each state i in the FSM shown in Figure 3.1 as well as the new codes  $d_{i0}d_{i1}d_{i2}d_{i3}$  obtained by the re-encoding approach in [70], where we can see that the second and last state registers have been flipped (that is,  $d_{i1} = c'_{i1}$ ,  $d_{i3} = c'_{i3}$ ).

According to the original coding scheme, PSV=3 on two CTs:  $6\to 0$  and  $8\to 0$ , where three state registers change from logic 1 to 0 simultaneously. In the new coding scheme, the PSV is reduced to 2.

# 3.2.3 FSM Re-Engineering for Low Power

Yuan et al. [74] propose a novel re-engineering paradigm for FSM synthesis. Their idea is to construct a new FSM from the minimized FSM to relax the constraints on the most constrained portion of the original FSM. The basic technique they develop to achieve this is state replication, or state splitting as is called in their work. When it becomes hard to find a code for a state without causing large

Hamming distance to one or more of its neighboring states, they create a new state to take away some of the previous-states to make encoding easier and more efficient.

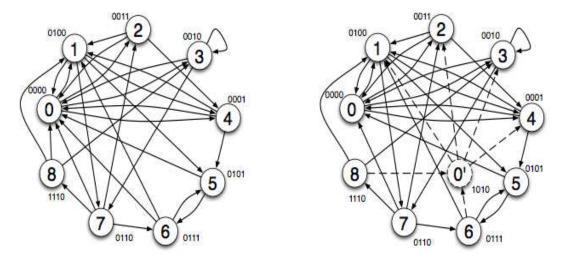

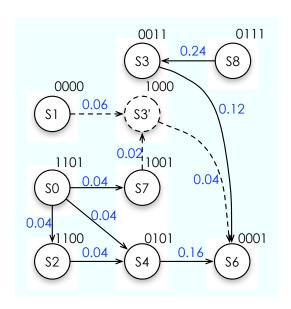

Figure 3.1: The 9-state STG representing MCNC benchmark circuit ex5. Left: the original STG with two CTs  $6 \rightarrow 0$  and  $8 \rightarrow 0$ . Right: new 10-state STG where state 0' is a replicate of state 0 and PSV is reduced from 3 to 2.

For example, on right of Figure 3.1, state 0' is a replicate of state 0 with the two CTs being redirected to this new state. Originally, for transition  $8 \to 0$ , we have H(1110,0000) = 3. Now we have the new transition  $8 \to 0'$  with H(1110,1010) = 1. So the TSA defined in Equation (1) would be reduced.

# 3.3 Two Basic Techniques for peak current reduction

Figure 3.1 depicts circuit ex5 from the MCNC benchmark suite [77], where there are 9 states labeled from 0 to 8. The FSM is encoded by the power driven encoder POW3 [55] and the codes for each state can also be found in Table 1.We can see that on two CTs  $6 \rightarrow 0$  and  $8 \rightarrow 0$ , there are three bits changing from 1 to

0. This means that three state registers will switch from logic level 1 to logic level 0 simultaneously, causing peak current at power line  $V_{ss}$ .

To reduce peak current, which corresponds to PSV = 3, it will be sufficient to make adjustments along each CT such that there will not be three or more state registers switching at the same direction at the same time. The two basic techniques we propose target directly the states that are involved in the critical transitions.

### 3.3.1 State Re-Encoding

Consider the CT  $6 \to 0$ , where the codes for the two states are 0111 and 0000, we can find a new code either for state 6 or state 0 to reduce the number of 1's changing to 0's and thus make this transition not critical. By checking the codes of previous-states of 6:  $\{0101,0110\}$  and its next-states:  $\{0000,0100,0101\}$ , we see that among the seven unused 4-bit codes, any one of the followings  $\{1000,1001,1010,1100\}$  can be used for state 6 such that all the state transitions that are involved with state 6 will not have more than two bits switching from 0 to 1 or from 1 to 0 at the same time. Similarly, we can achieve this by keeping the code of state 6 and re-encoding state 0 to be any of the followings:  $\{1001,1010,1100\}$ .

We refer to this technique as *state re-encoding* because of its nature of assigning a new code to the state. The new code to resolve a CT can be any valid code, not necessarily unused ones. We consider only unused codes in the above example for simplicity. If we use a code that is currently assigned to another state, this state will lose its code and we need to find a new code for it. We will elaborate this later.

If we have an n-state FSM where each state has a distinct k-bit code  $(k \ge \lceil \log_2 n \rceil)$ , potentially each of the n states can be encoded by any of the  $2^k$  k-bit codes. In another word, the state re-encoding space we can explore is as large as  $\binom{2^k}{n} \cdot n!$ .

Note that our approach is conceptually different from the term of state reencoding used by Huang et al. in [70]. They indeed consider the switching direction of the state registers, not individual states. Consequently, in their solution  $d_0d_1\cdots d_i\cdots d_{k-1}$ , for any given bit position  $i, d_i=c_i$  or  $d_i=c'_i$  for all the states. They consider up to all the  $2^k$  combinations of whether to flip each of the k state registers, which is a subset of our re-encoding solution space. Moreover, considering that  $2^k$  is normally of the same order of n,  $2^k$  is much less than  $\binom{2^k}{n} \cdot n!$ .