#### ABSTRACT

Title of dissertation: Exploiting Inherent Program Redundancy

for Fault Tolerance

Xuanhua Li, Doctor of Philosophy, 2009

Dissertation directed by: Professor Donald Yeung

Department of Electrical and Computer Engineering

Technology scaling has led to growing concerns about reliability in microprocessors. Currently, fault tolerance studies rely on creating explicitly redundant

execution for fault detection or recovery, which usually involves expensive cost on

performance, power, or hardware, etc. In our study, we find exploiting program's

inherent redundancy can better trade off between reliability, performance, and hardware cost.

This work proposes two approaches to enhance program reliability. The first approach investigates the additional fault resilience at the application level. We explore program correctness definition that views correctness from the application's standpoint rather than the architecture's standpoint. Under application-level correctness, multiple numerical outputs can be deemed as correct as long as they are acceptable to users. Thus faults that cause program to produce such outputs can also be tolerated. We find programs which produce inexact and/or approximate outputs can be very resilient at the application level. We call such programs soft computations, and find that they are common in multimedia workloads, as well as

artificial intelligence (AI) workloads. Programs that only compute exact numerical outputs offer less error resilience at the application level. However, *all* programs that we have studied exhibit some enhanced fault resilience at the application level, including those that are traditionally considered as exact computations–*e.g.*, SPECInt CPU2000.

We conduct fault injection experiments and evaluate the additional fault tolerance at the application level compared to the traditional architectural level. We also exploit the relaxed requirements for numerical integrity of application-level correctness to reduce checkpoint cost: our lightweight recovery mechanism checkpoints a minimal set of program state including program counter, architectural register file, and stack; our soft-checkpointing technique identifies computations that are resilient to errors and excludes their output state from checkpoint. Both techniques incur much smaller runtime overhead than traditional checkpointing, but can successfully recover either all or a major part of program crashes in soft computations.

The second approach we take studies value predictability for reducing fault rate. Value prediction is considered as additional execution, and its results are compared with corresponding computational outputs. Any mismatch between them is accounted as symptom of potential faults and incurs restoration process. To reduce misprediction rate caused by limitations of predictor itself, we characterize fault vulnerability at the instruction level and only apply value prediction to instructions that are highly susceptible to faults. We also vary threshold of confidence estimation according to instruction's vulnerability—instructions with high vulnerability are assigned with low confidence threshold, while instructions with low vulnerability

are assigned with high confidence threshold. Our experimental results show benefit from such selective prediction and adaptive confidence threshold on balance between reliability and performance.

# Exploiting Inherent Program Redundancy for Fault Tolerance

by

# Xuanhua Li

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2009

Advisory Committee:

Professor Donald Yeung, Chair/Advisor

Professor Gang Qu

Professor Manoj Franklin

Professor Bruce Jacob

Professor Amr Baz

© Copyright by Xuanhua Li 2009

# Dedication

For my lovely baby Kelly.

#### Acknowledgments

I sincerely express my gratitude to all the people who have made this thesis possible. Because of their kindness and love, my graduate experience has been one that I will cherish forever.

First of all, I really thank my advisor, Dr. Donald Yeung. He has not only patiently advised my research throughout my long stay in the graduate program, but also impressed me for life with his own integrity, intelligence, passion to work, etc. I always enjoyed the time discussing problems with him. And his help and advices have helped me to overcome numerous difficulties.

I also thank my dear husband, Huanfeng, and my family in China. I always thank God for bringing Huanfeng to my life. He is such a wonderful husband, a good friend and listener. I know no matter what happens, he is always there supporting me. I also thank my own family—my dad and mom, my brother and sister-in-law, and my little niece. Although they are far away from me, their consistent love and caring have supported me throughout the past years. I especially thank my brother, Menghua, for all he has done and is doing for our family.

I always feel lucky to be one of the members in Systems and Computer Architecture Lab (SCAL). I thank my colleagues for their help and discussion: Seungryul, Dongkeun, Hameed, Wanli, Meng-ju, Inseok, Xu, Aamer, Brinda, Rania, Kursad, Sumesh, Ohm, Zahran, and all other lab-mates. I also appreciate the members of my PhD defense committee: Dr. Gang Qu, Dr. Manoj Franklin, Dr. Bruce Jacob, and Dr. Amr Baz. I would like to acknowledge other graduate students and staffs at

Maryland: Bo, Juanjuan, and Vivian. I also express my special thanks to friends I knew during my internships: Dr. Steve Crago, Janice McMahon, Paul, Saila, Hima, and many others. I apologize to those I have inadvertently left out.

In addition, I thank my baby who is coming to this world soon. I am so excited and looking forward to embracing her.

Lastly, I sincerely thank God for his endless love and care.

# Table of Contents

| Lis | of Figures                                                                                                                                                                                                                                                                                                                                  | vii                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Lis | of Abbreviations                                                                                                                                                                                                                                                                                                                            | xi                                     |

| 1   | Introduction  1.1 Motivation                                                                                                                                                                                                                                                                                                                | . 4                                    |

|     | 1.2 Contributions                                                                                                                                                                                                                                                                                                                           |                                        |

| 2   | Background 2.1 Hardware Faults 2.2 Fault Tolerance 2.2.1 Fault Susceptibility Characterization 2.2.2 Fault Detection 2.2.3 Fault Recovery 2.2.4 Partial Fault Detection/Recovery                                                                                                                                                            | . 14<br>. 14<br>. 16<br>. 17           |

| 3   | Application-level Fault Susceptibility  3.1 Application-Level Correctness  3.1.1 Qualitative Program Outputs  3.1.2 Correctness Definitions  3.2 Fault Susceptibility Experiments  3.2.1 Experimental Methodology  3.2.2 Fault Susceptibility Result  3.3 Sources of Fault Tolerance                                                        | . 19<br>. 21<br>. 22<br>. 23<br>. 29   |

| 4   | Fault Recovery by Exploiting Application-level Correctness 4.1 Lightweight Fault Recovery 4.1.1 Lightweight Recovery Mechanism 4.1.2 Lightweight Recovery Results 4.2 Soft Checkpoint Mechanism 4.2.1 Soft Program State 4.2.2 Soft Recovery Mechanism 4.3 Soft Recovery Results 4.3.1 Soft Checkpoint Cost 4.3.2 Soft Recovery Performance | 38<br>40<br>42<br>44<br>45<br>47<br>48 |

| 5   | Fault Detection with Value Prediction  5.1 Reducing Error Rate with Value Prediction                                                                                                                                                                                                                                                        | . 56                                   |

|    |              | 5.1.3    | Fault Recovery                                                | 63  |

|----|--------------|----------|---------------------------------------------------------------|-----|

|    |              | 5.1.4    | Analysis of Instruction Vulnerability                         | 64  |

|    | 5.2          | Exper    | imental Methodology and Results                               | 68  |

|    |              | 5.2.1    | Simulator and Benchmarks                                      | 70  |

|    |              | 5.2.2    | Value Prediction Experiments                                  | 71  |

|    |              | 5.2.3    | Confidence Estimation                                         | 75  |

|    |              | 5.2.4    | Policy on Measuring Instruction Latency for Value Prediction  | 83  |

|    |              | 5.2.5    | Selective Value Prediction Experiments with Fault Injection . | 84  |

|    |              | 5.2.6    | Discussion about Fault Injection and AVF Computation          | 94  |

|    | 5.3          | Comp     | arison with Fault Screening and Flush-on-L2-miss Techniques . | 97  |

|    |              | 5.3.1    | Summary of Fault Screening and Flush-on-L2-miss Techniques    | 98  |

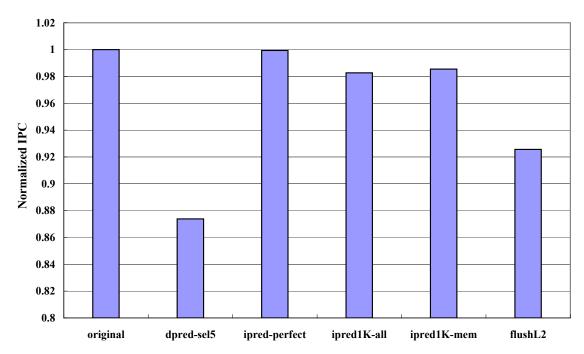

|    |              | 5.3.2    | Performance Impact                                            | 101 |

|    |              | 5.3.3    | Fault Injection Results                                       | 104 |

|    |              | 5.3.4    | Fault Detection Analysis                                      | 108 |

|    |              |          |                                                               |     |

| 6  |              | ited Wo  |                                                               | 110 |

|    | 6.1          |          | Computation                                                   |     |

|    | 6.2          |          | Susceptibility Characterization                               |     |

|    | 6.3          | -        | sis of Fault-Tolerance Sources                                |     |

|    | 6.4          |          | Tolerance Techniques                                          |     |

|    |              | 6.4.1    | Fault Detection                                               |     |

|    |              | 6.4.2    | Fault Recovery                                                |     |

|    |              | 6.4.3    | Reducing Fault Susceptibility                                 |     |

|    | 6.5          | Symp     | tom of Potential Faults                                       | 118 |

| 7  | Con          | clusions |                                                               | 119 |

| 1  | 7.1          |          | s<br>nary and Conclusion                                      | _   |

|    | $7.1 \\ 7.2$ |          | V                                                             |     |

|    | -            |          | ibutions                                                      |     |

|    | 7.3          | ruture   | e Directions                                                  | 123 |

| Bi | bliogi       | raphy    |                                                               | 127 |

# List of Figures

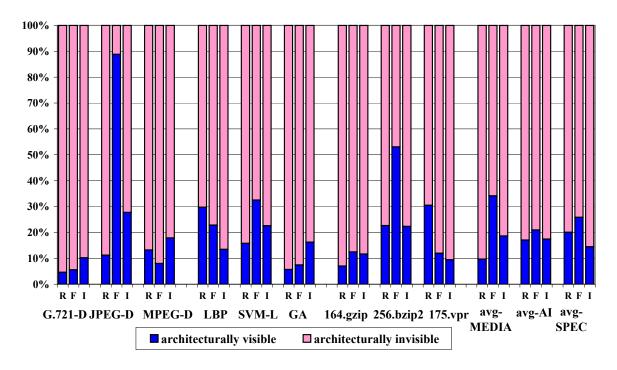

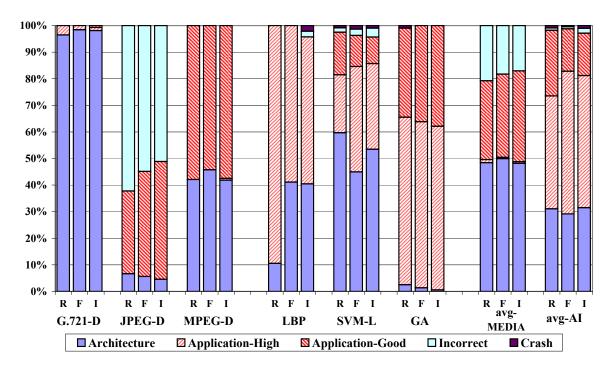

| 3.1 | Breakdown of fault injections on architectural visibility                                                                                                                                                                                                                                                                                           | 31 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

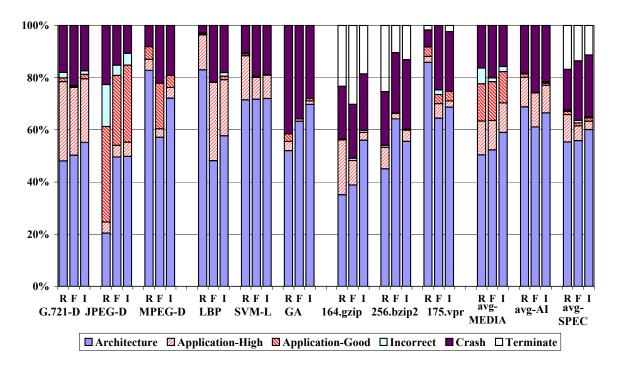

| 3.2 | Breakdown of program outcomes for architecturally visible fault injections                                                                                                                                                                                                                                                                          | 32 |

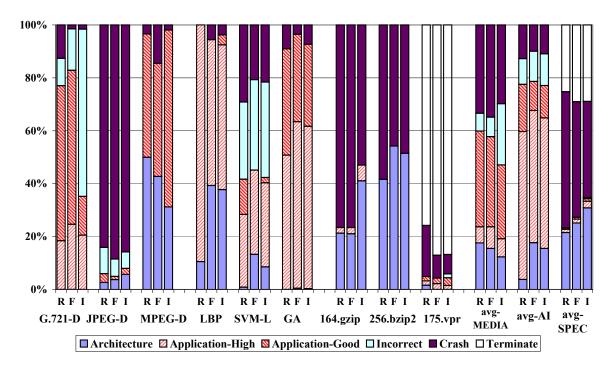

| 4.1 | Breakdown of program outcomes for lightweight recovery of crashes                                                                                                                                                                                                                                                                                   | 41 |

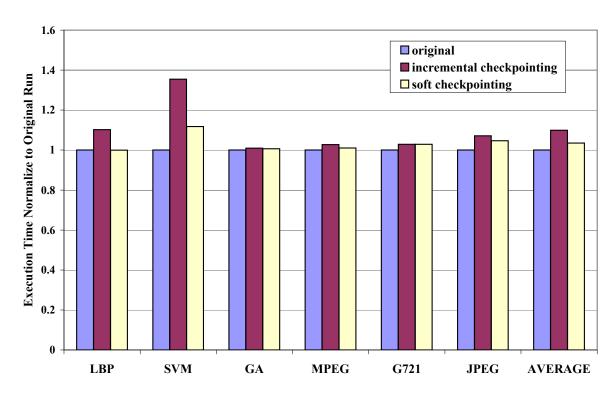

| 4.2 | Program execution time with traditional incremental checkpointing or soft checkpointing technique                                                                                                                                                                                                                                                   | 50 |

| 4.3 | Program outcomes breakdown for soft recovery of crashes                                                                                                                                                                                                                                                                                             | 52 |

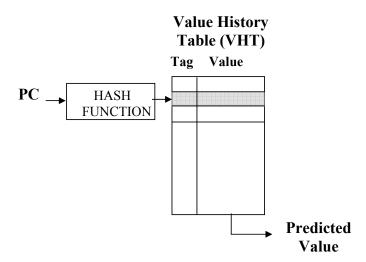

| 5.1 | Diagram of Last Value Predictor                                                                                                                                                                                                                                                                                                                     | 57 |

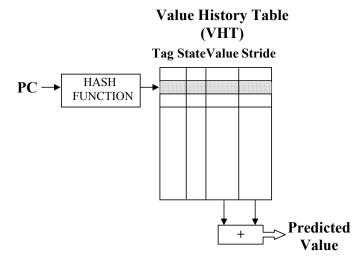

| 5.2 | Diagram of Last Value Predictor                                                                                                                                                                                                                                                                                                                     | 57 |

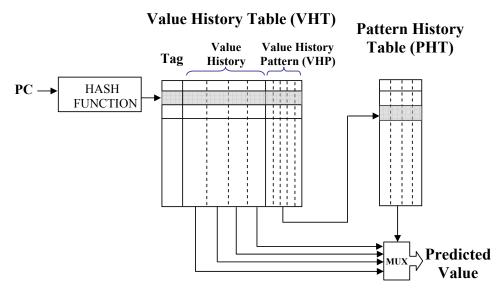

| 5.3 | Diagram of Last Value Predictor                                                                                                                                                                                                                                                                                                                     | 59 |

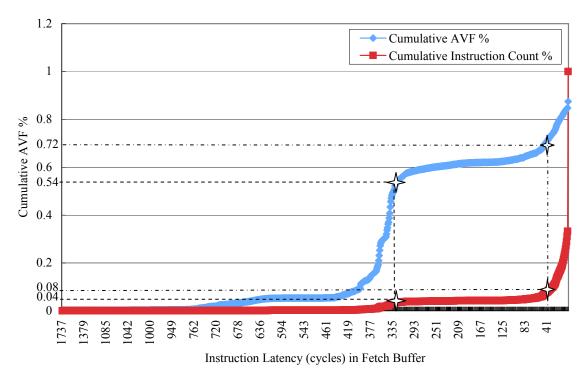

| 5.4 | Accumulative Percentage of AVF and Instruction Count in Fetch Buffer on TWOLF                                                                                                                                                                                                                                                                       | 66 |

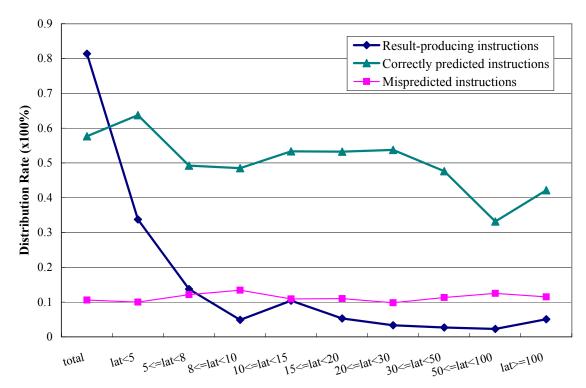

| 5.5 | Average distribution of result-producing instruction count, as well as their prediction and misprediction rate, across different latency range over all the 9 spec2000 integer benchmarks. Latency is measured from fetch to issue stage                                                                                                            | 72 |

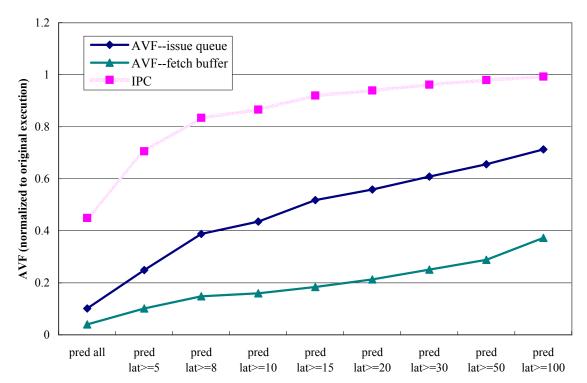

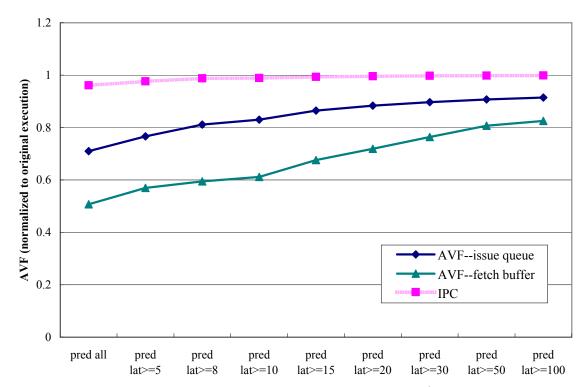

| 5.6 | Average AVF of 2 hardware structures and IPC (relative to original execution) across 9 spec2000 integer benchmarks by applying value prediction to long-latency instructions. Latency is measured from fetch to issue stage. On value misprediction, mispredicted instructions and all subsequent ones are flushed and then re-fetch and re-execute | 73 |

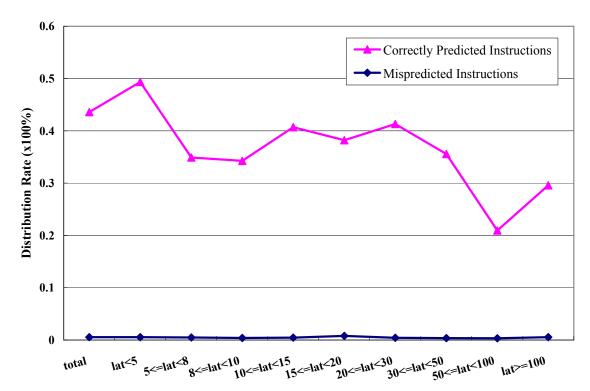

| 5.7 | Average distribution of value prediction rate—with confidence estimation—across different latency range over all the 9 spec2000 integer benchmarks. Latency is measured from fetch to issue stage                                                                                                                                                   | 76 |

| 5.8  | Average AVF of 2 hardware structures and IPC (relative to original execution) across 9 spec2000 integer benchmarks by applying value prediction to long-latency instructions. Value predictor is complemented with a separate confidence estimator. Latency is measured from fetch to issue stage. On value misprediction, mispredicted instructions and all subsequent ones are flushed and then re-fetch and re-execute                                                                                                                                                                                                                  | 77 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

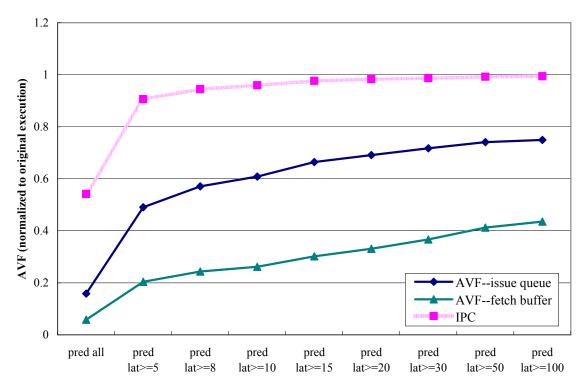

| 5.9  | Average AVF of 2 hardware structures and IPC (relative to original execution) across 9 spec2000 integer benchmarks by applying value prediction to long-latency instructions. Latency is measured from fetch to issue stage. Confidence threshold used for each prediction varies (high, medium or low threshold) according to the instruction's latency. On value misprediction, mispredicted instructions and all subsequent ones are flushed and then re-fetch and re-execute                                                                                                                                                           | 80 |

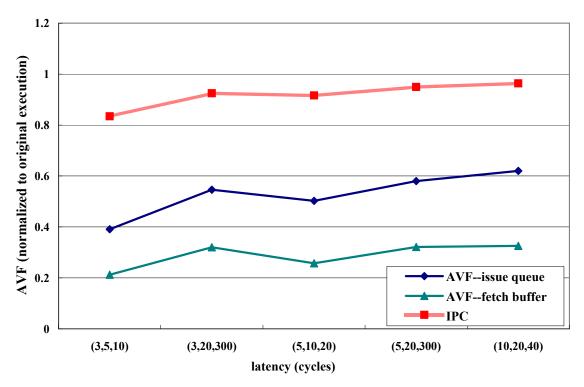

| 5.10 | Average IPC and AVF of 2 hardware structures across 9 spec2000 integer benchmarks by varying threshold of confidence estimation according to instruction latency. Each set of values marked along X-axis contains three latency thresholds, listed as lowest, medium, and highest threshold, and associated with three confidence thresholds, respectively—the three confidence thresholds are selected as described in [1]                                                                                                                                                                                                                | 81 |

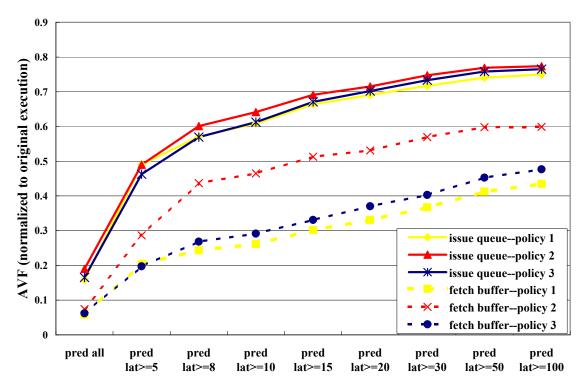

| 5.11 | Average AVF comparison of 3 policies for computing instruction latency—instructions are selected by their latency for value prediction and confidence estimation—on fetch buffer and issue queue (relative to original execution) across 9 spec2000 integer benchmarks. Policy 1 stands for latency computation from fetch to issue stage, policy 2 is for latency from dispatch to writeback, and policy 3 is for latency from fetch to writeback stage. The confidence threshold varies with instruction latency. On value misprediction, mispredicted instructions and all subsequent ones are flushed and then re-fetch and re-execute | 84 |

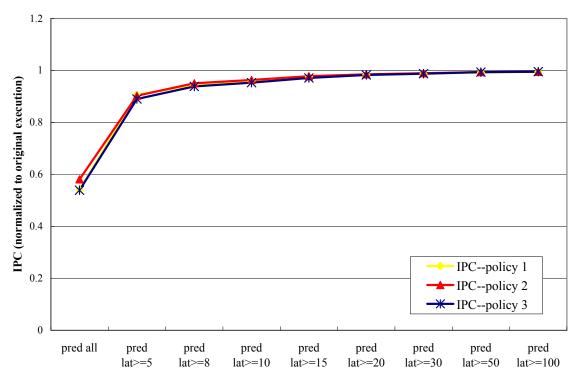

| 5.12 | Average IPC comparison of 3 policies for computing instruction latency—instructions are selected by their latency for value prediction and confidence estimation—on fetch buffer and issue queue (relative to original execution) across 9 spec2000 integer benchmarks. Policy 1 stands for latency computation from fetch to issue stage, policy 2 is for latency from dispatch to writeback, and policy 3 is for latency from fetch to writeback stage. The confidence threshold varies with instruction latency. On value misprediction, mispredicted instructions and all subsequent ones are flushed and then re-fetch and re-execute | 85 |

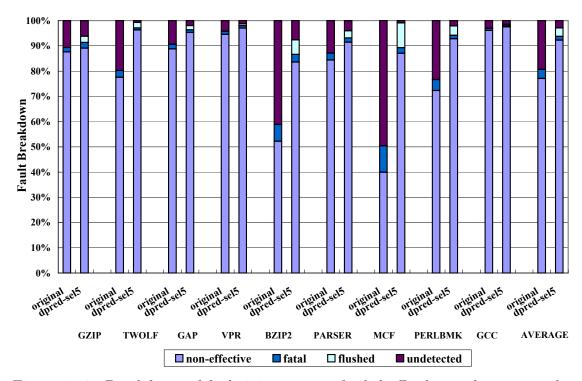

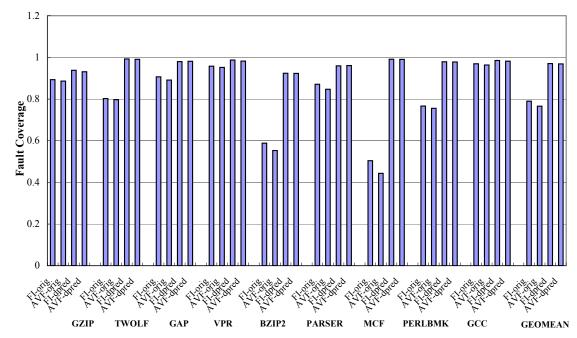

5.13 Breakdown of fault injections on fetch buffer by applying our selective value prediction technique. The minimum latency threshold for prediction is 5 cycles, measured from fetch to issue stage. Confidence threshold used for each prediction varies (high, medium or low threshold) according to the instruction's latency. On value misprediction, all the instructions in the pipeline are flushed and then re-fetch and re-execute. Categories include faults that have no architectural impact ("non-effective"), faults that cause program to crash or deadlock ('fatal"), faults that are removed during pipeline flushes before faulty instructions commit ("flushed"), and faults that are not detected by value predictor before faulty instructions commit ("undetected"). . .

89

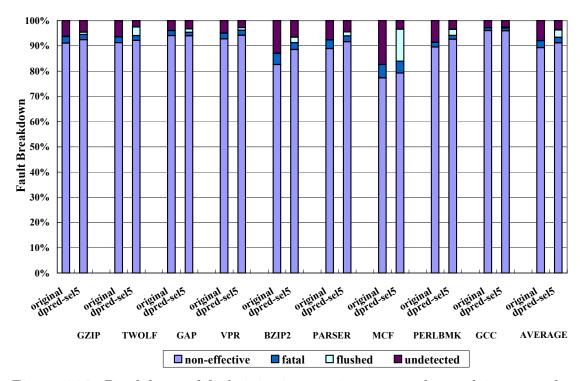

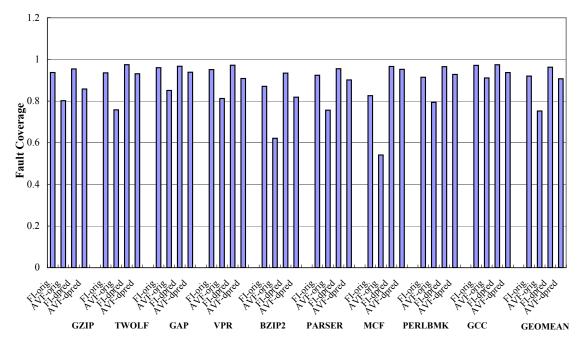

- 5.14 Breakdown of fault injections on issue queue by applying our selective value prediction technique. The minimum latency threshold for prediction is 5 cycles, measured from fetch to issue stage. Confidence threshold used for each prediction varies (high, medium or low threshold) according to the instruction's latency. On value misprediction, all the instructions in the pipeline are flushed and then re-fetch and re-execute. Categories include faults that have no architectural impact ("non-effective"), faults that cause program to crash or deadlock ('fatal"), faults that are removed during pipeline flushes before faulty instructions commit ("flushed"), and faults that are not detected by value predictor before faulty instructions commit ("undetected"). . . 91

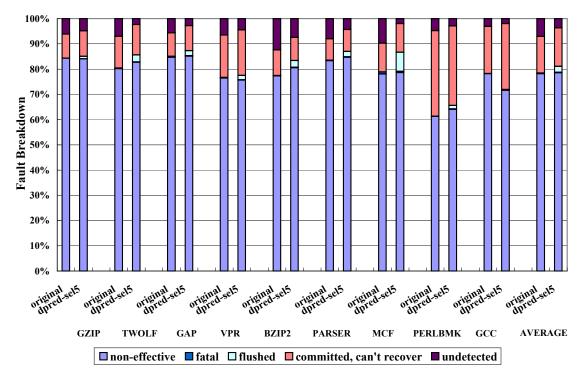

- 5.15 Breakdown of fault injections on physical register file by applying our selective value prediction technique. The minimum latency threshold for prediction is 5 cycles, measured from fetch to issue stage. Confidence threshold used for each prediction varies (high, medium or low threshold) according to the instruction's latency. On value misprediction, all the instructions in the pipeline are flushed and then re-fetch and re-execute. Categories include faults that have no architectural impact ("non-effective"), faults that cause program to crash or deadlock ('fatal"), faults that are removed during pipeline flushes before faulty instructions commit ("flushed"), faults that occur on registers while the most recent instructions updating the registers have committed ("committed, can't recover"), and faults that are not detected by value predictor before faulty instructions commit ("undetected"). 92

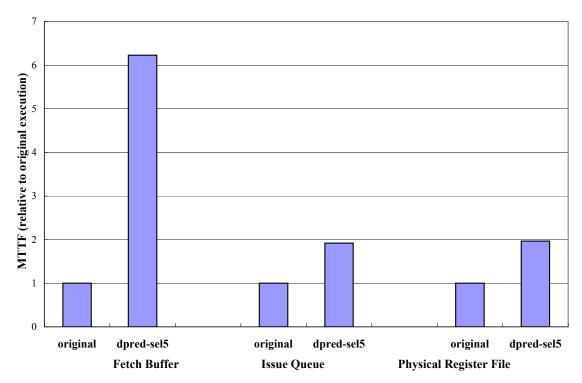

- 5.16 Average MTTF over 9 benchmarks in fetch buffer, issue queue and physical register file by applying our selective value prediction technique. The minimum latency threshold for prediction is 5 cycles, measured from fetch to issue stage. Confidence threshold used for each prediction varies (high, medium or low threshold) according to the instruction's latency. On value misprediction, all the instructions in the pipeline are flushed and then re-fetch and re-execute. . . . . . 94

| 5.17 | Fault coverage estimation for fetch buffer by fault injection experiments and AVF computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 95  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 5.18 | Fault coverage estimation for issue queue by fault injection experiments and AVF computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 96  |

| 5.19 | IPC (relative to original execution) on 9 spec2000 integer benchmarks with either value prediction, bit-invariance screening, or flushing on L2 miss implemented. On value or bit-invariance misprediction, the whole pipeline is flushed and then re-fetch after a 3-cycle penalty. On L2 miss, all the instructions following the load miss are squashed from the pipeline and they start to be re-fetch after the cache miss is resolved                                                                                                                                                                                                                                                       | . 101 |

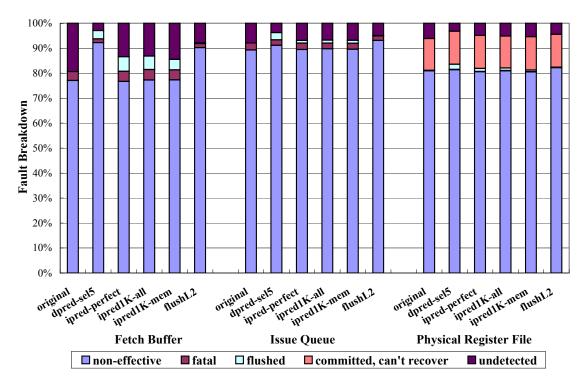

| 5.20 | Breakdown of fault outcomes on fetch buffer, issue queue and physical register file by applying value prediction, fault screening or flush-on-L2-miss techniques. Categories include faults that have no architectural impact ("non-effective"), faults that cause program to crash or deadlock ('fatal"), faults that are removed during pipeline flushes before faulty instructions commit ("flushed"), faults that occur on physical register file but the latest instruction which updates the corrupted register has committed ('committed, can't recover"), and faults that are not detected by value predictor or bit-invariance screener before faulty instructions commit ("undetected") | . 105 |

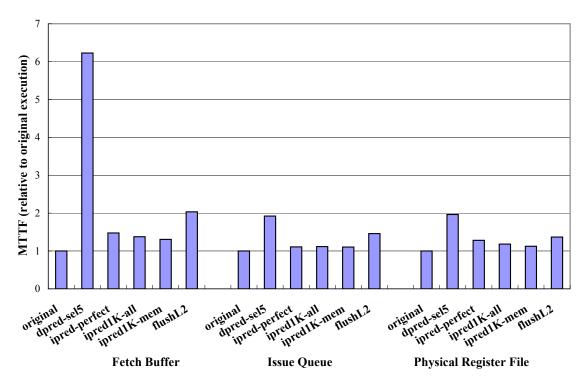

| 5.21 | Average MTTF over 9 benchmarks in fetch buffer, issue queue and physical register file by applying value prediction, fault screening, or flush-on-L2-miss techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 107 |

# List of Abbreviations

AI Artificial Intelligence

IPC Instructions per Cycle

SEU Single-Event Upset MTTF Mean Time to Failure

MTBF Mean Time between Failures MITF Mean Instructions to Failure

AVF Architectural Vulnerability Factor

### Chapter 1

#### Introduction

#### 1.1 Motivation

As CMOS technology scaling continues to enable faster transistors and lower supply voltage, tremendous improvements have been brought to microprocessor performance and power consumption. However, one of the most striking downsides of these trends is that computer systems become significantly more susceptible to hardware faults–particularly, soft errors (also known as transient faults). As intermittent faults, soft errors arise from strikes by cosmic particles and radiation from packaging materials, and are more seriously endangering system reliability as the number of on-chip transistors keeps growing exponentially. It is estimated that a chip's error rate will scale in proportion to the number of devices—*i.e.*, with Moore's Law [2].

To detect or recover from faults, there are basically two kinds of approaches. The traditional approach explicitly replicates program computation or program state, and uses the replicated program copy to detect or recover fault corruptions. For example, to detect potential faults, additional hardware structures such as processor cores, hardware contexts, and functional units [3, 4, 5, 6, 7] can be utilized, or alternatively, program code is duplicated during compiling stage [8, 9, 10], thus program computational outputs can be compared and checked for corruption. In addition, for recovering potential faults, checkpointing is usually adopted to create

additional copies of program state. Such duplication of program state can then be used for rolling back program execution once a fault is detected. Unfortunately, for both fault detection and recovery, although such approach of explicit replication can be very accurate, it usually incurs a significant cost on either performance, power, or hardware expense, etc.

Contrastingly, a relatively new approach exploits programs' inherent redundancy to improve fault tolerance, such as the technique that use symptoms like branch misprediction as indication of possible fault corruptions [11]. Another technique, which is called fault screening, identifies value space of instructions' computation, and triggers recovery if the instructions' future outputs are not within the recorded space [12]. Compared to the traditional approach, these techniques do not replicate program computation or state, hence they incur very low overhead. But they are not perfect—either the fault checkers are too sensitive and catch false positives, or they can not recover all possible faults. We call such techniques probabilistic fault tolerance. Although the probabilistic techniques cannot achieve failure-safe execution, they are still very useful for most general-purpose systems which do not need perfect fault coverage but are very sensitive to cost. For such systems, these techniques can reduce fault rate with small cost.

In this thesis, we contribute to existing probabilistic techniques by exploiting two new sources of inherent program redundancy to improve fault tolerance [13, 14]. First, we find that many programs compute much more precisely than necessary. Although traditional approaches to evaluating correctness require numerical integrity of architectural state, in many cases, it is not necessary for program state to be numerically correct. Instead, program data may tolerate some errors, or there may exist multiple values which all lead to correct program execution from the user's standpoint. This program characteristic is highly application dependent but we find it occurs frequently in application domains that involve sensing data, such as multimedia and artificial intelligence (AI) workloads. In such workloads, as long as programs' final outputs meet user's requirement, they are acceptable even if their numerical values are different from their fault-free versions. For example, some precision loss in outputs is tolerable to users if their precision requirements are lower than the datatypes supported by the programming environment or hardware architecture. Also, program solutions that are not optimal but still adequate from the user's standpoint can be accepted as well. In our study, we call such standard of correctness which is evaluated from the user or application level as application-level correctness. In contrast to the traditional definition that views correctness at the architecture level, application-level correctness is examined at a higher level of abstraction, thus allowing the existence of multiple correct outputs. Faults that cause program execution to be numerically incorrect, but still produce one of the outputs that are acceptable to users, can be tolerated.

In addition to the data redundancy at the application level, program computations can also show a high degree of redundancy–i.e., instruction streams and their output results often exhibit repeatability. Such redundancy has been traditionally exploited for increasing instruction-level parallelism (ILP) to improve program performance. One of the best examples of this is value prediction which has been widely studied for boosting program performance, but has not yet been applied to

fault tolerance. In our study, we find value prediction can be used to detect faults—prediction results can be compared against the actual computation results, with comparison mismatches indicating potential data corruptions.

In our study, we find it is beneficial to exploit both sources of program's inherent redundancy for fault tolerance enhancement. In particular, we exploit redundancy at the application level for lightweight fault-recovery mechanisms—our selective checkpointing technique only checkpoints a small part of program state while it can successfully recover a large portion or most of program crashes. We also exploit value predictability for low-cost fault detection—we take value prediction as another form of program execution, and compare the results of value prediction and actual computation to detect potential faults. In addition, we implement experiments to explore the tradeoff between performance and reliability impacts.

The following texts briefly introduce application-level fault tolerance (Section 1.1.1) and value prediction (Section 1.1.2) that have initiated our work.

# 1.1.1 Application-level Fault Tolerance

First, as we have discussed, application-level correctness enables the numerical redundancy of program state from user's standpoint. Compared to the traditional architecture-level definition of correctness, application-level correctness allows more faults to be tolerable as long as the final outputs can be accepted by users. Although such property of additional fault tolerance at the user level can be found in many important workloads, the degree of tolerating faults is application-specific.

Different programs have different characteristics, thus they may appear more or less resilient to faults. For instance, multimedia programs process human sensory and perception information and are highly fault resilient at the application level. Another example is artificial intelligence (AI) workloads, which have shown more significance recently [15]. AI is a vast research area and includes many branches such as reasoning, inference, and machine learning. As we will discuss later, AI algorithms also exhibit a great deal of fault tolerance at the application level. All these programs, e.q., multimedia and AI programs, belong to a class of computations which we call soft computations [16, 17]. Soft computations compute on inexact or approximate data. Their outputs are associated with certain forms of qualitative representations, which are usually interpreted by users. Certain faults which may change the numerical values of those outputs do not change the corresponding qualitative answers, thus are tolerable to users. Compared to soft computations, programs which requires numerically exact outputs in order to be correct, such as traditional scientific computations, may offer much less amount of fault resilience at the application level.

Although the degree of error resilience at the application level varies across different applications, we find *all* programs that we have studied exhibit some enhanced fault tolerance from user's standpoint, including those that are traditionally considered as exact computations—*e.g.*, SPECInt CPU2000. Such application-level fault tolerance could be exploited to avoid overdesign and achieve better tradeoff between system reliability and performance cost.

#### 1.1.2 Value Prediction-based Fault Detection

Prior studies have shown that program execution including its instruction and data streams exhibits another kind of redundancy—repeatability. One example of applying such inherent redundancy is value prediction, which predicts instruction results by learning their past values, thus breaks true data dependency. Unfortunately, although value prediction seems promising, its effectiveness is weakened due to its high misprediction penalty, which turns to be even worse as processor pipeline becomes deeper.

In our study, we find such predictability in computational outputs can be exploited to improve system reliability. Compared to other redundant-execution techniques, the biggest advantage of applying value prediction for result comparison and fault detection is, by exploiting program's inherent redundancy, it avoids the need for explicitly duplicating hardware or program execution, thus evades related area and power demands or performance degradation. Although value predictor itself requires some additional hardware, we find a relatively small predictor is effective in detecting faults. In addition, compared to the traditional applications of value prediction which mainly pursue performance speedup, in the field of fault tolerance, it is acceptable to trade between performance and reliability impact, which brings more chances for value prediction. For example, in case of value misprediction, we adopt the idea of flushing pipeline to try to recover fault corruptions. Although flushing degrades program performance, it improves reliability when fewer valid bits become vulnerable during flushing and re-execution. Moreover, unlike traditional

applications that require value prediction results at the early stage of pipeline, for detecting faults, value prediction can wait until the end of execution stage. All these render much flexibility for adapting value predictor design to improve fault tolerance.

In addition, by characterizing fault vulnerability at the instruction level—i.e., sorting instructions by how much they contribute to a hardware structure's fault vulnerability during program execution, we find for the hardware structures we have studied, a small portion of instructions accounts for a major fraction of program vulnerability. For example, for fetch buffer in our processor model, about 3.5% instructions contribute to 53.9% of total AVF for SPEC2000 benchmark TWOLF. Therefore, by selectively protecting such a small portion of instructions from fault corruption, the overall reliability can be enhanced greatly, while program performance is much less affected than protecting all the instructions. We apply such idea into our experiments—selectively predicting the most vulnerable instructions—to achieve better fault coverage with smaller performance impact.

To further reduce performance cost caused by value misprediction and the consequent pipeline flush, we utilize confidence estimator which allows value prediction only when there is enough confidence in its correctness. We also incorporate the fact that instructions do not contribute equally to reliability, and vary confidence threshold accordingly—instructions that are more susceptible to faults use lower confidence threshold, and instructions that are less susceptible use higher confidence threshold.

#### 1.2 Contributions

This dissertation makes the following contributions.

Complete Study on Application-Level Correctness. In this work, we present our study on exploring definitions of program correctness and their impacts on fault tolerance. To characterize program susceptibility under different correctness definitions, we implement fault injection experiments and measure how many more faults program can tolerate under application-level correctness, compared to the traditional architectural correctness. Our results show that for soft computations, about 45.8% of fault injections that lead to architecturally incorrect execution produce acceptable results under application-level correctness. For SPEC programs, a smaller portion of architecturally incorrect faults, 17.6%, produce acceptable results at the application level. Such results indicate the degree of program-level redundancy that provides additional fault tolerance.

Analysis on Sources of Application-Level Fault Tolerance. As discussed by Mukherjee et al [18] and Wang et al [19], there are sources of masking at the microarchitecture level as well as architecture level which reduce the probability that faults affect program's output. Our study exposes another level of fault masking—the application level—from user's standpoint. By analyzing program characteristics as well as how faults propagate, we identify several sources of redundancy at the application level which render additional fault tolerance.

New Fault Recovery Techniques by Exploiting Application-Level Correctness. We implement new fault recovery techniques by exploiting such additional redundancy at the application level. One technique we propose is stack checkpointing which only saves program counter, architectural register file, and stack. Our results show about 66.3% of program crashes in our multimedia and AI workloads can be successfully recovered. Another mechanism we propose identifies program state that are resilient to errors, which we call "soft" state. In our experiments, we incrementally checkpoint state that are not marked as soft state and have been updated during each checkpoint period. Our results show small additional performance cost, compared to lightweight fault recovery, while almost all crashes in soft computations are successfully recovered.

Characterizing Fault Vulnerability at the Instruction Level. In our study, we characterize instruction's vulnerability by computing the percentage of a hard-ware structure's average AVF (Architectural Vulnerability Factor) that an instruction relates to. We find that a small portion of instructions accounts for a major fraction of program vulnerability. Thus, by selectively protecting such small portion of instructions from fault corruption, the overall reliability can be enhanced greatly, while program performance is affected much less compared to fully protection.

New Fault Detection Technique by Exploiting Value Predictability. We apply value prediction for checking program computational results and consider misprediction as symptom of potential fault. In our work, we only predict instructions that have high vulnerability and squash pipeline on mispredictions to recover po-

tential faults. To reduce possible fault positives that are caused by limitation of value predictor itself, we implement confidence estimator to reduce misprediction rate. In addition, by incorporating various vulnerability at the instruction level, we propose adaptive confidence estimation—adjusting confidence threshold according to instruction's vulnerability. We analyze the impacts of value prediction and confidence estimation on both aspects of program reliability and performance.

#### 1.3 Road Map

The rest of the dissertation is organized as follows.

Chapter 2 explains the background of our study about hardware faults and fault tolerance research.

Chapter 3 analyzes application-level correctness and characterizes fault susceptibility at the application level, compared to the traditional architectural level.

In Chapter 4, we present our lightweight fault recovery as well as soft-checkpointing recovery techniques.

Chapter 5 discusses our fault detection technique with value prediction. We apply our selective value prediction (by instruction vulnerability) and adaptive confidence mechanisms to detect potential faults. We evaluate both reliability and performance impacts of our technique. In addition, we also implement fault injection experiments to compare with other related work.

Chapter 6 lists the prior work related to our study, covering soft computation, fault susceptibility characterization, analysis of fault-tolerance sources, fault detection and recovery techniques.

Finally, Chapter 7 concludes the dissertation and suggests the future research directions.

# Chapter 2

## Background

#### 2.1 Hardware Faults

Hardware faults such as soft errors, lifetime reliability and process variation problems, have always posed threats to normal functionality of semiconductor-based digital systems. Such problems are becoming more serious as scaling in device size, operating voltages and design margins continues. The following describes the nature of these types of faults.

Transient Fault A transient fault, or soft error, is a signal or datum that is wrong, but is not caused by hardware defect—mistake in design or construction, or broken component. It is not a permanent failure—the occurrence of soft errors does not cause permanent damage to hardware, and there is no implication on reliability reduction of the system itself. On the contrary, it is temporary and intermittent fault, but can still corrupt normal program execution.

Soft errors are mainly due to particle strikes such as alpha particles emitted by decaying radioactive impurities in packaging and interconnect materials, energetic neutrons and protons from cosmic rays, or thermal neutrons. When particles travel through a semiconductor device, they release electron-hole pairs which can be absorbed by transistor source and drain nodes and disturb the distribution of electrons there. If the disturbance is large enough, the state of a logic device—such as an SRAM cell, a latch or a gate—can be changed from a 0 to a 1 or vice versa.

Soft errors have become a more challenging problem for future microprocessor design. While the raw error rate per logic device remains small, a processor's error rate grows proportional to the number of transistors per chip which has kept scaling with the rapid technology development [2].

Usually, soft errors are localized to a very small area of a chip, and only affect the state of one logic node. This is known as a Single-Even Upset (SEU). We mainly study this form of fault in our work.

Lifetime Reliability System lifetime reliability is impacted by wear-out based failures, which are mainly caused by migration of metal atoms due to electro- or mechanical stress, gate oxide wear down, or damage accumulated by thermal cycling [20, 21].

Device scaling results in increased power density, and consequently, temperature, which directly affect processor lifetime reliability. For example, the main failure mechanisms including atom migration, gate oxide wear down and thermal cycling, are adversely affected by increases in temperature, while the decreasing feature size of interconnects accelerates failure rate due to electro-migration.

**Process Variation** Process variation is mainly caused by fluctuations in dopant concentrations and device channel dimensions, which cause deviations in the manufactured properties of the chip such as transistor size, threshold voltage or driving capability, etc., thus affecting stability of circuit blocks [22].

As devices scale with decreasing dimensions and growing transistor density, device variation as well as the probability of deviations in longer critical path delay increase, which will significantly affect performance, and more severely, compromises reliability.

#### 2.2 Fault Tolerance

Current fault tolerance research focuses primarily on characterizing fault susceptibility or developing fault detection and recovery techniques. This section discusses the nature of research in these areas.

# 2.2.1 Fault Susceptibility Characterization

To characterize a device's susceptibility to faults, it is necessary to understand how faults propagate in circuits after they hit devices. Traditionally, soft errors were tackled within the context of memory cells, for which error detection and correction circuits are widely used for protection. Combinational logic circuits, on the other hand, have been found to be less susceptible to SEU due to the naturally occurring masking effects: electrical masking, logical masking, and temporal (or timing-window) masking. In particular, electrical masking attenuates affected signal by the electrical properties of gates on the propagation path such that the resulting pulse is of insufficient magnitude to be reliably latched; logical masking occurs when the propagation of an SEU is blocked from reaching an output latch because off-path gate inputs prevent a logical transition of that gate's output; and temporal masking

occurs when the erroneous pulse reaches an output latch, but it does not occur close enough to when the latch actually samples its input.

Although these masking effects reduce the probability of soft errors to be manifested, they are diminishing as device feature size decreases and circuits adopt higher operating frequencies. As a result, recently more and more work has been devoted to study the characteristics of fault susceptibility by building proper models or implementing fault injection experiments, etc.

In addition to masking effects at the circuit level, there exist other sources of masking such as those proposed by Mukherjee et al [18]. Mukherjee et al identified the effects of microarchitecture-level masking which come from mispeculated instructions, predictor structure bits, and microarchitecturally idle bits. They also identified masking effects at the architectural level—for example, faults on NOP instructions, performance-enhancing instructions, dynamically dead code, and logically masked instructions. Faults on such microarchitecture structure and architectural instructions do not affect program outputs.

To calculate fault susceptibility, there exist various metrics to specify Soft error rate (SER). SER is the rate at which a device or system encounters or is predicted to encounter soft errors. It is typically expressed as either the number of failures-in-time (FIT), or mean-time-between-failures (MTBF). The unit adopted for quantifying failures in time is called FIT, equivalent to 1 error per billion hours of device operation. MTBF is usually given in years of device operation. To put it in perspective, 1 year MTBF is equal to approximately 114,077 FIT.

MTBF can be further expressed as mean-time-to-failure (MTTF) and mean-

time-to-repair (MTTR). Generally MTTR is ignorable compared to MTBF. Also considering the fact that usually processor vendors have no control over factors related to MTTR, MTTF is more frequently used for featuring fault susceptibility.

#### 2.2.2 Fault Detection

Fault Detection is the process of discovering if a fault has occurred. Several schemes exist to achieve fault detection. For example, error detection codes are often used in data storage media, in which extra bits, referred to as check bits, are utilized for storing information that is derived from data to be protected. Fault can be detected by re-generating the check bits and comparing with the old check bits—a mismatch on comparison indicates the occurrence of a fault. Examples of check bits include parity bits, checksum, etc.

For more comprehensive comparison, dual modular redundancy (DMR) can be employed at various levels to enable fault detection. DMR has duplicated elements which work in parallel—the duplicated elements can range from replicated pipelines within the same die to separate processors. At any time, all the replications of each element should be in the same state: the same inputs are provided to each element, and the same outputs are expected. To detect faults, the outputs of the replications are compared using a voting circuit. A fault is detected when mismatch on output comparison is captured. However, other methods are needed in addition to DMR for recovery.

#### 2.2.3 Fault Recovery

Fault recovery is the process of limiting fault propagation and enabling the service which restores system to an acceptable state. It can be accomplished in two general ways. The first mechanism is forward-error recovery, in which enough redundancy exists in the system to determine the correct operation. For example, triple modular redundancy (TMR) utilizes three systems which perform the same functions. Results of the three composing units are processed by a voting system to produce a single output. Usually the voter is much more reliable than other TMR components. When any one of the three systems fails—its result is different from those produced by the other two systems. The remaining systems can correct and mask the fault.

Another recovery mechanism is backwards-error recovery, which creates checkpoints of system state and rollback program execution when an error is detected.

Checkpointing can be implemented by operating system, or at the user level, incorporating special checkpointing mechanism with the application program. It is

performed at a periodic interval by storing checkpoints to disk. If a failure occurs

which causes the application to be terminated prematurely, the stored (most-recent)

checkpoint can be used to restart the application—with the loss of computation during a checkpoint interval.

To checkpoint an application, its state including values in memory, CPU registers, and the state of the operating system such as the file system, have to be saved.

Typically, the memory state can be divided into four parts: executable code, global

variables, heap and stack. The global variables, heap and stack need to be stored in checkpoint. As for the executable code, because it is usually unchanged since the beginning of execution, it can be restored from the program's executable file and thus does not need to be saved every time.

To reduce checkpoint size as well as runtime overhead, incremental checkpointing uses page protection hardware to identify and only save the portion of pages that have been updated since the previous checkpoint. Our recovery mechanism, which is to be described in Section 4, is based on incremental checkpointing.

# 2.2.4 Partial Fault Detection/Recovery

Traditional fault-tolerance techniques aim at achieving perfect coverage—detecting and recovering from all possible latent faults. However, for most systems such as desktop computers or commodity servers, such high reliability is not necessary. On the contrary, for those systems, performance and hardware cost appear to be more crucial for customers. Thus recently, a lot of work has been committed to reducing fault rate with low performance or hardware cost.

# Chapter 3

## Application-level Fault Susceptibility

In this chapter, we present our work on characterizing programs' fault susceptibility at the application level. We first discuss definitions of application-level correctness (Section 3.1). Then we report our experimental methodology as well as susceptibility results (Section 3.2). Lastly, we discuss various sources of fault tolerance at the application level (Section 3.3).

## 3.1 Application-Level Correctness

This section presents our study on application-level correctness. We first discuss qualitative program outputs (Section 3.1.1). Then, we present various correctness definitions which are used in our fault susceptibility experiments (Section 3.1.2).

# 3.1.1 Qualitative Program Outputs

Traditionally, program outputs are defined as all the numerical values that are stored to memory at program completion. And program's execution is said to be correct as long as all the output values are the same as those obtained by a fault-free execution. However, in many cases, only a small portion of the final values need to be provided to users. Thus, state that are invisible to users do not need to be correct. More interestingly, in a lot of cases, even the results that are

presented to users do not need to be exact either. This commonly occurs in programs computing results that are qualitatively interpreted by the user, such as multimedia workloads which process human sensory information. In these programs, different numerical results can lead to the same qualitative interpretation. Another example is AI processing that applies artificial intelligence algorithms for reasoning, inference, and learning, etc. These algorithms are approximate in nature, and errors in the numerical answers may not affect the programs on drawing further conclusions (i.e., qualitative answers). For example, results of learning algorithms may be used for classifying new datasets. Thus, numerically different results from learning could be qualitatively correct if they lead to the same classification answers.

Not only soft computations like multimedia and AI programs have qualitative outputs, but other general computations may also exhibit such properties. For instance, many programs are designed to achieve the best performance, such as a compression algorithm that tries to generate an output file as compact as possible. However, the ultimate goal is to faithfully convert the compressed file back to the original data. Hence, even if the compression process is not efficient and produces a bigger compressed output, the user may still accept it if it leads to the same correct result after decompression.

Furthermore, even qualitative answers can vary if they are acceptable at the user(i.e., application) level. Considering multimedia applications again, outputs which result in similar, although not the same, qualitative interpretation can be deemed as correct as long as users are satisfied. The amount of acceptable error in the output depends on users. This allows correctness to cease to be simply black or

white; instead, we can speak of a degree of correctness determined by the amount of tolerable error.

#### 3.1.2 Correctness Definitions

Existing definitions of program correctness can be expanded by considering solution quality interpreted at the user level. Below are possible correctness definitions, listed in decreasing strictness.

- I. Architectural state is numerically correct on a per-cycle (or per multiple-cycle) basis.

- II. Output state (*i.e.*, architectural state visible after program completion) is numerically correct.

- III. Output state is qualitatively correct with high fidelity.

- IV. Output state is qualitatively correct with acceptable fidelity.

Definitions I and II are two main traditional approaches used in fault tolerance research. They require program state, either intermediate or final results, to be numerically exact compared to fault-free execution. Unlike the first two architecture-level definitions, the remaining ones, definitions III and IV, are at the application level, thus they are less strict. Both correctness definitions apply to programs producing results that have a higher qualitative interpretation. More specifically, definition III requires outputs to be the same or very similar to the baseline output (i.e., high fidelity). The baseline output is defined as the result obtained from fault-free

execution of a program. In other words, answers satisfying definition III do not have noticeable quality degradation. Definition IV requires answers to have relatively good fidelity compared to baseline solutions. Compared to definition III, definition IV allows more tolerance of reduced answer quality.

As we have discussed in Section 3.1.1, programs with qualitative answers exhibit more error resilience since their results are not directly tied to precise numerical values. Errors in the numerical results may not be noticeable, or they may not significantly impact qualitative answers. Furthermore, under application-level correctness definitions, *i.e.*, definitions III and IV, the output acceptability can be customized by users by varying the minimum fidelity necessary for a program output to be "acceptable." Hence, users can accept more program outputs as "correct" by sacrificing fidelity. Generally, the more tolerable the qualitative answer is to error, the more reliable the program appears to be. As we will see in Section 3.2, this provides users with a great opportunity to tradeoff solution quality for fault tolerance.

# 3.2 Fault Susceptibility Experiments

This section discusses the impact of application-level correctness on fault susceptibility. We conduct experiments to quantify how much more fault resilient programs appear to be under application-level correctness compared to traditional architecture-level correctness. We first present our experimental methodology in Section 3.2.1, then discuss our results in Section 3.2.2.

### 3.2.1 Experimental Methodology

To analyze program fault susceptibility under different correctness definitions which have been described in Section 3.1.2, we perform statistical fault injection experiments on selected benchmarks and analyze the effects of faults on a microarchitecture model. We also assume a Single Event Upset, or SEU, fault model, throughout our experiments. In each fault injection experiment, a random single bit flip fault is injected into the execution of one of the benchmarks. In order to capture architectural effects of the faults more efficiently, we adopt the methodology introduced by Reis et. al. [23] which uses a two-phase simulation technique. Similar to [23], during the first fault injection phase, we inject faults into a detailed architectural simulator. Each time one fault is injected, we continue simulation until the effects of the fault have been completely manifested in architectural state. Then, we checkpoint the architectural effects, and continue to inject another fault. After we have compiled the information across all the fault injections, in the second phase, we use a simple functional simulator and replay each fault injection experiment that has been recorded. More specifically, for each fault, we resume simulation with its corresponding checkpoint, thus the architectural effects of the fault will keep propagating while the program executes. In each simulation trial, we try to run the program to completion. If the program does not crash, we evaluate its outputs under both architecture- and application-level correctness. Note in our experiments, we only evaluate program correctness with definitions II, III and IV introduced in Section 3.1.2.

| Processor Parameters                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bandwidth Queue size Rename register / ROB Functional unit Memory port | 8-Fetch, 8-Issue, 8-Commit<br>64-IFQ, 40-Int IQ, 30-FP IQ, 128-LSQ<br>128-Int, 128-FP / 256 entry<br>8-Int Add, 4-Int Mul/Div, 4-FP Add, 2-FP Mul/Dir<br>4-Mem Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Branch Predictor Parameters                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Branch Predictor<br>Meta Table / BTB / RAS Size                        | Hybrid 8192-entry gshare/2048-entry Bimodal<br>8192 / 2048 4-way / 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Memory Parameters                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| IL1 config DL1 config UL2 config Mem config                            | DL1 config UL2 config  64kbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 2 way, 1 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 4 way, 20 cycle latent 1Mkbyte, 64byte block size, 64byte block |  |  |  |  |

Table 3.1: Parameter settings for the detailed architectural model into which we inject faults.