**ABSTRACT**

Title of Document: LEAD-FREE ELECTRONICS USE AND

REPAIR DYNAMIC SIMULATION

Andrew Charles Chaloupka, Master of Science,

2009

Directed By: Dr. Peter Sandborn, Professor of Mechanical

Engineering

The conversion from tin-lead to lead-free electronics has increased concern amongst engineers about the reliability of electronic assemblies that have been repaired

with lead-free parts. Program-level management is often told by engineers that the "sky

is falling" due to an unforeseen technical issue but is not moved to action without the

occurrence of an unfortunate incident or a quantitative business case. Unfortunately,

engineers often do not have the tools to articulate the risks and impacts that they foresee

in terms that management understands such as cost and availability.

In order to communicate the impact of the tin-lead to lead-free electronics

conversion in terms of cost and availability, a simulation of fielded electronic systems to

and through a repair facility was created. Systems manufactured with tin-lead parts (or a

mixture of tin-lead and lead-free parts) that potentially have to be repaired with a mixture

of tin-lead and lead-free parts are modeled. The model includes the effects of repair

prioritization, multiple possible failure mechanisms, no-fault-founds, and un-repairable

units. These effects are used to quantify and demonstrate the system- and enterpriselevel risks posed by the tin-lead to lead-free conversion issue.

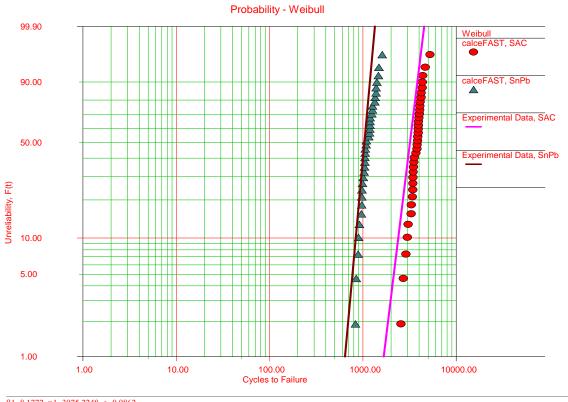

Example analyses were performed on electronic assemblies that use SAC (tin, silver and copper) and tin-lead solder using a repair process modeled after a NSWC Crane Aviation Repair Process. The components considered consisted of SMT passive, BGA, CSP and TSOP packaged parts that experienced three different thermal cycling profiles. The impact of the conversion from tin-lead to SAC for the example system is studied and the cost and availability impacts were quantified.

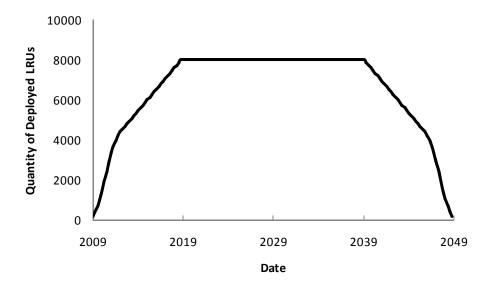

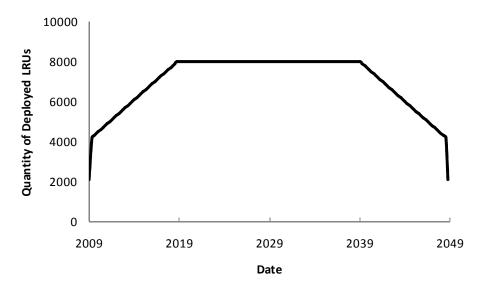

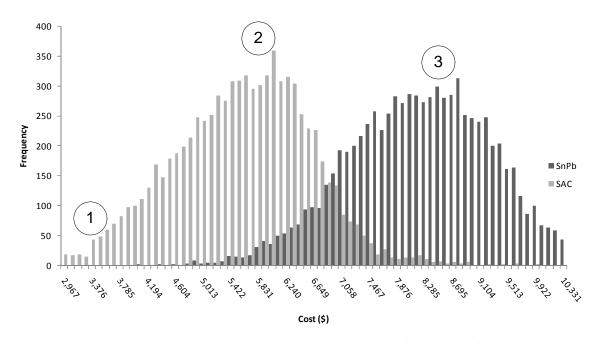

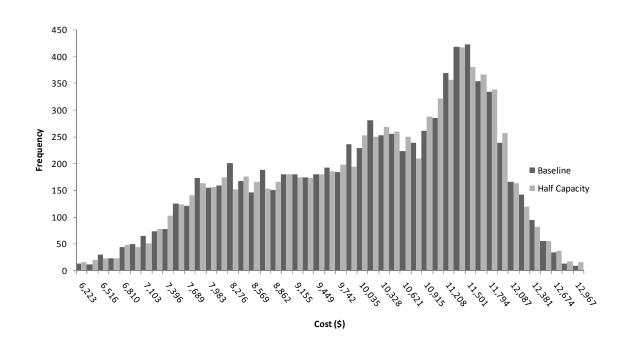

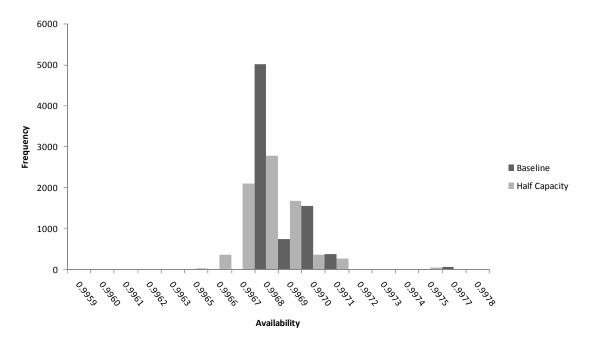

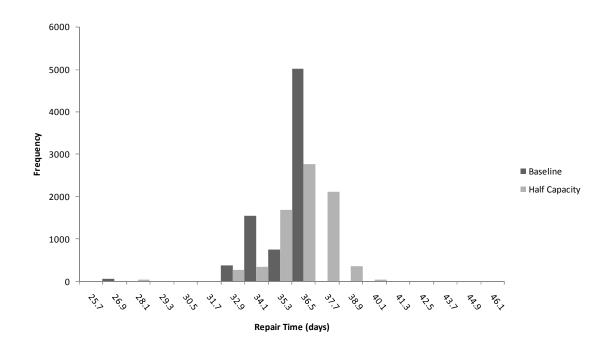

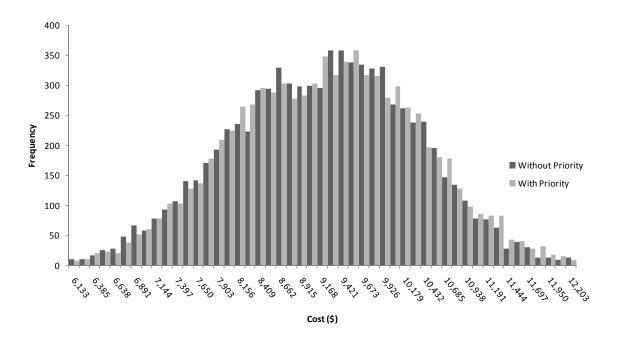

The case studies revealed that when exposed to usage profiles characteristic of consumer electronics, low maximum and mean thermal cycling temperatures with long dwell times, SAC exhibited significantly reduced repair costs when compared to tin-lead. For usage profiles characteristic of aerospace and high performance applications, high maximum and mean thermal cycling temperatures with short dwell times, SAC exhibited significantly increased repair costs when compared to tin-lead. It was also found that the NSWC Crane Aviation Repair Process (as modeled) is more than capable of handling a population of 8,000 LRUs even when experiencing a 50% reduction in capacity. As a result, prioritizing the repair of LRUs had no significant impact on the cost or availability metrics for the cases considered. In addition, the rate of LRU field deployment had no impact when using the NSWC Crane Aviation Repair Process.

### LEAD-FREE ELECTRONICS USE AND REPAIR DYNAMIC SIMULATION

By

Andrew Charles Chaloupka

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Master of Science 2009

Advisory Committee: Professor Peter Sandborn, Chair Associate Professor Patrick McCluskey Associate Professor Jeffery Herrmann © Copyright by Andrew Charles Chaloupka 2009

### Dedication

This thesis is dedicated to my parents Roland and Linda, my sister Tracy, my service dog in training, and my officemates in graduate school.

My mother has supported me through every endeavor I have ventured. Her motivation and dedication to her career has provided me with a strong model of how to operate both professionally and efficiently in my own work.

My father has strongly influenced me with his engineering background to be the best and most creative in my work. He imbues the fortitude to never settle for anything but the best.

My sister Tracy has always been there to offer support and comic relief. Her continued determination in her career has been an enduring example growing up.

Although it may seem as an unconventional dedication, my service dog in training, Maya, has been an over arching support over the past seven months. Her ability to show unconditional love, her willingness to stay by my side morning and night either in my office or at home, has fueled my strength and stamina to push through this thesis in just under one calendar year.

I would also like to dedicate this to my officemates in graduate school. With their help I have experienced what it means to be a Maryland Terrapin.

### Acknowledgements

First and foremost, I would like to thank my advisor, Dr. Peter Sandborn for his continued support in this thesis. His guidance has allowed me to successfully complete my research in a limited amount of time.

I would also like to thank Dr. McCluskey and Dr. Herrmann for being part of my defense committee and for inspiring me to be a better decision maker.

I would like to acknowledge the contributions of several individuals to this work: first to Bill Russell at Raytheon and Denny Fritz at SAIC whose vision and guidance proved invaluable throughout the course of my research. I would also like to thank the Naval Surface Warfare Center at Crane Indiana for providing data and technical feedback. Finally, I wish to acknowledge the CALCE Electronic Products and Systems Consortium at the University of Maryland for funding this work.

## Table of Contents

| Dedication                                                              | ii  |

|-------------------------------------------------------------------------|-----|

| Acknowledgements                                                        | iii |

| List of Tables                                                          | vi  |

| List of Figures                                                         | vii |

| Chapter 1: Introduction                                                 | 1   |

| 1.1 Making a Case to Management                                         | 2   |

| 1.2 Lead-Free Solder                                                    | 3   |

| 1.2.1 The Conversion to Lead-Free                                       | 4   |

| 1.3 Repair Culture Concerns                                             | 5   |

| 1.4 Thesis Objectives and Tasks                                         | 6   |

| Chapter 2: Model Development                                            | 8   |

| 2.1 Modeling Repair Processes                                           |     |

| 2.1.1 Modeling Using Discrete Simulation                                | 11  |

| 2.1.2 Advantages of a Simulation                                        | 12  |

| 2.2 Introduction to Modeling Repair Using Discrete Event Simulation     | 13  |

| 2.2.1 Mode of Execution                                                 | 14  |

| 2.2.2 Process Modeling (Process Flow and Steps)                         | 15  |

| 2.2.3 Conversion of Non-Time Based Distributions                        | 18  |

| 2.2.4 Sampling                                                          | 19  |

| 2.3 The Modeling Process                                                | 20  |

| 2.3.1 Modeling the Queues                                               | 21  |

| 2.3.2 Adding Spares/Repairing Process                                   | 28  |

| 2.3.3 Early Retirement                                                  | 29  |

| 2.3.4 Branching                                                         |     |

| 2.3.5 How LRUs Get in and Out of the Repair Process Flow                | 31  |

| 2.3.6 Time Step Selection and Management                                | 31  |

| 2.3.7 The Impact of Low Capacity Process Steps on the Total Repair Time | 33  |

| 2.4 Outputs                                                             |     |

| 2.4.1 Average Cost per LRU                                              | 35  |

| 2.4.2 Average Repair Time                                               | 36  |

| 2.4.3 Availability                                                      | 37  |

| 2.5 Model Summary                                                       | 38  |

| Chapter 3: Model Test Case                                              | 40  |

| 3.1 Test Case Development                                               |     |

| 3.1.1 LRU Introduction and Retirement Schedules                         | 40  |

| 3.1.2 LRU Operational Profile                                           |     |

| 3.1.3 Developing the Failure Mechanism Distributions                    | 43  |

| 3.1.4 Repair Process                                                    |     |

| 3.2 Analysis Results                                                    |     |

| 3.2.1 Test A Results                                                    | 59  |

| 3.2.2 Test B Results                                                    |     |

| 3.2.3 Test C Results                                                    |     |

| 3.2.4 Test D Results                                                    |     |

| 3.2.5 Test E Results                                                    | 73  |

| 3.2.6 Test F Results                                     | 76  |

|----------------------------------------------------------|-----|

| 3.2.7 Test G Results                                     | 78  |

| 3.2.7 Test H Results                                     | 80  |

| 3.2.8 Test I Results.                                    | 82  |

| Chapter 4: Conclusions                                   | 85  |

| 4.1 Conclusions                                          |     |

| 4.2 Contributions.                                       | 86  |

| 4.3 Future Work                                          | 87  |

| 4.3.1 Throwaway Applications                             | 87  |

| 4.3.2 Process Step Durations                             |     |

| 4.3.3 Multiple Instances of a Package Type on a Test LRU | 89  |

| 4.3.4 Multiple Failures on the Same Date                 |     |

| 4.3.5 Vibration Failure Mechanism                        | 89  |

| 4.3.6 Maintenance Data Integration                       | 90  |

| 4.3.7 Continuation of Damage During the Repair Process   |     |

| Appendix A – Simulation Details                          |     |

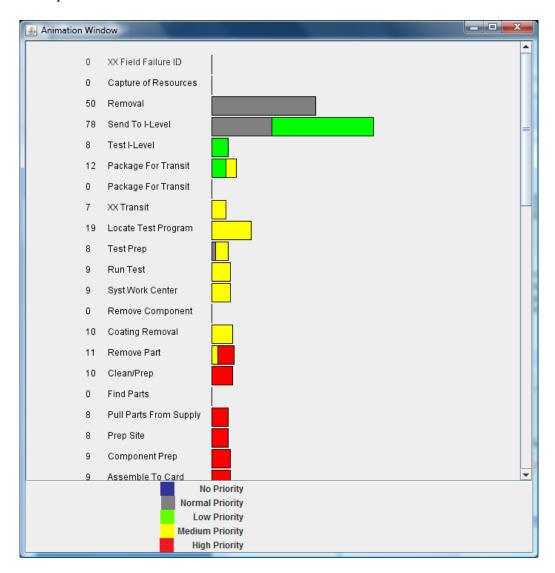

| Repair Process Step Animation                            | 101 |

| Appendix B – calceFAST Failure Mechanism Reference       |     |

| First Order Thermal Fatigue Model For Leadless Packages  |     |

| Glossary                                                 |     |

| References                                               |     |

## List of Tables

| Table 2.1: Process Step "Field Failure Identification"                       | 17      |

|------------------------------------------------------------------------------|---------|

| Table 2.2: Example Process Step Notation                                     | 24      |

| Table 3.1: Temperature Cycling Requirements, Mandated and Preferred Test Par | ameters |

| within Mandated Conditions [GEIA 2008]                                       | 43      |

| Table 3.2: Thermal Cycling Cases 1-3 Used to Compare Solder Reliability      | 48      |

| Table 3.3: LCC Attributes Defined in calceFAST                               | 48      |

| Solders                                                                      | 49      |

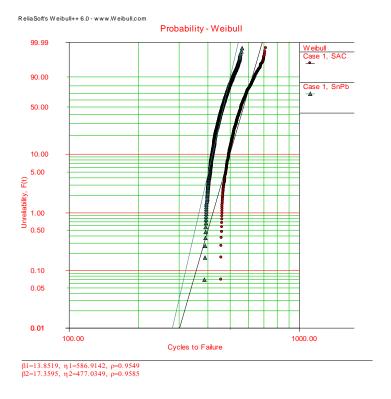

| Table 3.4: Weibull Parameters, LCC Package, for Thermal Cases 1-3            | 50      |

| Table 3.5: BGA Attributes Defined in calceFAST                               | 51      |

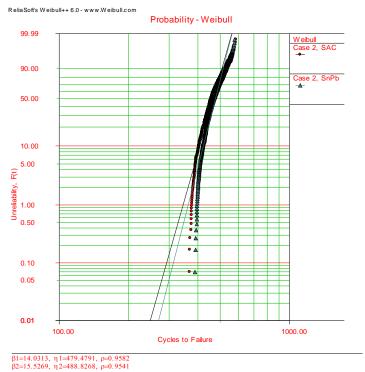

| Table 3.6: Weibull Parameters, BGA Package, for Thermal Cases 1-3            |         |

| Table 3.7: BGA Attributes Defined in calceFAST                               | 53      |

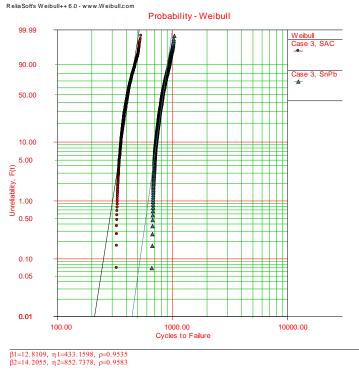

| Table 3.8: Weibull Parameters, CGA Package, for Thermal Cases 1-3            | 56      |

| Table 3.9: Baseline NSWC Repair Process                                      | 58      |

| Table 3.10: Parameters for Thermal Cycling Case 1                            | 59      |

| Table 3.11: Test A Metrics                                                   | 63      |

| Table 3.12: Parameters for Thermal Cycling Case 2                            | 66      |

| Table 3.13: Test B Metrics.                                                  | 68      |

| Table 3.14: Parameters for Thermal Cycling Case 3                            | 69      |

| Table 3.15: Test C Metrics.                                                  | 71      |

| Table 3.16: Test D Metrics                                                   | 73      |

| Table 3.17: Case E Metrics                                                   | 76      |

| Table 3.18: Case F Metrics                                                   | 78      |

| Table 3.19: Case G Metrics                                                   | 79      |

| Table 3.20: Case H Metrics                                                   | 82      |

| Table 3.21: Case I Metrics                                                   | 84      |

| Table 4.1: Case Study Results, Tests A-I, Percent Differences                | 85      |

# List of Figures

| Figure 2.1: Breakdown of a Process Steps Queue into the Repair Section and Waiting   |      |

|--------------------------------------------------------------------------------------|------|

| Pool                                                                                 | . 16 |

| Figure 2.2: First Time Step of Field Failure Identification Process Step             | . 17 |

| Figure 2.3: Second Time Step of Field Failure Identification Process Step            | . 17 |

| Figure 2.5: LRU Flow through the model from Fielding to End of Support               | . 21 |

| Figure 2.6: Priority Levels and Relation to Mission Criticalness                     |      |

| Figure 2.7: Impact of Priority on Total Repair Time                                  |      |

| Figure 2.8: No Priority Sorting                                                      | . 28 |

| Figure 2.9: Priority Sorting                                                         | . 28 |

| Figure 2.10: Example of Original to Spare LRU Relationship                           | . 30 |

| Figure 2.11: Implementation of Unique and Independent Repair Processes               |      |

| Figure 2.12: Example Process Steps with different durations                          | . 32 |

| Figure 2.13: Example Process Steps                                                   | . 34 |

| Figure 2.14: Total Repair Time (hours) for LRUs 1-40 in the example process shown in | n    |

|                                                                                      | . 35 |

| Figure 2.15: Usage Procedure for the Model                                           | . 39 |

| Figure 3.1: Baseline Deployment Schedule                                             | . 41 |

| Figure 3.2: Medium Deployment Schedule                                               | . 41 |

| Figure 3.3: Rapid Deployment Schedule                                                | . 42 |

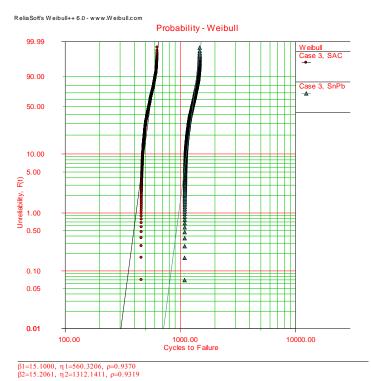

| Figure 3.4: Comparing Data Generated Using calceFAST to Experimental TTF Data        | . 45 |

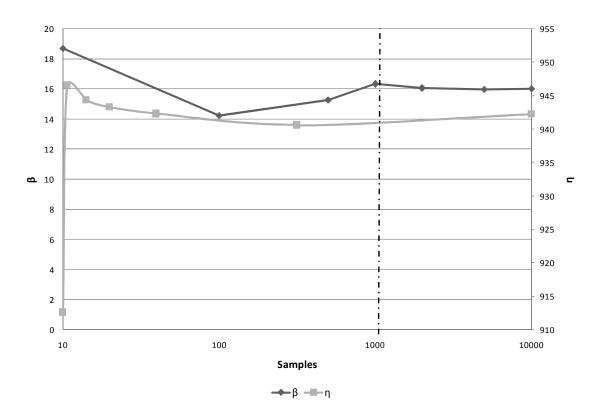

| Figure 3.5: Convergence of Weibull Parameters by Increasing Sample Size              | . 46 |

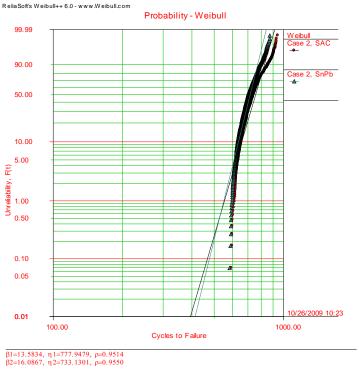

| Figure 3.6: Case 1, Weibull Plot of LCC Package Cycles to Failure for SnPb and SAC   |      |

| Solders                                                                              | . 49 |

| Figure 3.7: Case 2, Weibull Plot of LCC Package Cycles to Failure for SnPb and SAC   |      |

| Solders                                                                              | . 49 |

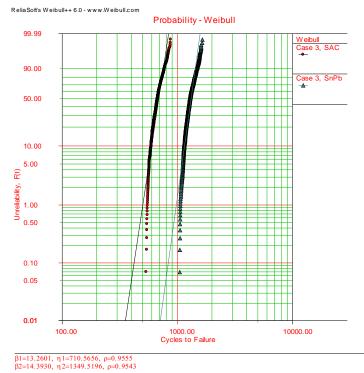

| Figure 3.8: Case 3, Weibull Plot of LCC Package Cycles to Failure for Both SnPb and  |      |

| SAC Solders                                                                          | . 50 |

| Figure 3.9: Case 1, Weibull Plot of BGA Package Cycles to Failure for Both SnPb and  | ļ    |

| ~                                                                                    | . 51 |

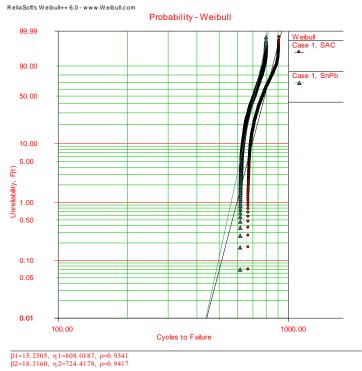

| Figure 3.10: Case 2, Weibull Plot of BGA Package Cycles to Failure for Both SnPb an  |      |

| SAC Solders                                                                          | . 52 |

| Figure 3.11: Case 3, Weibull Plot of LCC Package Cycles to Failure for Both SnPb and |      |

| SAC Solders                                                                          | . 52 |

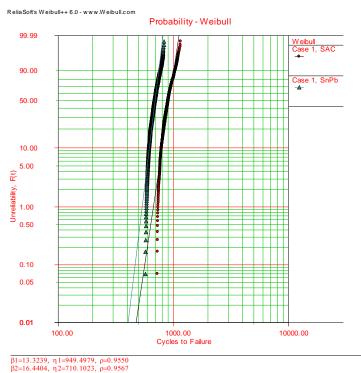

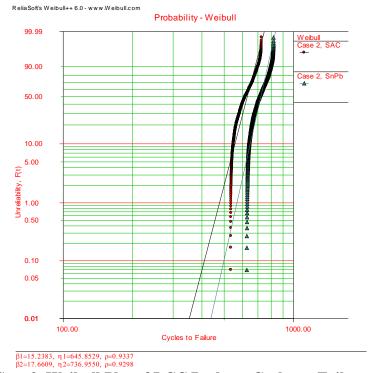

| Figure 3.12: Case 1, Weibull Plot of LCC Package Cycles to Failure for Both SnPb and |      |

| SAC Solders                                                                          |      |

| Figure 3.13: Case 2, Weibull Plot of LCC Package Cycles to Failure for Both SnPb and |      |

| SAC Solders                                                                          |      |

| Figure 3.14: Case 3, Weibull Plot of LCC Package Cycles to Failure for Both SnPb and |      |

| SAC Solders                                                                          |      |

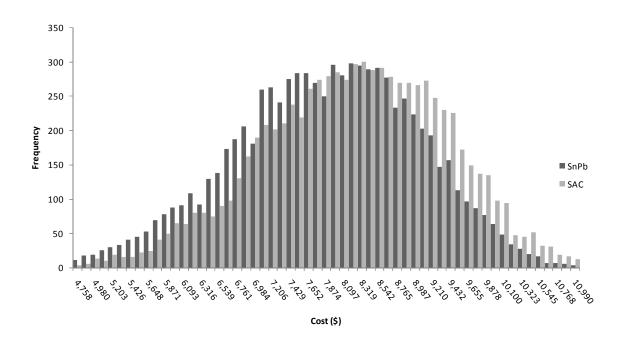

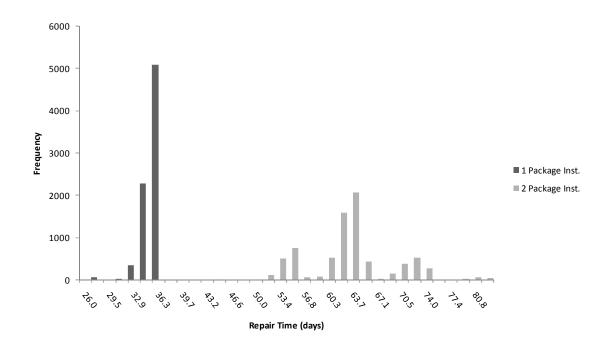

| Figure 3.15: Histogram Comparing Repair Cost for SnPb and SAC, Test A                |      |

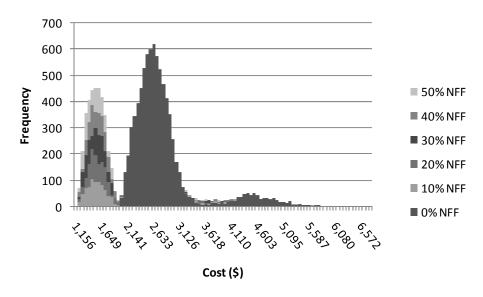

| Figure 3.16: Effect of Increasing NFF Percent on Population Growth                   |      |

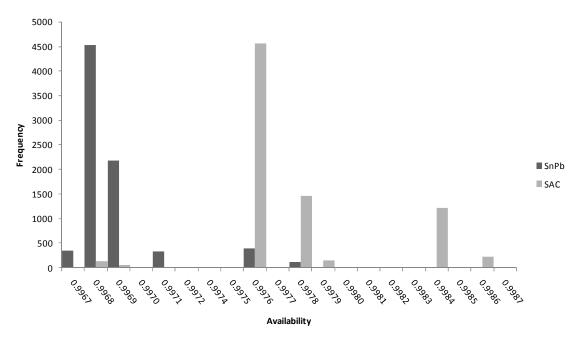

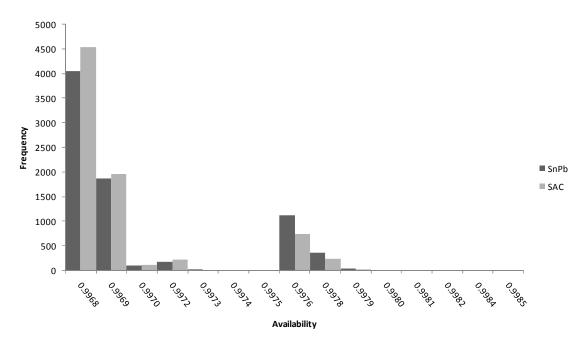

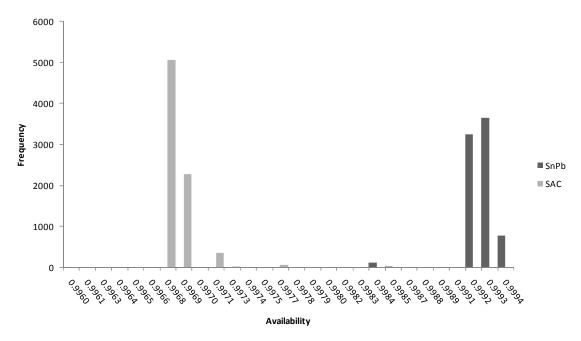

| Figure 3.17: Histogram Comparing Availability for SnPb and SAC, Test A               |      |

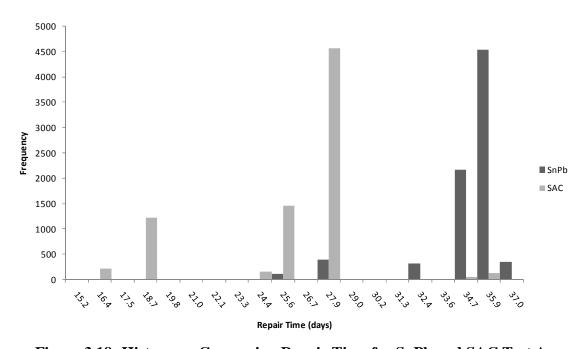

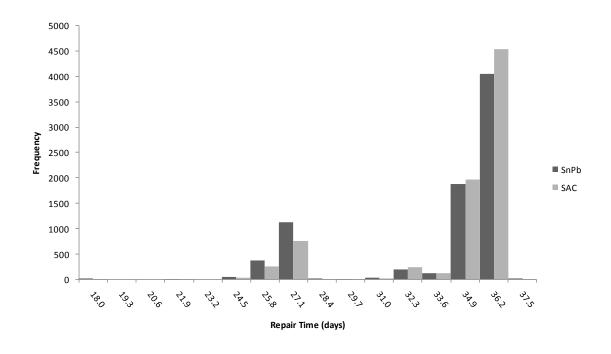

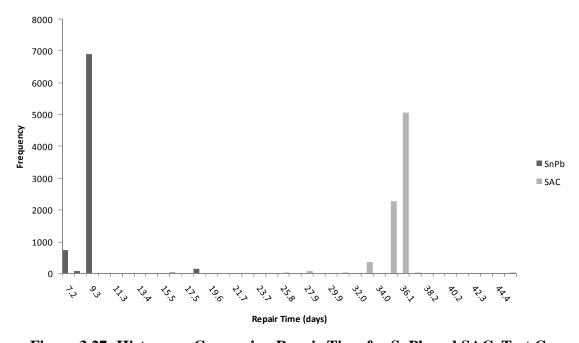

| Figure 3.18: Histogram Comparing Repair Time for SnPb and SAC Test A                 | . 62 |

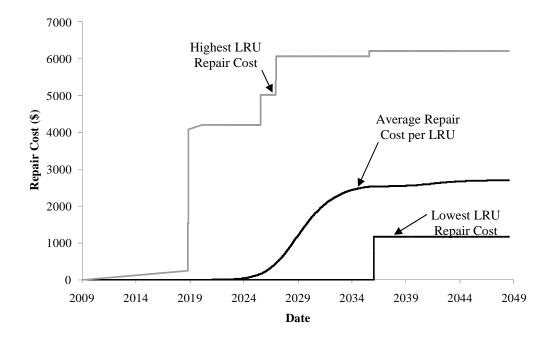

| Figure 3.19: Individual Lowest and Highest LRU Repair Cost Compared to the Aver     | rage       |

|-------------------------------------------------------------------------------------|------------|

| LRU Repair Cost for SAC Solder                                                      | 64         |

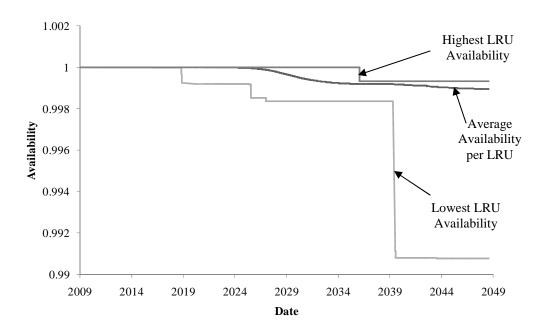

| Figure 3.20: Individual Lowest and Highest LRU Availability Compared To the Ave     | erage      |

| LRU Availability for SAC Solder                                                     | 65         |

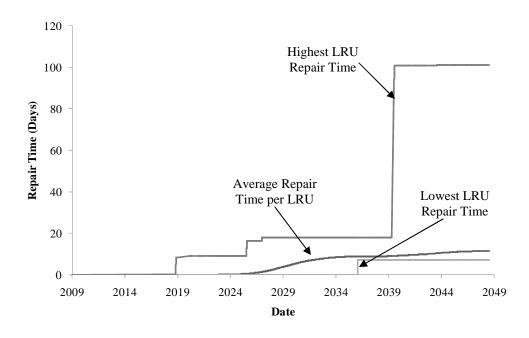

| Figure 3.21: Individual Lowest and Highest LRU Repair Time Compared To the Av       | erage      |

| LRU Repair Time For SAC Solder                                                      | 66         |

| Figure 3.22: Histogram Comparing Repair Cost for SnPb and SAC, Test B               |            |

| Figure 3.23: Histogram Comparing Availability for SnPb and SAC, Test B              | 67         |

| Figure 3.24: Histogram Comparing Repair Time for SnPb and SAC, Test B               | 68         |

| Figure 3.25: Histogram Comparing Repair Cost for SnPb and SAC, Test C               | 69         |

| Figure 3.26: Histogram Comparing Availability for SnPb and SAC, Test C              | 70         |

| Figure 3.27: Histogram Comparing Repair Time for SnPb and SAC, Test C               | 70         |

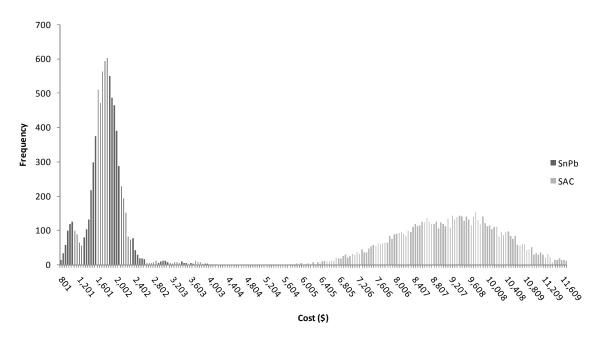

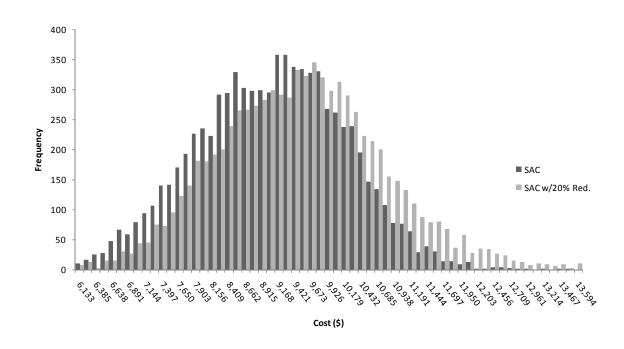

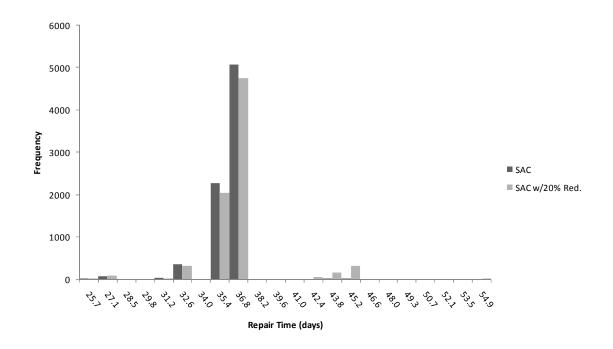

| Figure 3.28: Histogram Comparing Repair Cost for Baseline and 20% Reduced Post      | <u>,</u>   |

| repair Reliability, Test D                                                          | 72         |

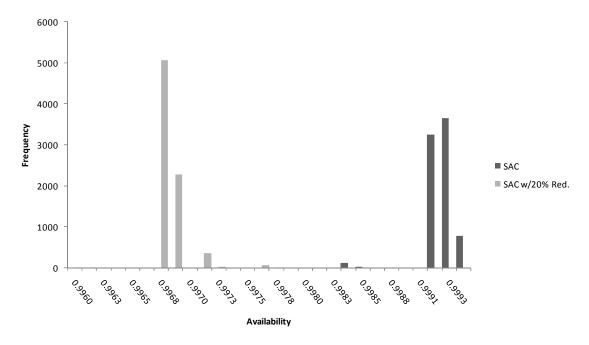

| Figure 3.29: Histogram Comparing Availability for Baseline and 20% Reduced Post     | ; <b>-</b> |

| repair Reliability, Test D.                                                         | 72         |

| Figure 3.30: Histogram Comparing Repair Time for Baseline and 20% Reduced Pos       | t-         |

| repair Reliability, Test D                                                          | 73         |

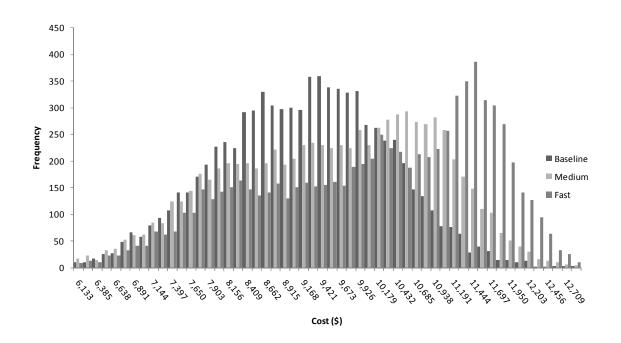

| Figure 3.31: Histogram Comparing Repair Cost for Baseline, Medium and Fast Field    | ding       |

| Rates, Test E                                                                       | 74         |

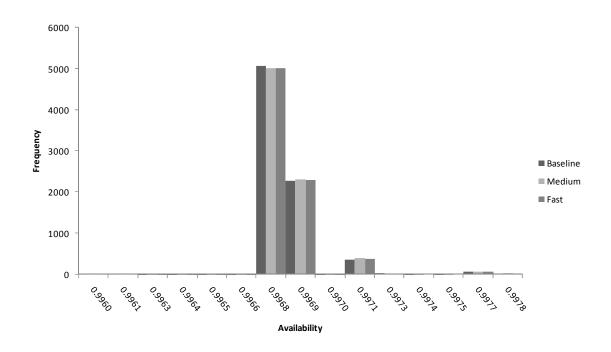

| Figure 3.32: Histogram Comparing Availability for Baseline, Medium and Fast Field   | ding       |

| Rates, Test E                                                                       | 75         |

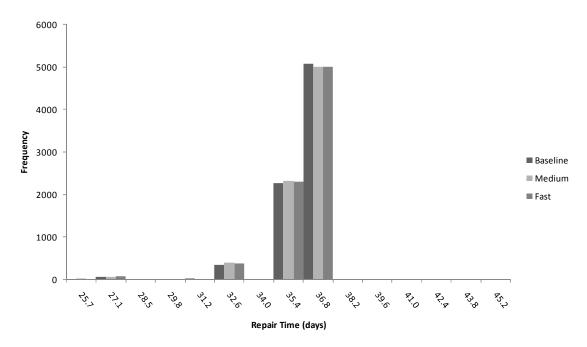

| Figure 3.33: Histogram Comparing Repair Time for Baseline, Medium and Fast Fiel     | ding       |

| Rates, Test E                                                                       | 75         |

| Figure 3.34: Histogram Comparing Repair Cost for Baseline and Reduced Capacity      |            |

| Process Steps, Test F                                                               | 77         |

| Figure 3.35: Histogram Comparing Availability for Baseline and Reduced Capacity     |            |

| Process Steps, Test F                                                               | 77         |

| Figure 3.36: Histogram Comparing Repair Time for Baseline and Reduced Capacity      |            |

| Process Steps, Test F                                                               | 78         |

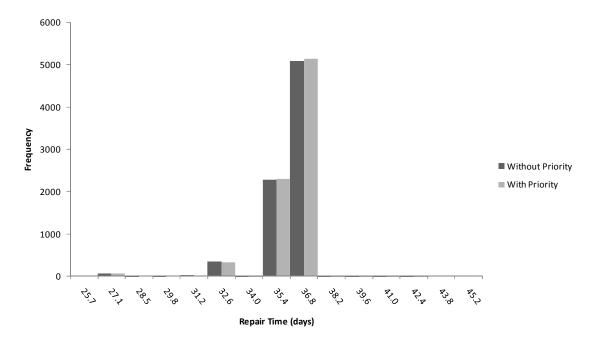

| Figure 3.37: Histogram Comparing Repair Cost for Prioritized and Un-prioritized LI  | RUs,       |

| Test H                                                                              | 80         |

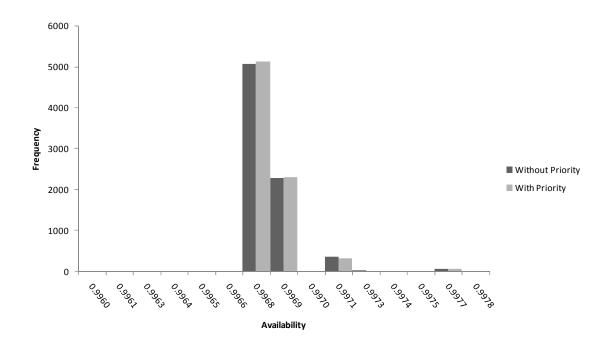

| Figure 3.38: Histogram Comparing Availability for Prioritized and Un-prioritized Ll | RUs,       |

| Test H                                                                              |            |

| Figure 3.39: Histogram Comparing Repair Time for Prioritized and Un-prioritized L   | RUs,       |

| Test H                                                                              |            |

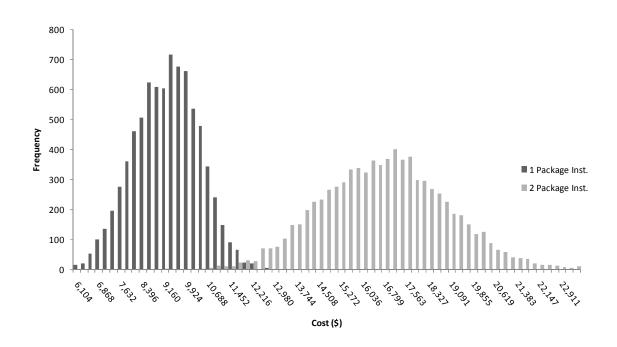

| Figure 3.40: Histogram Comparing Repair Cost for Single and Double Package Insta    | ance       |

| LRUs, Test I                                                                        | 83         |

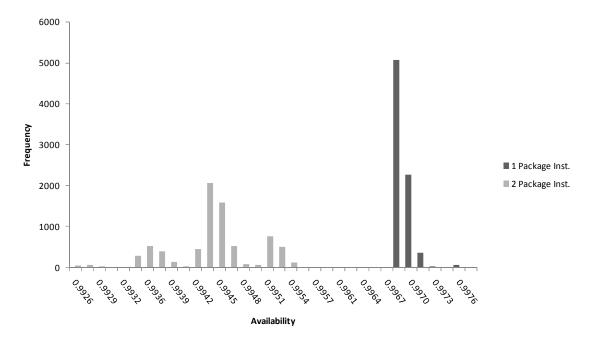

| Figure 3.41: Histogram Comparing Availability for Single and Double Package Insta   | ance       |

| LRUs, Test I                                                                        | 83         |

| Figure 3.42: Histogram Comparing Repair Time for Single and Double Package Inst     | tance      |

| LRUs, Test I                                                                        |            |

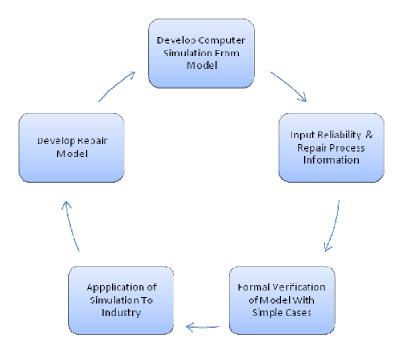

| Figure A.1: Progression of a Modeling to Implementation                             |            |

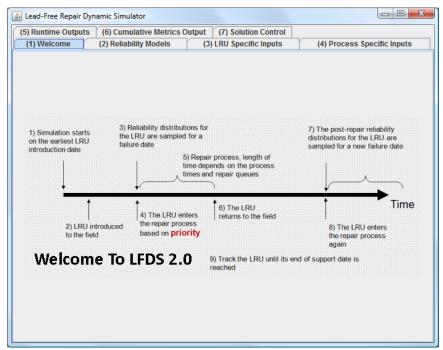

| Figure A.2: Tab (1), Welcome                                                        | 92         |

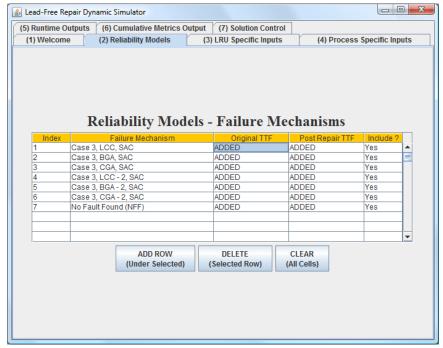

| Figure A.3: Tab (2) Reliability Models                                              |            |

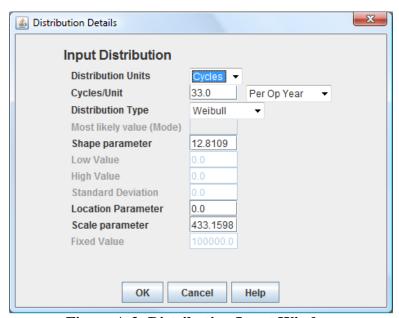

| Figure A.3: Distribution Input Window                                               | 93         |

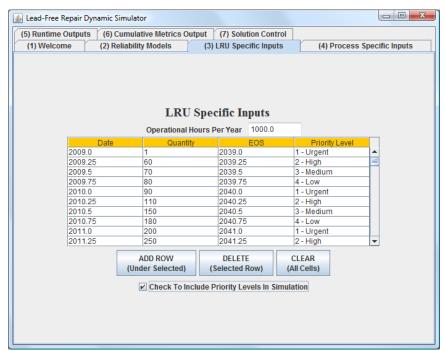

| Figure A.4: Tab (3) LRU Specific Inputs       | 94 |

|-----------------------------------------------|----|

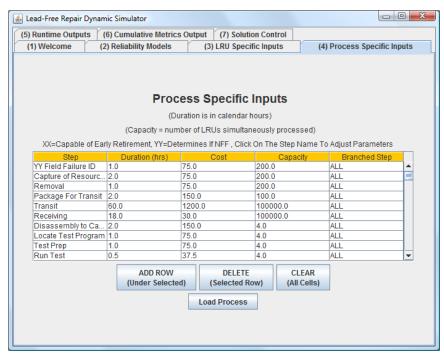

| Figure A.5: Tab (4) Process Specific Inputs   | 95 |

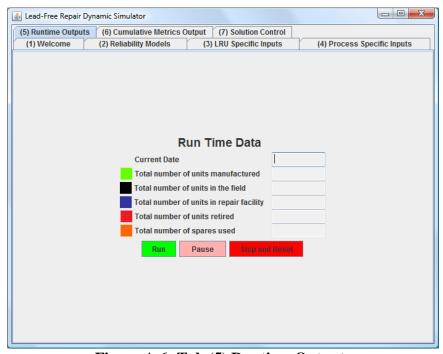

| Figure A.6: Tab (5) Runtime Outputs           | 96 |

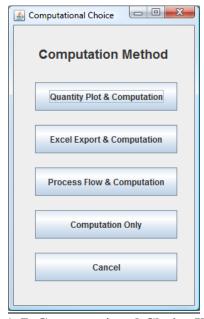

| Figure A.7, Computational Choice Window       | 96 |

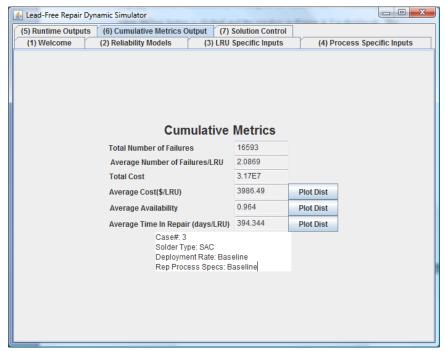

| Figure A.8: Tab (6) Cumulative Metrics Output | 97 |

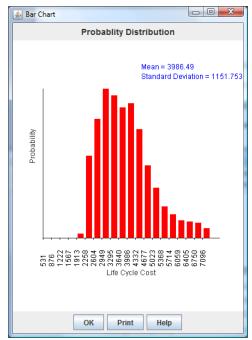

| Figure A.9: Distribution of Repair Cost       |    |

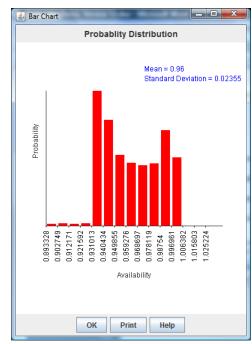

| Figure A.10: Distribution of LRU Availability |    |

| Figure A.11: Distribution of Repair Time      |    |

| Figure A.12: Tab (7) Solution Control         |    |

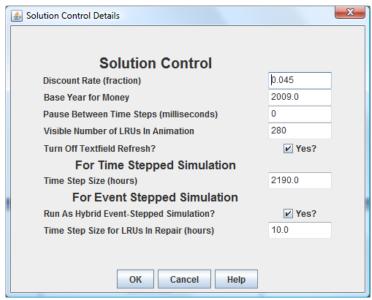

| Figure A.13 Solution Control Details          |    |

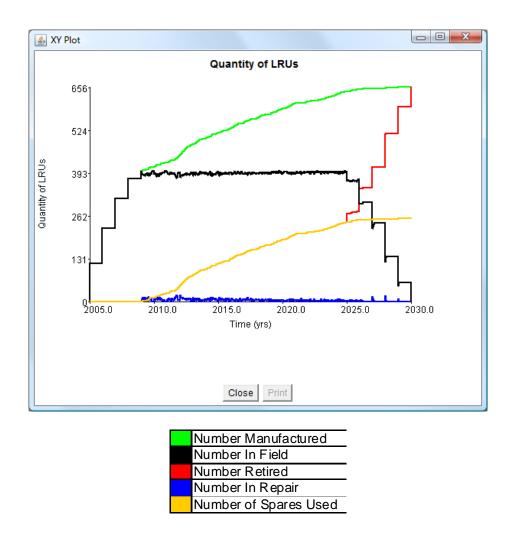

| Figure A.14: Quantity Plot.                   |    |

| Figure A.15: Process Flow Animation           |    |

### Chapter 1: Introduction

The impact of transitioning to lead-free parts is affecting the electronics industry and most severely the aerospace and defense industries that produce products that require high levels of reliability. Products produced with applications known as AHP (Aerospace and High Performance) are characterized by severe or harsh operating environments, long service times, and high consequences of failure [GEIA 2008]. With these consequences of failure, AHP manufactures, currently are excluded from the RoHS directive. The current directive excludes equipment solely for the purpose of national security and military purposes that are not included in the consumer categories described in the RoHS Directive.

Although excluded from using lead-free parts, most defense and aerospace manufacturers utilize the same supply chain as commercial electronics manufacturers for parts and boards. This is important as in many cases AHP electronics must be repairable at the soldered assembly level [GEIA 2008]. While the supply chains for AHP parts can still produce legacy products that contain tin-lead solder, they have relatively little motivation to do so because the defense and aerospace industry represent less than 5% of the total market share [Russell 2007]. Therefore, commercial manufacturers are focused on providing parts for the commercial electronics industry. The limited availability of

\_

<sup>&</sup>lt;sup>1</sup> WEEE has only exclusions, RoHS has exemptions and exclusions. When equipment is left entirely out of legislation it is termed excluded. This means that certain types of equipment are out of the scope of WEEE entirely, i.e., equipment for the sole use in Aerospace and Defense applications. Exemptions are a series of applications of banned substances that are exempted from some of the RoHS requirements, i.e., Medical and Telecommunications [U.S. Department of Commerce, 2009]. Equipment for use in Aerospace and Defense applications are excluded and not mentioned in RoHS.

<sup>&</sup>lt;sup>2</sup> RoHS – Restrictions on Hazardous Substances is a European directive that restricts hazardous materials in electronics equipment [European Union 2002/95/EC, 2002/96/EC]

lead-based items has become a major driver in the design and sustainment of defense and aerospace systems as the number of tin-lead electronic suppliers' has decreased. This challenge will require the defense and aerospace industry to convert to lead-free long before the RoHS directive requires it to (if ever), i.e., their current exclusion from RoHS is effectively a moot point.

Abundant data exists on the short-term reliability (i.e., less than 5 years) of leadfree solder joints under single loading conditions [Ganesan et al. 2005]. However, data

on combined loading conditions and long-term reliability is limited. Many AHP leadfree products will be serving in platforms where long-term (greater than 15 years)

reliability is a critical requirement. The impact of reliability may be most prevalent at the

system- and enterprise- level for legacy tin-lead assemblies that have been repaired with

lead-free solder. **Legacy systems** refer to systems that have been manufactured in the

past using tin-lead solders and must continue to be supported for the foreseeable future,

while new systems refer to those that were manufactured using lead-free technology. **Enterprise-level impact**, refers to the impact on support logistics (repair flow: repair

time, repair cost, backlog) over the support life cycle of equipment. The impact of the

conversion to lead-free must be quantified in order to provide performance expectations

and provide risk mitigation if and when needed to program-level management.

#### 1.1 Making a Case to Management

Engineers communicate to program-level management every day that the "sky is falling" due to some previously unforeseen technical issue, but management is rarely moved to action without a quantitative demonstration of the system- or enterprise-level

risks posed by the issue. The potential for reduced and less predictable reliability of leadfree electronics increases the probability that a serious technical issue will arise. While engineers have the resources to model and quantify system reliability, they often lack the ability to articulate the risk/impact of the reliability (or changes to the reliability) in terms of cost and availability that management will understand. To provide engineers with a tool that they can use to develop sound proposals (i.e., business cases) to program-level management, a model is needed. This model needs to track large populations of LRUs from field introduction to retirement and accumulate characteristics of the repaired units, including repair cost, repair time and unit reliability. An LRU is defined as a "Line Replaceable Unit", i.e., an electronic card (or board) that can be removed from the field and repaired or replaced. The acronym LRU is used in this thesis synonymously to Shop Replaceable Assembly (SRA), Shop Replaceable Unit (SRU), and Weapon Repair Assembly (WRA). In addition to tracking a population of LRUs, it is important to provide a distinct comparison of traditional tin-lead and lead-free solder reliability. This will allow engineers to make a direct comparison of tin-lead and lead-free solders and the impact in cost and availability they can have on long term fielding.

### 1.2 Lead-Free Solder

For the past 60 years, soldering materials have traditionally been composed of tin and lead. The transition to lead-free solders, meaning that the content of the element lead is <0.1% by weight, applies both to printed circuit boards (PCBs) soldering materials, namely solder paste, or wave solder for surface-mount or through-hole assembly respectively, and finishes used on part terminals and PCB mounting pads [Ganesan et al.

2005, GEIA 2008]. Many different lead-free solders have been proposed and used, however, the most common are Sn-3.0Ag-0.5Cu (SAC 305) alloys due to low melting temperatures and good wettability compared with the Sn-Ag alloys [Zhu et al. 2005]. Currently engineers are developing SAC alloys containing the elements of Indium and Bismuth to improve application properties such as anti-oxidization, stability and melting point [Ma 2006]. Although improvements have been made with lead-free solders such as SAC, many concerns with reliability still exist. The example case in this thesis considers the use of SAC 305, the most commonly used lead-free solder in industry [Hillman 2006].

#### 1.2.1 The Conversion to Lead-Free

Legislative pressures resulting from the RoHS Directive on lead in electronics (and similar pending legislation throughout the world), the enacted Japanese take-back legislation (and similar pending legislation elsewhere in the world), and marketing policies from electronics companies, are the driving forces behind lead-free solder adoption [Eveloy 2005].

The primary driving force of the lead-free conversion is RoHS, a European Directive passed in 2003 that restricts the use of certain hazardous substances in electrical and electronic equipment. The aim of the RoHS Directive is to control the use of certain hazardous substances in newly fielded and future repaired electrical and electronic equipment (EEE) [European Union 2002/95/EC, 2002/96/EC]. Hazardous substances whose use is restricted include: lead, mercury, cadmium, hexavalent chromium, polybrominated biphenyls (PBB) and polybrominated diphenyl ethers (PBDE) [European

Union 2002/96/EC]. Electrical and electronic equipment are categorized into ten categories ranging from household appliances to sports equipment. However, not included in this list are electronics associated with defense and aerospace electronics due to reliability concerns and the implications of failure.

An analysis of individual companies' strategies and consumer reaction within the electronics industry shows that to date, the main benefit of migrating to lead-free electronics has been an increase market share through product differentiation, in terms of product environmental friendliness [Pecht 2005]. Thus, due to the consumer's growing environmentally conscious, manufactures are voluntarily migrating to lead-free technology because these manufacturers wish to be considered environmentally friendly [Casey 2002]. The actual value to the environment (if any) of the conversion from tin-lead to lead-free electronics is not clear and will not be addressed in this thesis.

Irregardless of the reasons for conversion from tin-lead to lead-free electronics, the conversion is a reality (the "train has left the station" and there is no going back) and the ramifications of the conversion need to be understood.

### 1.3 Repair Culture Concerns

Two different cultures exist associated with the handling of failed electronics. Commercial electronics manufactures follow a throwaway culture with their consumer products, i.e., the ideology that throwing away a failed product and replacing it is less expensive than repairing it. In the defense and aerospace industry, a repair culture is followed. The belief behind this culture is that it is more economical to repair than to throwaway and replace.

A legacy aerospace or defense system, a system that was manufactured prior to the RoHS directive with tin-lead technology must continue to be supported post the RoHS directive (maybe for many years). Many military platforms today are operating with legacy technology from the 1980s and 1990s. If a part fails, it may be necessary to repair it using a newer lead-free technology as equivalent or identical lead-based parts become less available (obsolete). The introduction of lead-free repair and manufacturing processes on a legacy system introduces new failure mechanism associated with the addition of lead-free parts and the exposure to thermal profiles not experienced during the original tin-lead manufacturing process.

#### 1.4 Thesis Objectives and Tasks

The objective of this thesis is to provide a model that can be used by engineers to demonstrate to program management the repair cost and availability impacts of reliability changes and various repair scenarios for mixtures of legacy and new electronic systems. The thesis will accomplish the following:

- Describe the development of a new model for the repair of electronic systems

- Develop test cases based on a combination of reliability simulation and experimental results for a representative set of electronic parts

- Provide demonstration results from the test cases from which application-specific and general conclusions about the impact of lead-free parts can be drawn.

Chapter 2 describes the model developed in this thesis in detail in order to provide the reader with background regarding its operation. Topics discussed include: queuing, priority sorting, reliability distribution sampling, modeling a repair process, and the formulation of cost and availability metrics that are the output of the model. The model developed in this thesis has been implemented in software in a tool called the Lead-Free Dynamic Simulator (LFDS). For a description of the software, see Appendix A.

Chapter 3 applies the model to a set of example problems. The sample cases used for validation have been created under the guidance from the Naval Surface Warfare Center (NSWC) at Crane, IN. The repair process was modeled after the Navy's 3M (Maintenance and Material Management) system. Based on this case study, engineers will have the capability to study the implications on repair cost, availability, and repair time due to the conversion from tin-lead to SAC solders.

Chapter 4 provides a summary of results and conclusions based on the case study in Chapter 3. Also included are a set of contributions and recommendations for future work associated with this research.

### Chapter 2: Model Development

Traditional methods of studying a system include experimenting with the actual system and experimenting with a model of the system. Both may produce similar results, however, in some situations, it may not be feasible to test the actual system. Creating a model, either physical or mathematical, allows engineers to gain insight into the expected outcome of the system's operation. The emulation of the system's operation over time introduces the capability to monitor years of activity, the time between LRU field introduction and end of support. One method of modeling a system's operation over time is known as a discrete event simulation. This chapter discusses the development of a discrete event simulation based model for evaluating the impact of reliability on the part repair process for traditional lead-tin and lead-free solders.

### 2.1 Modeling Repair<sup>3</sup> Processes

The service repair model developed in this thesis describes the process in which operating LRUs are tracked to and through repair after failure. The model developed here also models an independent "post-repair" reliability that can represent "as good as new" or "not good as new" repair. Since the process in this model assumes a single of echelon supply (central depot), and does not take into account the product structure of failed units (assemblies, subassemblies), the model will be referred to as a single-echelon, single-indenture model [Sleptchenko et al. 2002].

-

<sup>&</sup>lt;sup>3</sup> Repair refers to fixing units that have failed during field use. Alternatively, "rework" refers to fixing units identified as defective during a manufacturing process (prior to fielding). Rework is not addressed in this thesis.

In the area of repair process modeling, a great deal of effort has been done to solve classical repair problems such as "the military logistics problem of stocking repairable parts for aircrafts at bases which are capable of repairing some, but not all broken parts, and at a central depot which serves all of the bases" [Guide and Srivastava 1997]. This method of understanding, based on Sherbrooke's METRIC model [Kennedy et al. 2002, Sherbrooke 1968], identifies a perspective of the repair process as multiechelon, and multi-indenture, focusing entirely on inventory constraints and replenishment quantities. Later models such as MOD-METRIC and VARI-METRIC are extensions to the base METRIC model that include many modifications to study batch repairs and lateral shipments. These models however, focus almost entirely on the optimal stocking of parts as bases (or forward locations) and a central depot facility that repairs failed units returned from the bases while providing some predetermined level of service [Guide and Srivastava 1997]. There objective is typically to maximize the availability of aircraft, or conversely minimize shortages and hence the number of grounded aircraft, subject to a budget constraint [Guide and Srivastava 1997].

Due to the increased numerical complexity associated with multi-echelon and multi-indentured processes, Diaz and Fu developed a simple model of a single repair shop consisting of one or more single server queues [Diaz and Fu 1997]. This model's primary focus is inventory control and therefore is most appropriate in a resource-constrained environment such as in most industrial settings.

Improvements continued to the METRIC model by Graves in 1985, which introduced the complexities of modeling general service time distributions and multiple types of repairs.

The METRIC model and the single-server method modeled developed by Diaz and Fu do not allow for studies of the impact of components that require different repair steps, or of components that can fail due to multiple mechanisms. Grave's model, although addressing the multiple repair types, differentiates the repair type by another Poisson distribution failing to capture the relationship between LRU and LRU.

The modeling methods, METRIC, MOD-METRIC, VARI-METRIC and the single-server method modeled developed by Diaz and Fu, assume: a Poisson failure process, an infinite LRU population (so that arrival rate at the depot is constant and independent of the actual number of working LRUs), and ample repair capacity (so that the distribution of LRUs in the repair facility is Poisson) [Diaz and Fu 1997]. However, the repair model in this thesis must allow for multiple failure mechanisms, the distribution of failures over time (or cycles), and the ability to distinguish between specific failure mechanisms in the repair process in order to address the tin-lead (SnPb) to lead-free (SAC) conversion. The difference between sampling Weibull distributions for time to failure data and assuming a Poisson failure rate makes the model significantly different. Although existing models track components or LRUs independently, not as populations, they do not carry the specific information unique to the LRU. Tracking the component's specific TTF, mechanism that caused failure, priority level, introduction date or end of support date is very important because this information can be very different for each LRU.

In the model required in this thesis, the repair process is resource limited (in fact, part of the outcome of this research is the required repair process capacity) and each LRU is tracked individually following FIFO queuing rules when interacting with LRUs of

similar priority. None of the known repair models meet the specific requirements; therefore, a new model will be developed.

### 2.1.1 Modeling Using Discrete Simulation

Discrete simulations include two distinct modeling techniques, time-based and discrete event.

For time-based simulation, the progress of the modeled repair process occurs at discrete points in simulation time and are labeled time steps. **Simulation time** is defined as the time being represented within the model. While the state of the process may be observed precisely at time steps 1, 2, 3, etc., its progress between any two consecutive time steps is assumed to be atomic and cannot be perceived by an external observer [Ghosh et al. 2000]. Time-based simulation assumes that important changes only occur at the discrete time steps, and nothing important occurs between consecutive time steps. Therefore, the choice of the time step value is determined by the maximum desired rate of progress, in terms of time of the simulation process.

In discrete event simulation, the process being modeled is advanced by events not time steps. The Cambridge English Dictionary [Cassidy 2007] defines "event" as anything that happens, especially something important or unusual. In the discipline of discrete event simulation, an event refers to any significant incident associated with the state of the process being modeled, expressed in terms of any frame of reference (time, space, energy, etc.) [Ghosh et al. 2000].

### 2.1.2 Advantages of a Simulation

Advantages of computer simulation include the ability to compress and expand time, the ability to control sources of variation, avoidance of errors in measurement, the ability to stop and review, the ability to restore system state, facilitation of replication, and control over the level of detail [Fishman 2001]. The ability to compress or expand time is facilitated in the simulation by running through multiple years of events in a matter of minutes or even seconds depending on the required level of computation. The ability to control (and identify) variation is accomplished through a statistical analysis of the relationship between the independent (input) and dependent (output) factors [Fishman 1978]. Unlike field experiments, which exhibit unavoidable errors of measurement, no measurement errors exist in simulations since the programmed simulation produces numbers free of any superimposed variation due to external and uncontrollable sources [Fishman 1978]. The ability to stop and review intermittent results only exists in simulations, as with field experiments it is often impossible to completely stop all active processes. The ability to restore the systems state allows the researcher to re-run the model to output additional data, and to duplicate the previous run to include this data. The ability to replicate experiments allows for changes in select operating parameters and the investigation of their impact on the result. The model's detail level affects the analysis cost, time, chance of errors and debugging time.

### 2.2 Introduction to Modeling Repair Using Discrete Event Simulation

This section describes the development of a new discrete event simulation based repair model that can be used to evaluate the repair of tin-lead and lead-free electronic systems.

The Lead-Free Dynamic Simulator (LFDS) developed in this thesis exhibits many of the qualifications of a discrete event simulation and time-based simulation. The model utilized in the simulation is stochastic, dynamic, partially discrete, and partially timebased. It is stochastic because its variables are treated as random. This randomness is achieved in the model by sampling reliability distributions so that a population of nonidentical fielded systems can be assessed. The model is intrinsically dynamic, being dependent on time as the primary state variable. The simulation time of the model is represented by tracking each LRU from introduction to retirement (referred to as end of support). In order to comprehend how the model can be partially discrete and partially time based, the framework of the model must be explored. While the discrete list of LRU failure events is determined prior to the advancement of simulation time, the repair events are dependent on more than the simulation time and the state of its individual LRU. The total repair time is dependent on the quantity of LRUs in repair. This quantity and repair time relationship is therefore only advanced by a discrete set of monotonically increasing time steps where the choice of the duration of the time step interval reflects the desired accuracy of the model.

#### 2.2.1 Mode of Execution

The mode of execution for the Lead-Free Dynamic Simulator is as-fast-aspossible execution. This method is also known as unpaced execution because no

relationship exists between the simulation time and wall clock time. The simulator

operates by determining the earliest LRU introduction date into the field, then advances

by time steps or jumps to discrete events. The simulation operates as a discrete event

simulation by jumping to a failure event when there are no LRUs in the repair process.

This jump is accomplished by increasing its time step size to the difference of the next

failure date minus the current date. The time step can increase when there are no LRUs

in the repair process without compromising the simulation's accuracy because state

values are not changing. When one or more LRUs are in the repair process, the model

still operates as a discrete event simulation and the simulation time advances by a

predetermined time step length because events are occurring at the instant of the time

step.

The disadvantage of a time stepped only simulation is the addition of unnecessary computations when no events are present (which results in slow simulations). Locations when no events are present include when there are no LRUs in repair, and when no LRUs are failing.

The Lead-Free Dynamic Simulator utilizes an event-based method of time advancement at discrete time instants in order to: 1) minimize the total wall clock time the simulation operates, 2) maximize state value accuracies.

### 2.2.2 Process Modeling (Process Flow and Steps)

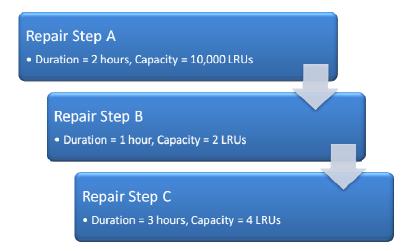

A process flow is a chronological interaction of events used to describe both informational and physical objects [Fishman 1973]. For the model developed in this thesis, the process flow is represented by a list of the process steps in a repair process. Process steps are single server Markovian Queue chains with priority rankings [Ozekici 1990]. Each process step is defined by six unique properties, the step name, cost, duration, capacity, failure mechanism applicability, and early retirement abilities. These properties, which are inputs to the model, affect how failed LRUs are processed in repair. While each process step is independent with respect to another process step's properties, the position or index in the list of steps is global to the simulation.

Depending on a process step's capacity and assuming that there are no other failed LRUs in the step's queue, a LRU will be immediately repaired. As failed LRUs continue to enter the step's queue, they are placed into repair until it reaches full capacity. The queue represents the sequential list of LRUs in the step waiting to be repaired. Capacity is the maximum number of LRUs that a step can simultaneously repair. The capacity of five LRUs in the "Field Failure Identification" process step, Table 2.1, can be imagined as having five workers on separate workstations all performing the same tests to identify what caused the LRU to fail. When there are a greater number of LRUs than the maximum capacity in the step, LRUs are placed into the waiting pool. After the process step has been completed for the LRUs in repair they move to the next sequential step. LRUs that have been held in the waiting pool are drawn into the process step's

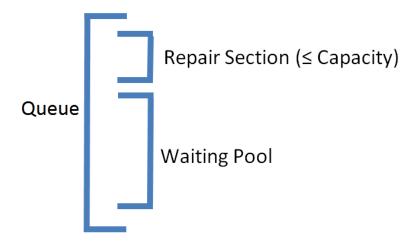

repair based on a FIFO queuing policy. Figure 2.1 represents the waiting pool and capacity as a subset of the process step's queue.

Figure 2.1: Breakdown of a Process Steps Queue into the Repair Section and Waiting Pool

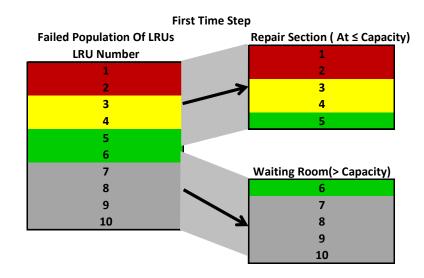

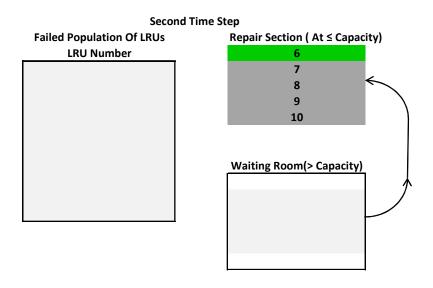

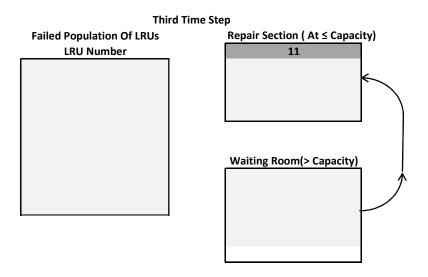

Consider the example shown in Figure 2.2. When there are greater than five LRUs in the step, they go into the waiting room where they wait until they can be processed by workers (LRU numbers 6 through 11). The time in step, and total repair time, continues to grow even when the step is in the waiting room. In the case in Figure 2.4, during the third time step there is only one LRU being processed. The LRUs in the queue may be processed regardless if the queue is at capacity or not. Priorities are used to sort the LRUs if requested. The first time step in Figure 2.2 processes all of the urgent, and high priority failed LRUs and one of the medium priority LRUs. The second time step, Figure 2.3, processes the final medium priority LRU followed by four of the LRUs with low priority. The third time step, Figure 2.4, processes the final low priority LRU. This step completes the process of all the failed LRUs waiting to be processes in the step.

Table 2.1: Process Step "Field Failure Identification"

| Process Step                 | <b>Duration (hrs)</b> | Cost (\$) | Capacity | Branching |

|------------------------------|-----------------------|-----------|----------|-----------|

| Field Failure Identification | 6.0                   | 150.00    | 5        | ALL       |

Figure 2.2: First Time Step of Field Failure Identification Process Step

Figure 2.3: Second Time Step of Field Failure Identification Process Step

Figure 2.4: Third Time Step of Field Failure Identification Process Step

Similar to the structure of the process steps is the list of LRU objects. The LRU list contains an individual object for each LRU. Properties included are the LRU number (unique), introduction date, end of support date (EOS), the next time to failure, and mechanism that will cause the next failure. The "LRU number" is an index assigned to the LRU to identify if from other LRUs within the model.

### 2.2.3 Conversion of Non-Time Based Distributions

Since the model's execution is based on the advancement of time, all model inputs that define events must also be mapped to time. When a non-time based reliability distribution is used, i.e., one that is in cycles (thermal, vibration or other), the model must convert all values into relevant time measures. In order to do this, the failure mechanism must contain the basic reliability distribution parameters, the number of cycles per unit, and the units desired for the conversion. In an example case, a failure mechanism asserts

that an LRU will experience 1000 cycles per operational year. It is expected then, that if the reliability distribution was a Weibull distribution containing a location parameter of 4000 cycles that the LRU will fail sometime after four operational years. This calculation is done in the model, by converting cycle based reliability distributions from operational years, days, hours, and minutes to operational hours.

### 2.2.4 Sampling

In order to determine the location (in time) of events corresponding to failures of LRU instances, the time to failure distributions associated with the applicable failure mechanisms must be sampled. Since the example case described in Chapter 3 uses 2-parameter Weibull time to failure distributions, Equation (2.1) the sampling procedure will be explained below.

$$(x; \beta, \eta) = \frac{\beta}{\eta} \left( \frac{x}{\eta} \right)^{\beta - 1} e^{\left( \frac{x}{\eta} \right) \beta}$$

$$\beta = \text{shape parameter}$$

$$\eta = \text{scale parameter}$$

(2.1)

A Monte Carlo method is used in which deviates are obtained from probability distributions through the following process: 1) a random number between 0 and 1 inclusive is chosen; 2) the value of the cumulative distribution function (cdf) is set equal to the random number and the corresponding value is added to the current time in the model. The addition of the cdf value to the current time creates the next time to failure TTF.

### 2.3 The Modeling Process

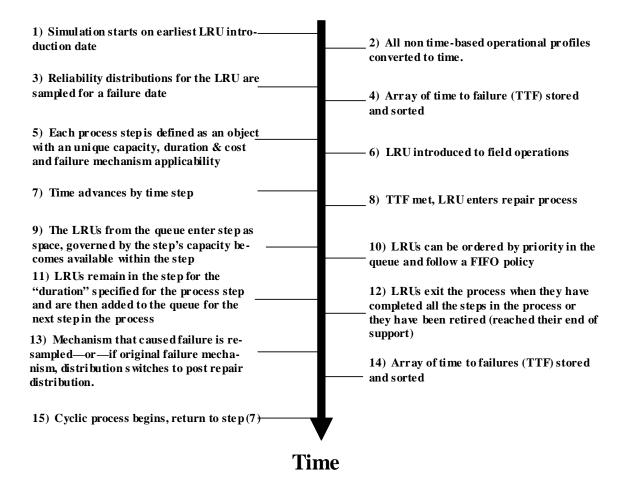

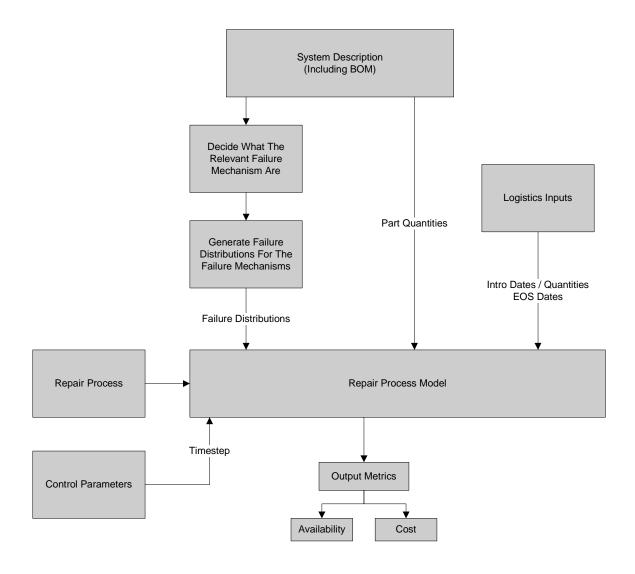

Unique to the model described in this thesis is the ability to track information regarding individual LRUs from introduction to end of support to and through a repair facility during failure. A conceptual layout of the model is depicted in Figure 2.5. The model starts at step 1 in Figure 2.5, by determining the earliest introduction date in the population of LRUs. In the preprocessing stage, steps 2 through 4 in Figure 2.5, operational profiles are converted to common units, reliability distributions are sample, and numerical sorting of data occurs to determine the soonest failure event. Steps 6 through 14 in Figure 2.5, describe the operation of the simulation and the tracking of a LRU to and through the repair process. Important to these steps are the advance of time by variable time step sizes, the repair of LRUs in a process is flow determined by specific repair rules, i.e., FIFO, priority, duration, etc, and the resampling of a post-repair reliability distributions. The LRU is retired when they reach their end of support dates. If the LRU has not been retired, the model progresses to step 15 of Figure 2.5. The LRU will continue in the cycle of fielding, failure, repair, and re-fielding until its end of support date is reached.

Figure 2.5: LRU Flow through the model from Fielding to End of Support

Important to the single LRU flow is the interaction that exists when multiple LRUs are in the repair process. When there are multiple LRUs in the repair process, a significant amount of queuing and sorting occurs in steps 9-14 in Figure 2.5.

### 2.3.1 Modeling the Queues

Each process step in the repair process has a repair section limited by the capacity and waiting pool, which are subsets of the queue Figure 2.1 that individual LRU instances enter into in the order in which they arrive at a specific process step (FIFO).

The process step takes LRU instances from the top of the waiting pool and moves them into the repair as its capacity allows.

The arrival process associated with failing LRUs being fed into the repair queues can is not an ordinary Poisson process with rate  $\lambda$ , therefore the time between LRU failures, are independent of each other [Ozekici 1990]. This makes the model different from the repair models described in the literature review; the time to failure is not generated by the constant failure rate. Within this model, LRU failures are dependent on TTFs generated through Monte Carlo sampling of Weibull distributions.

Once an LRU fails, it enters a repair step and stays there for the specified duration of the step. The time in the step can increase based on having to wait if other LRUs are ahead of it, waiting to be repaired. In the case of the model described here, there are no distributions associated with the process step's duration. The time required for repair is associated with the specific mechanism that caused failure and the current number of LRUs in the process step. The time in the step will always be greater than or equal to the process step's duration. When the process step's repair is full and LRUs have to pause in the waiting pool, the total time spent in the step will increase.

#### 2.3.1.1 Service Policy (Queuing Discipline)

In order to define the service policy, three key items must be specified. The first item to be identified is the number of servers present in the process.<sup>4</sup> Within the model, there is only one repair process. This repair process, which is synonymous to the process flow, can be modeled as a Markovian queue (the capacity represents the maximum number of LRUs that can be simultaneously processed) with priorities. The second item

-

<sup>&</sup>lt;sup>4</sup> In this model, a server is defined as a single parallel repair process.

to be identified is the capacity of the queue, and the policy that dictates what happens when there are more LRUs in the step's queue than can be processed concurrently by the step. The third item to be identified is the service discipline, i.e., first in, first out (FIFO), last in, first out (LIFO), servicing in random order (SIRO) and priority rules (PR).

In 1953, Kendall [Kendall 1953] proposed the following notation to classify queues:

$$A \mid B \mid C \mid k$$

(Service Rule) (2.2)

Where:

A = interarrival distribution

B = service time duration,

C = number of servers

$k = queue \ capacity$

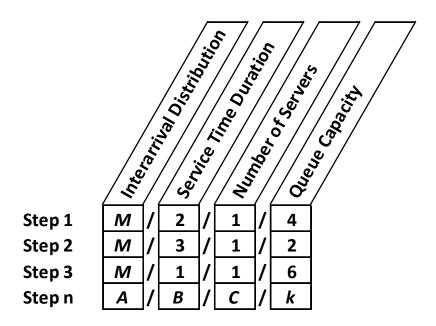

Within the model, LRUs enter the repair process through a Monte Carlo sampled Weibull distribution that is denoted by M. Each repair step has a fixed duration, denoted by the time in hours. As stated before, there is only one server, as all LRUs must flow though the same repair process. The queue capacity, k, is denoted by the maximum number of LRUs that can be repaired in the steps duration. Example step notations for the model described here are given in Table 2.2.

**Table 2.2: Example Process Step Notation**

### 2.3.1.2 Markovian Queues with Priorities (M/M/1/k) and Priorities

Within the model, LRUs are repaired individually rather than being repaired as a batch.

The first in, first out (FIFO) service discipline is often the most chosen procedure for determining the order in which LRUs are repaired. However, this is not the case in many service systems and customers are classified according to different priorities. VIP, first-class and economy-class priorities are almost always given to airline passengers. Users of computers systems are routinely given different priority levels to access the system and run their programs [Ozekici 1990].

# 2.3.1.3 Preemptive versus Non-preemptive

LRUs in fielded applications often have different levels of mission importance. In order to incorporate this in the model, priorities were introduced in order to expedite LRUs of higher importance through the repair process.

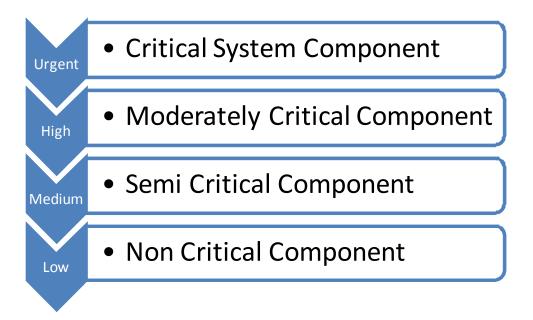

Within the model there are four priority levels: urgent, high, medium, and low, which are described based on mission criticalness in Figure 2.6. Priority levels urgent, high and medium are preemptive, meaning that if they join a queue that contains LRUs of lower priority, they will shuffle the order or preempt them from the repair of LRUs specified by the capacity being processed. When the queue opens up, the LRU preempted from service may continue from the point of the interruption, this rule is called preemptive-resume [Ozekici 1990].

During the repair process, and the beginning of each time step, the model sorts the LRUs into ranking priorities, fills the queue and begins repair. This method of sorting allows for a single, urgent priority LRU, to bypass all queue LRUs within a process step.

Figure 2.6: Priority Levels and Relation to Mission Criticalness

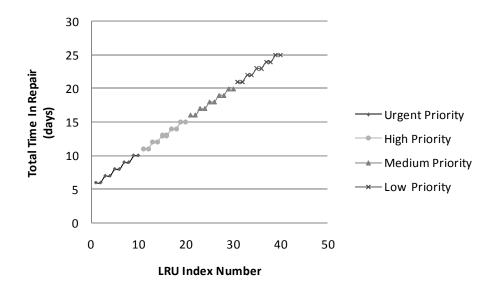

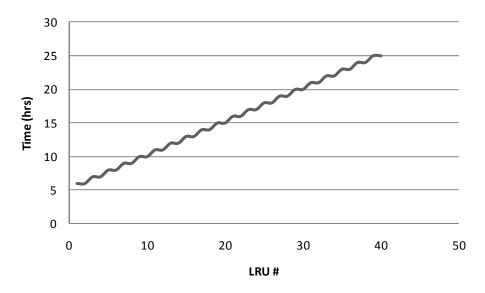

In order to better describe the impact of priority on LRU availability, a small population of 40 LRUs will be observed over a one year period (all of the LRUs are assumed to fail at the same time in this example). For a population this size, the capacities and durations of the repair process steps have been decreased to significantly impact the lead time before repair.

When the model simulates this population of LRUs, there is no change in the average availability between a population that was prioritized and a population that was not because the LRUs were assumed to fail only once. The increase in average repair time when prioritizing will be addressed below. When looking at the distribution of average repair times, the impact of prioritizing LRUs is clearly visible. Figure 2.7, plots the individual index number versus its total time in the repair process (sum of time spent either being repaired, or waiting to be repaired).

Figure 2.7: Impact of Priority on Total Repair Time

For this example the average repair time for each group of urgent, high, medium, and low priority LRUs is 8, 13, 18, and 23 hours respectably. The average repair time for all 40 LRUs in this sample is 15.5 hours. By assigning the mission critical LRUs the urgent priority rating, there is a 48.3% reduction in repair time. From Figure 2.7, it is clear that prioritizing LRUs can alter a population's repair time either decreasing or increasing it based on its level of mission importance when lead times are affected.

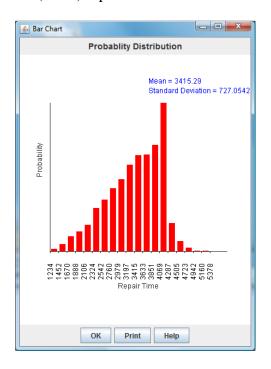

Figures 2.6 and 2.7 depict the distributions of repair time for an un-prioritized case and a prioritized case respectably. The inputs used to generate this case were a population of 400 LRUs whose failures are dictated by Weibull distribution generated TTFs. When comparing the mean repair time for the un-prioritized case versus the prioritized case, there is an 8.9% increase when assigning repair priorities to LRUs. The increase in repair time on the average repair time is because LRUs of higher priority are spending less time in repair, and are placed in the field more quickly. These LRUs

experience a greater amount of time in the field, therefore failing more often than their counterparts waiting in the repair facilities to be repaired. The double distribution shape seen in Figure 2.9 is due to the fact that higher priority LRUs have a decreased repair time (the left population), followed by LRUs of lower priority forming the population on the right. The distribution in Figure 2.8 is single and normal as the LRUs follow a first in first out (FIFO) repair rule.

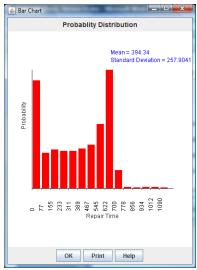

Probablity Distribution

Mean = 3722.64

Standard Deviation = 3208.601

Mean = 3722.64

Standard Deviation = 3208.601

Mean = 3722.64

Standard Deviation = 3208.601

Repair Time

OK Print Help

Figure 2.8: No Priority Sorting

**Figure 2.9: Priority Sorting**

# 2.3.2 Adding Spares/Repairing Process

In a real life situation when an LRU fails in the field, it is removed from the system and sent for repair. A spare is immediately installed in place of the original LRU to continue system operation. Upon repair, the original LRU is reinstalled and the spare is removed and replaced into storage. The time to failure clock associated with failure

mechanisms in the spare only accumulates the time the original LRU spent in the repair process.

An approximation to the real sparing process is assumed in the model. When a LRU fails and enters the repair process, a spare is assumed to replace it. However, the simulation does not accumulate time against the spare's failure mechanisms unless the spare becomes a permanent replacement for the LRU, i.e., only if the original LRU is retired during repair. The assumption is that the spares do not accumulate appreciable degradation if they are only used while the original LRUs are in repair.

#### 2.3.3 Early Retirement

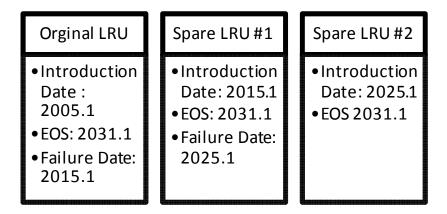

Oftentimes, an LRU will enter the repair process, pass through one or more steps and be deemed non-repairable. Early retirement is supported in the model by creating specific process steps with the capability to specify a fixed fraction or distribution of LRUs to be retired. When a failed LRU enters one of these specific process steps and is determined to be retired early, the model adds a spare LRU to replace the retired LRU. The failure date of the original LRU becomes the introduction date of the spare LRU. Prior to introduction into the field, the reliability distributions corresponding to all the relevant failure mechanisms are sampled and included in the spare LRUs properties. All other LRU specific properties of the spare, including the end of service date and priority, are the same as the originally failed LRU. The spare LRU acts with the same behavior as the original LRU, and is modeled with the same metrics. If a spare should fail and not be repairable, it will be replaced by another spare that inherits the properties of its parent. Figure 2.10 represents the relationship of LRU specific properties between the parent and child LRU.

Figure 2.10: Example of Original to Spare LRU Relationship

# 2.3.4 Branching

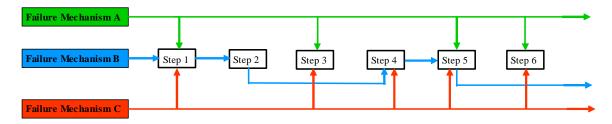

The branched step option provided in the model allows the engineer to explicitly specify the repair path as a function of the failure mechanism (and/or part type) that caused the LRU's failure. In some cases, different failure mechanisms require different repair steps. Figure 2.11 depicts how the process flow of a failed LRU can differ based on which failure mechanism causes the failure: A, B or C.

Figure 2.11: Implementation of Unique and Independent Repair Processes

The mechanism-specific capabilities of each step are stored as part of the process step object's information.

### 2.3.5 How LRUs Get in and Out of the Repair Process Flow

When a LRU fails, it is removed from the field and is placed in the first step of the repair process. This is achieved by increasing the number of LRUs by 1 in either the repair or waiting pool subsection of the queue. If the process step's repair section is under capacity and the LRU is un-prioritized it will be placed in the next sequential opening in the repair section and will be processed during the time step. If the process step's repair section is full (over capacity) and the LRU is un-prioritized it will be placed next in line within the waiting pool. The waiting pool consists of a sequential list of LRUs waiting to fill the process step's repair. If the process step's repair section is under capacity and the LRU is prioritized, the LRU will be placed at the top of its priority type within the repair section. If there are no LRUs of that priority type, it will be placed at the end of the line following the next highest priority rating. If the process step's repair section is full (over capacity) and the LRU is prioritized, it will be placed next in line, following an LRU with equivalent priority rating, within the waiting pool.

# 2.3.6 Time Step Selection and Management

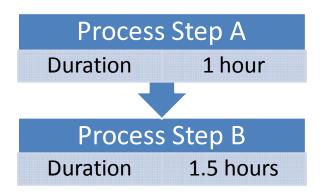

The process of determining the time step value (length) is controlled by two factors, the required accuracy of the simulation and the duration (time) of each repair process step. To obtain the best accuracy and minimize the run-time of the simulation, the size of the time step is set to the greatest common divisor (GCD) of the process step duration during the repair process and the difference of the soonest time to failure (TTF)

and the current date when there are no LRUs in the repair process. This concept is explained in Figure 2.12, which depicts two process steps with unique repair durations.

Figure 2.12: Example Process Steps with different durations

The simulation time operates by beginning at the "start" time, or earliest LRU introduction date and advances by the addition of the time step. In the case shown in Figure 2.12 with two process steps, with durations of 1 and 1.5 hours respectably, the user may choose to use a "1 hour" time step as it is the smallest process step. In this case the clock advances 1 hour, and the LRU passes through process step A. Entering process step B, the clock must advance two full time steps before the LRU can move out of the step. This time step size therefore increased the total repair time to 3.0 hours versus the correct time of 2.5 hours. To avoid this error, the time step must be the lowest common denominator of the process step durations. Taking the above example, the GCD of the two process steps would be ½ hour. Upon entering the repair process, the model advances two time steps before removing the LRU from process step B obtaining the correct total repair time of 2.5 hours.

While accuracy of the model is always important, it may be traded off against computational speed. However, there are ways of increasing the speed of the simulation

by reducing the number of computations without negatively impacting the accuracy. When there are no events occurring in the simulation, i.e., when no LRUs are failing or are in the repair process, there is no need to sort each repair process step queue or the array of LRU TTFs. The simulation determines the gap until the next event, and jumps to the next event. This is the part of the event stepped method that advances time when the discrete events of the model are the LRU failures.

In order to determine the next discrete event, the model must first determine whether there is a LRU in the repair queue. If there is, the step size is set to the GCD of the process step duration by default. If there are no LRUs in the repair process, the simulation calls on a stored array of TTF distributions for each LRU, sorts this array by ascending date and determines the soonest future TTF event. The difference between this TTF date and the current date is the new time step. The size of this step can potentially range from the GCD of the process flow to many years. This time step has the ability to be large because the simulator is jumping to a date when there will be LRUs in the repair queue. When a LRU enters the repair queue, the time step is set to the fixed value, determined by the GCD of the process step durations. This fixed value time represents each individual event in the repair process.

# 2.3.7 The Impact of Low Capacity Process Steps on the Total Repair Time

The electronic repair process in a discrete event simulator is initiated by a single or group of failed LRUs. The failed LRU is placed into the first step of the repair process, remains there for the step's duration, and is then transferred into the next process step upon completion of the step. This release of the LRU from the first process step is

dependent on both the process step's duration and its capacity. The process step's duration is the minimum time that each LRU must spend in that process step. The maximum time spent in the repair process step is dependent on the step's capacity or capability to repair multiple LRUs simultaneously. The capacity of the process step is the maximum number of LRUs that can be handled in that process step concurrently. Therefore, a process step with a high capacity will only occupy the LRU for the step's defined duration. However, a process step that has a capacity lower than the total number of LRUs entering the repair process will backup LRUs and increase the overall LRU repair time. The example repair process with three steps A, B and C used to demonstrate the negative impact of a process step with characteristics of a low capacity and a small duration is represented by Figure 2.13.

Figure 2.13: Example Process Steps

Each process step has a unique duration and capacity. For this case, 50 LRUs have just failed, and the user is running a 1-hour time step in the model. After one time step, all 50 LRUs have completed 50% of repair step A. After the second time step, all 50 LRUs have completed 100% of repair step A, and have moved into repair step B. Due to repair step B's small capacity (2 LRUs), after the third time step, LRUs will begin to

back up in repair step B's queue. The minimum time needed to complete the entire repair process for a single LRU is 6 hours for the above case. Figure 2.14 illustrates the LRU number versus the repair time for each of the 40 LRUs sampled in this example.

Figure 2.14: Total Repair Time (hours) for LRUs 1-40 in the example process shown in Figure 2.13

In Figure 2.12, when a process step has a small capacity it can have significant repercussions on the duration a LRU remains in repair. The time spent in the repair process modeled in Figure 2.11 increases rapidly from the minimum time of 6 hours to nearly 25 hours for LRU #40 due to time spent waiting to enter the repair section.

#### 2.4 Outputs

# 2.4.1 Average Cost per LRU

In this model, the cost being calculated represents only a subset of the total ownership cost of a LRU. The specific subset being described in this model is the cost of

maintaining LRUs in the field, i.e., the cost to repair. Other costs associated with the LRU are not addressed in this model.

The repair cost per LRU is calculated by summing the cost of each repair step that the LRU was processed in. However, the cost of the repair step represented by the value specified in the repair process is the cost of performing the step during the first year. A discount rate, or time value of money is taken into account for repairs that occur past the first year. In Equation 2.3, the cost of the repair step is calculated based on the date (in years) of the repair.

$$Present Value of Repair Step = \frac{Orginal Value of Repair Step}{(1 + Discount Rate)^{Year}}$$

(2.3)

The number of process steps that each LRU enters, is dependent on the mechanism that caused failure. LRUs may fail more than once, therefore be repaired more than once, and possibly follow different repair branches each time it is repaired. The possibility for different repair costs suggests calculating an average repair cost per LRU. In Equation 2.4, the average cost per LRU is calculated by summing the individual repair costs per LRU and dividing by the total number of LRUs.

$$Average Repair Cost per LRU = \frac{\sum Repair Cost per LRU}{Total Number of LRUs}$$

(2.4)

# 2.4.2 Average Repair Time

The repair time represents the time required for an LRU to move through a particular repair process and any extra time spent waiting to enter the repair area. The specific repair process is determined by the mechanism that caused failure and the type of part. Therefore failure caused by vibration in a 2512 resistor is processed differently than a NFF (no fault found) failure in a CTBGA.

The repair time is calculated by summing the individual times the LRU spends in each repair step, either while being repaired or time spent in the waiting pool. In Equation 2.5, the average repair time per LRU is calculated by summing the repair time for each LRU and divided by the total quantity of LRUs.

Average Time In Repair per

$$LRU = \frac{\sum Time\ In\ Repair\ per\ LRU}{Total\ Number\ of\ LRUs}$$

(2.5)

# 2.4.3 Availability

Availability is the probability that an item will be able to function (i.e., not failed or undergoing repair) when called upon to do so. Availability is a function of an item's reliability (how quickly it fails) and its maintainability (how quickly it can be repaired and/or how it is spared). Quantitatively, availability is given by,

$$Availability = \frac{Up \ time}{Up \ time + Down \ time} \tag{2.6}$$

The concept of availability marries reliability and maintainability together and only applies to "repairable" systems.

Within this model, availability is defined as the fraction of time the LRU is available for field use and is calculated on the LRU level versus the system level.<sup>5</sup> From this perspective, availability is only a function of total time in the field and the total repair time. In order to calculate the average LRU availability, the individual LRU availability must first be calculated. The individual LRU availability is calculated in Equation 2.7 by subtracting the total time in the field by the total repair time and dividing this by the total time in the field.

\_

<sup>&</sup>lt;sup>5</sup> Availability can be evaluated either for the LRUs or for the "sockets." Sockets are the places in a system where the fielded LRUs are located. In this thesis, only the availability of the LRUs is considered.

$$LRU \ Availability = \frac{\sum Time \ In \ Field - \sum Time \ In \ Repair}{\sum Time \ In \ Field}$$

(2.7)

To calculate the average availability, Equation 2.8 sums each individual LRU's availability and divides by the total number of LRUs in the system.

$$Average LRU \ Availability = \frac{\sum LRU \ Availability}{Total \ Number of \ LRUs}$$

(2.8)

In comparison, for the above repair process, it took only 6 hours to repair the first LRU and 25 hours to repair the  $40^{th}$  LRU.

# 2.5 Model Summary

The model described in this chapter communicates the impact of the tin-lead to lead-free electronics conversion in terms of repair cost and LRU availability. These effects are used to quantify and demonstrate the system- and enterprise- level risks posed by the tin-lead to lead-free conversion issue. The procedure for utilizing the model is shown in Figure 2.13. In Chapter 3, detailed test cases are developed and example results from the test cases are discussed.

Figure 2.15: Usage Procedure for the Model

# Chapter 3: Model Test Case

In order to exercise the model developed in Chapter 2 test cases were developed. The test cases implement a range of different electronic components of various sizes and package types and were assessed for both tin-lead and lead-free solder finishes. The objective of the test cases is twofold: 1) to demonstrate the capability of the model, and 2) to assess the cost and availability impact of the conversion from tin-lead to lead-free and for a range of conditions.

# 3.1 Test Case Development

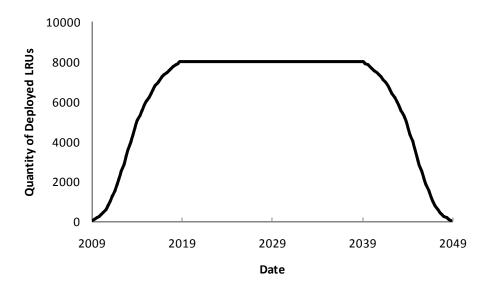

The model test cases track 8,000 LRU level avionics boards from introduction to retirement. Each of the 8,000 LRUs were tracked entirely independent of each other. The test cases require three basic inputs:

- 1) Logistics Inputs: Introduction and retirement schedules for the LRUs (how many are fielded, when they are fielded and when they are retired from the field)

- 2) Relevant failure mechanisms for the LRUs (including reliability distributions)

- 3) The repair process that will be used for the LRUs (process steps including durations and capacities)

The following subsections describe the development of the input data for the test cases.