#### **ABSTRACT**

Title of Document: A PHYSICS OF FAILURE BASED

QUALIFICATION PROCESS FOR FLEXIBLE DISPLAY INTERCONNECT MATERIALS.

Thomas Andrew Martin, Doctor of Philosophy,

2011

Directed By: Dr. Aris Christou,

Professor,

Department of Mechanical Engineering,

University of Maryland

The next paradigm shift in display technology involves making them flexible,

bringing with it many challenges with respect to product reliability. To compound the

problem, industry is continuously introducing novel materials and experimenting with

device geometries to improve flexibility and optical performance. Hence, a method to

rapidly qualify these new designs for high reliability applications is imperative.

This dissertation involves the development of a qualification process for gate line

interconnects used in flexible displays. The process starts with the observed failure

mode of permanent horizontal lines in the displays, followed by the identification of

the underlying failure mechanism. Finite element analyses are developed to determine

the relationship between the physical flexing and the mechanical stress imposed on

the traces. The design of an accelerated life test is performed based on the known

agent of failure being cyclic bending that induces a tensile strain. A versatile dedicated test system is designed and integrated in order to rapidly capture changes in resistance of multiple traces during test. Dedicated test structures are also designed and fabricated to facilitate in-situ electrical measurements and direct observations.

Since the test structures were consumed during the integration of the test system, random failure times are used in the process of determining a life-stress model. Different models are compared with respect to their applicability to the underlying failure mechanism as well as parameter estimation techniques.

This methodology may be applied towards the rapid qualification of other novel materials, process conditions, and device geometries prior to their widespread use in future display systems.

# A PHYSICS OF FAILURE BASED QUALIFICATION PROCESS FOR FLEXIBLE DISPLAY INTERCONNECT MATERIALS

By

Thomas Andrew Martin.

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2011

Advisory Committee: Professor Aris Christou, Chair Professor Neil Goldsman Professor Martin Peckerar Associate Professor Jeffrey Hermann Associate Professor Teng Li © Copyright by Thomas Andrew Martin 2011

## Dedication

I would like to dedicate this to my family. First and foremost, my wife Mindy – without your understanding and support this would not have been possible. To my daughter Jennifer – I hope this inspires you to never give up. To my parents – for giving me a solid foundation to become a man and staying alive to see this day. To my brother, my two sisters, my nieces and nephews, and my close friends – I am thankful that you are all an integral part of my life. I know this was a long time coming, but I had to fight the good fight and here we are.

As thanks, I hope that none of you are ever required to read this document.

## Acknowledgements

First and foremost, I would like to thank Dr. Christou for his time, dedication, and patience. Given that I was a distance student, this would not have been possible without Dr. Christou's countless hours of interaction over the phone and through email. His guidance has helped me grow not only as a researcher but more importantly as a person.

In addition, I would like to thank Dr. Goldsman, Dr. Peckerar, Dr. Hermann, and Dr. Li for serving on my committee and providing valuable comments to improve my dissertation.

I would also like to thank Eric Forsythe of the Army Research Laboratory for providing advice on research topics, the staff at the Flexible Display Center, especially Shawn O'Rourke for providing sample devices, and my fellow colleagues at L-3 Display Systems for their support (Dave Huffman, Derek Greene, Carrie Whitehead, Justin Bolin, and Jim McIntyre).

Finally, I would like to thank all my teachers for not only teaching me what to learn but how to learn. I would like to highlight Dr. W. Marshall Leach of Georgia Tech who unfortunately passed away in late 2010 prior to seeing me earn my degree.

## Table of Contents

| Dedication   |                                                    | ii       |

|--------------|----------------------------------------------------|----------|

|              | lgements                                           |          |

| Table of Co  | ontents                                            | iv       |

| List of Tab  | les                                                | 1        |

| List of Figu | ures                                               | 2        |

| Chapter 1:   | Introduction                                       | 5        |

| 1. Ove       | erview                                             | 5        |

| 1.1.         | History of Display Technologies                    | <i>6</i> |

| 1.1.1.       |                                                    |          |

| 1.1.2.       | 1 1 1                                              | 8        |

| 1.2.         | Advanced Display Technologies Enabling Flexibility | 10       |

| 1.2.1.       | Emissive Displays                                  | 11       |

| 1.2.2.       | Reflective Displays                                | 13       |

| 1.2.3.       | Transmissive Displays                              | 15       |

| 1.3.         | Theory of Operation                                | 15       |

| 1.3.1.       | Basic Fabrication Steps                            | 16       |

| 1.3.2.       | Electrical Operation of Display                    | 18       |

| 1.3.3.       | Pixel Layout                                       | 19       |

| 1.3.4.       | Thin Film Transistor                               | 21       |

| 1.3.5.       | Gate Line Interconnects                            | 23       |

| 1.3.6.       | Transistor Operation                               | 23       |

| 1.4.         | Field Conditions for Flexible Displays             | 26       |

| 1.5.         | Reliability Problem as Observed by the End User    | 28       |

| 1.6.         | Failure Mode and Effects Analysis                  | 29       |

| 1.7.         | Identification of Specific Failure Mode            | 32       |

| 1.8.         | Criteria for Failure                               |          |

| 1.9.         | Statement of Problem                               | 36       |

| 1.10.        | Motivation and Contribution of this Thesis         | 38       |

| Chapter 2:   | Analysis of Failure Mechanism                      | 39       |

| 2. Ove       | erview                                             | 39       |

| 2.1.         | Characterization of the Failure Mode               | 40       |

| 2.1.1.       | Cracks in Gate Line Interconnect Thin Film         | 41       |

| 2.1.2.       | Series Resistance Model                            | 43       |

| 2.2.         | Fracture of Thin Films                             | 46       |

| 2.2.1.       | Thin Films in Compression                          | 47       |

| 2.2.2.       | Thin Films in Tension                              |          |

| 2.2.3.       | Channel Cracking as a Result of Induced Stress     | 49       |

| 2.3.         | Properties of Materials Used in Investigation      | 57       |

| 2.3.1.       | PEN Substrate                                      | 58       |

| 2.3.2.       | SiN Buffer Layer                                   | 59       |

| 2.3.3.       | ITO Gate Layer                                     | 60       |

| 234          | Summary of Material Properties                     | 67       |

| 2.4.         | Internal Fabrication Stress Specific to this Investigation     | 67  |

|--------------|----------------------------------------------------------------|-----|

| 2.4.1.       | Theory of Internal Stresses                                    |     |

| 2.4.2.       | Internal Stresses Using a Stiff Substrate                      | 70  |

| 2.4.3.       | Internal Stresses Using a Compliant Substrate                  | 71  |

| 2.4.4.       | Finite Element Analysis of Internal Stresses                   |     |

| 2.5.         | External Stress and Strain from Bending                        | 75  |

| 2.5.1.       | Theory based on Simple Two Layer System                        |     |

| 2.5.2.       | Results of ANSYS Model                                         |     |

| 2.6.         | Summary of Failure Mechanism                                   | 78  |

| 2.6.1.       | Influence of Key Parameters on Three Different Stresses        | 79  |

| 2.6.2.       | Summary Calculation of Stresses                                |     |

| 2.6.3.       | Conclusions                                                    | 82  |

| Chapter 3: 1 | Previous Reported Investigations                               | 83  |

| 3. Ove       | erview                                                         | 83  |

| 3.1.         | Strain to failure methods                                      | 83  |

| 3.1.1.       | Uniaxial Tensile method                                        | 84  |

| 3.1.2.       | Two point bending method                                       | 85  |

| 3.1.3.       | Biaxial method                                                 | 87  |

| 3.1.4.       | Observations of failure patterns for the three methods:        | 88  |

| 3.1.5.       | Analysis of results between Uniaxial and Two Point Bending     | 90  |

| 3.1.6.       | Analysis of Fragment Length                                    | 91  |

| 3.1.7.       | Patterned ITO lines on flexible substrates                     | 92  |

| 3.2.         | Cyclic Testing Method                                          | 93  |

| 3.3.         | Critique of Previous Investigations                            | 96  |

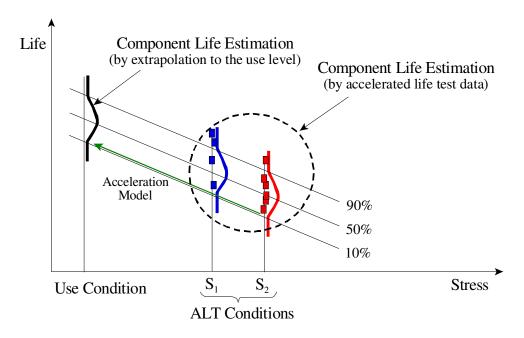

| 3.4.         | Rationale for Performing an Accelerated Life Test              | 97  |

| Chapter 4: 1 | Design of Accelerated Life Test                                | 98  |

| 4. Ove       | erview                                                         | 98  |

| 4.1.         | Rationale for Accelerated Life Testing                         | 98  |

| 4.2.         | Key Components of an Accelerated Life Test                     | 101 |

| 4.2.1.       | Types of Responses                                             | 101 |

| 4.2.2.       | Acceleration Models                                            | 102 |

| 4.2.3.       | Acceleration Factor                                            | 104 |

| 4.3.         | Accelerating the Failure Mechanism                             | 105 |

| 4.3.1.       | Types of Failure Mechanisms                                    |     |

| 4.3.2.       | Types of Applied Stress (Agent of Failure)                     | 106 |

| 4.3.3.       | Methods for Applying Stress                                    |     |

| 4.3.4.       | Methods of Acceleration                                        | 108 |

| 4.4.         | Cyclic Fatigue as the Specific Method of Acceleration          | 110 |

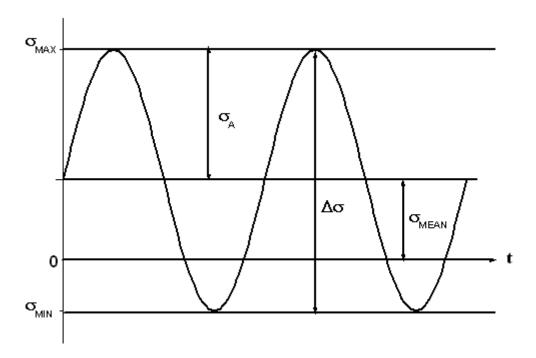

| 4.4.1.       | Constant Amplitude Cyclic Loading                              | 110 |

| 4.4.2.       | Specifics of Cyclic Loading for this Investigation             | 112 |

| 4.5.         | Test Structure Attributes Required to Support the Test         |     |

| 4.6.         | Summary of Accelerated Life Test in Context with Investigation |     |

| Chapter 5: 1 | Dedicated Test System                                          |     |

| 5. Ove       | erview                                                         | 117 |

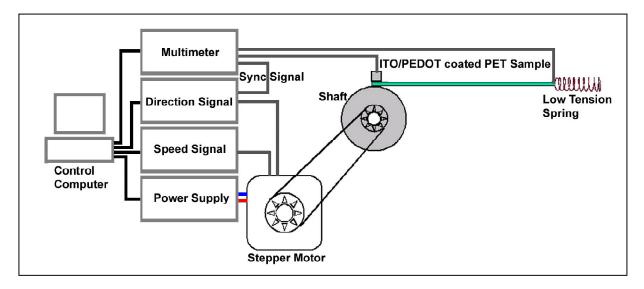

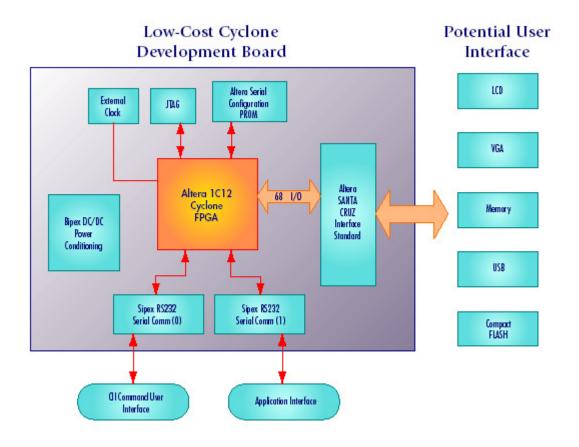

| 5.1.         | System overview                                                | 117 |

| 5.2.         | Labview Program.                                               |     |

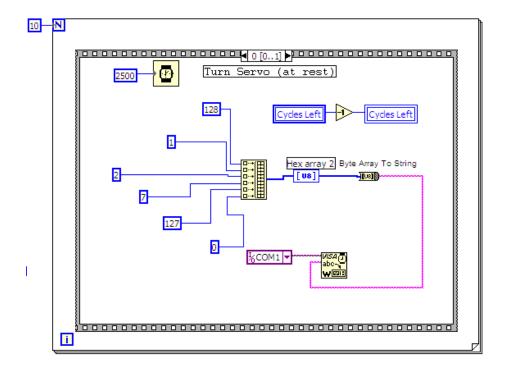

| 5.2     | .1. Rotation Around Mandrel                          | 120 |

|---------|------------------------------------------------------|-----|

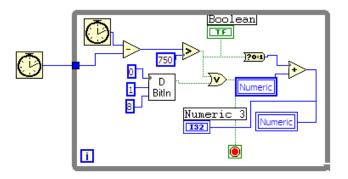

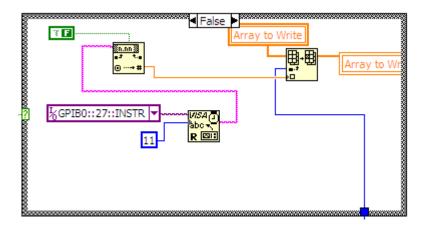

| 5.2     | .2. Discrete Interface Controller                    | 120 |

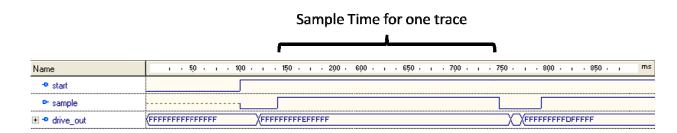

| 5.2     | .3. FPGA Card                                        | 122 |

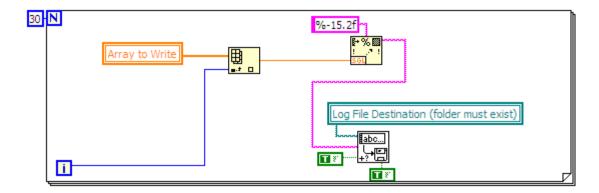

| 5.2     | .4. Store Data and Return Substrate to Relaxed State | 125 |

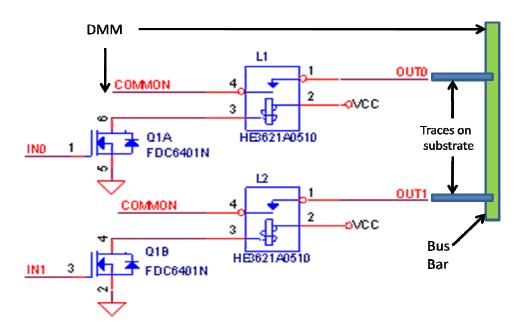

| 5.3     | . Driver Card                                        | 127 |

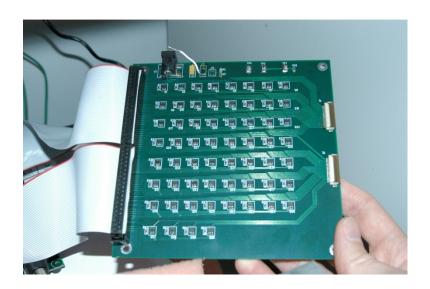

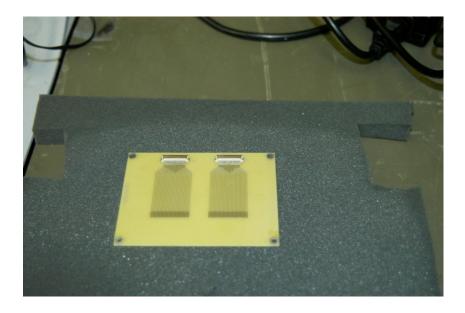

| 5.4     | . TAB Bonding Card                                   | 128 |

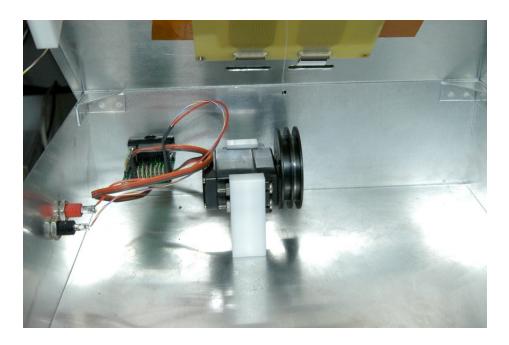

| 5.5     | . Mechanical Fixture                                 | 132 |

| 5.6     | . Verification of Dedicated Test System              | 137 |

| 5.6     | .1. Initial Sporadic Resistance Readings             | 137 |

| 5.6     | .2. Continued Sporadic Resistance Readings           | 138 |

| 5.6     | .3. Rapid Open Circuit Conditions                    | 138 |

| 5.6     | .4. Form Factor                                      | 139 |

| 5.6     | .5. Trace Failure During Calibration                 | 140 |

| 5.6     | .6. Excessive Stress on Motor                        | 140 |

| 5.6     | .7. Premature Meter Lead Fatigue                     | 140 |

| 5.6     | .8. Slippage of Clamp Assembly                       | 141 |

| 5.6     |                                                      |     |

| 5.7     |                                                      |     |

| Chapter | 6: Life Test Data Analysis                           |     |

| _       | Overview                                             |     |

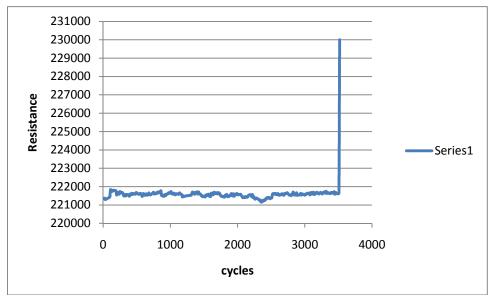

| 6.1     | . Resistance Calculation                             | 143 |

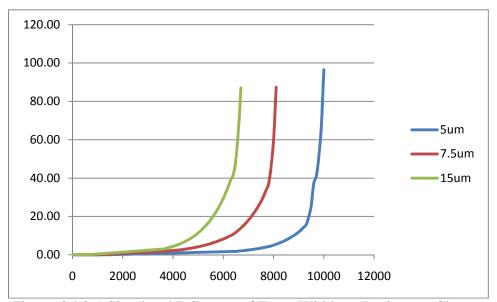

| 6.2     | . Definition of Failure Based on Trace Width         | 144 |

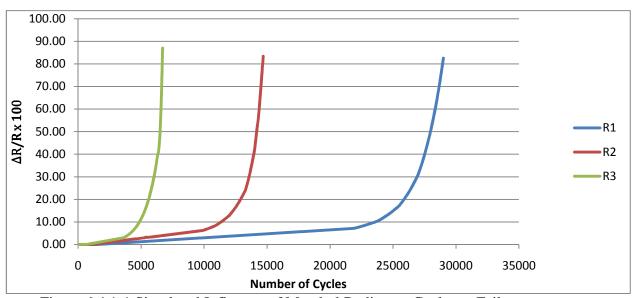

| 6.3     | . Cycles to Failure Data                             | 145 |

| 6.4     | Process for Analyzing Life Test Data                 | 146 |

| 6.4     |                                                      |     |

| 6.4     | · · · · · · · · · · · · · · · · · · ·                |     |

| 6.5     | . Summary of Data Analysis                           | 149 |

| Chapter | 7: Life-Stress Model Analysis                        | 150 |

| 7.      | Overview                                             | 150 |

| 7.1     | . Life Distributions                                 | 150 |

| 7.1     | .1. Exponential Distribution                         | 150 |

| 7.1     | .2. Weibull Distribution                             | 152 |

| 7.1     | .3. Lognormal                                        | 153 |

| 7.2     |                                                      |     |

| 7.2     |                                                      | 155 |

| 7.2     |                                                      | 157 |

| 7.2     |                                                      | 157 |

| 7.2     | .4. Coffin-Manson and the IPL Relationship           | 158 |

| 7.3     | . Modeling Fatigue                                   | 159 |

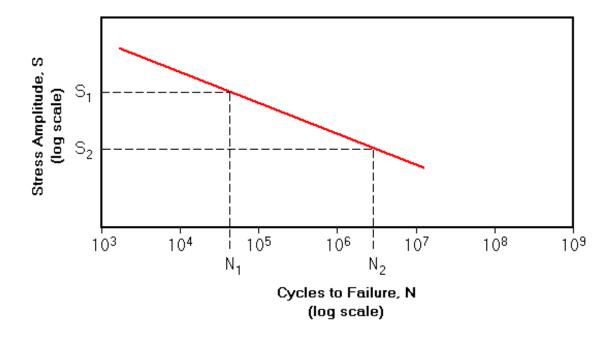

| 7.3     | .1. Stress-Life                                      | 159 |

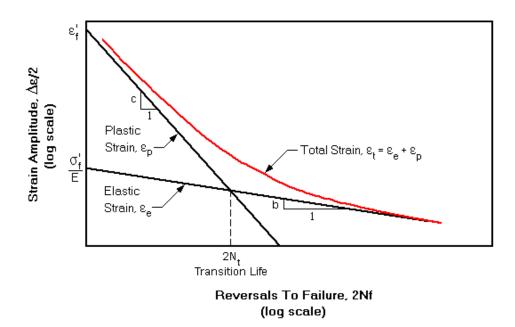

| 7.3     | .2. Strain-Life                                      | 161 |

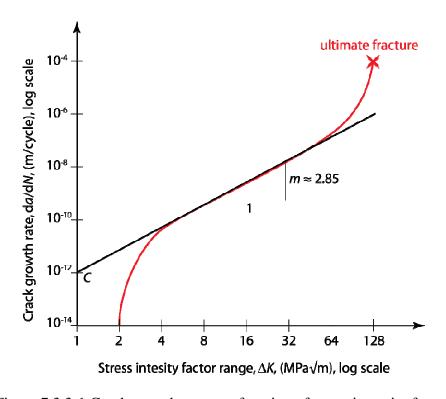

| 7.3     | .3. Fracture Mechanics                               | 163 |

| 7.3     | .4. Comparison of Fatigue Models                     | 165 |

| 7.4     | 1 6                                                  |     |

| 7.4     | <u> •</u>                                            |     |

| 7.4     | .2. Maximum Likelihood Estimation                    |     |

| 7.4.3.       | Bayesian Analysis                             | 170 |

|--------------|-----------------------------------------------|-----|

| 7.4.4.       | Comparison of Parameter Estimation Techniques | 170 |

| 7.5.         | Analysis of Models Based on Life Data         | 170 |

| 7.6.         | Summary of Resulting Life-Stress Model        | 173 |

| Chapter 8: 0 | Conclusions and Future Research               | 175 |

| 8. Ove       | rview                                         | 175 |

| 8.1.         | Summary of Results                            | 175 |

| 8.2.         | Contributions                                 | 179 |

| 8.3.         | Future Research                               | 182 |

| 8.4.         | Closing Remarks                               | 186 |

| Appendix A   | 1                                             | 187 |

| 1 1          |                                               |     |

# List of Tables

| Table 1.6-1 Failure modes that result in horizontal line-outs                    | 31  |

|----------------------------------------------------------------------------------|-----|

| Table 2.3.1-1 Listing of material properties of PEN substrate                    | 58  |

| Table 2.3.3-1 Electrical properties of ITO films deposited on PET                | 61  |

| Table 2.3.4-1 Summary of Material Properties and Process Conditions              | 67  |

| Table 2.6.1-1 Summary of Key Parameters on the Three Stress Types                | 80  |

| Table 2.6.2-1 Summary of Parameter Values to Calculate Intrinsic Critical Stress | 81  |

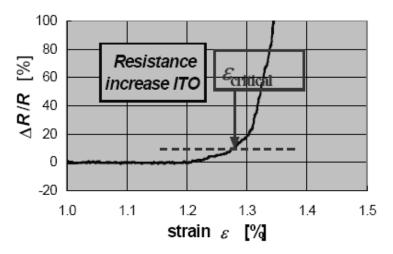

| Table 3.1.5-1 Crack onset Strain (COS) of ITO layers                             | 91  |

| Table 3.1.7-1 COS and modulus for different ITO trace widths                     | 93  |

| Table 3.3-1 Comparison of different test methods                                 | 97  |

| Table 4.3.1-1 Categorization of Failure Mechanisms and Related Stresses          | 106 |

| Table 4.4.2-1 Cyclic Loading Profile for each of the Three Life Tests            | 112 |

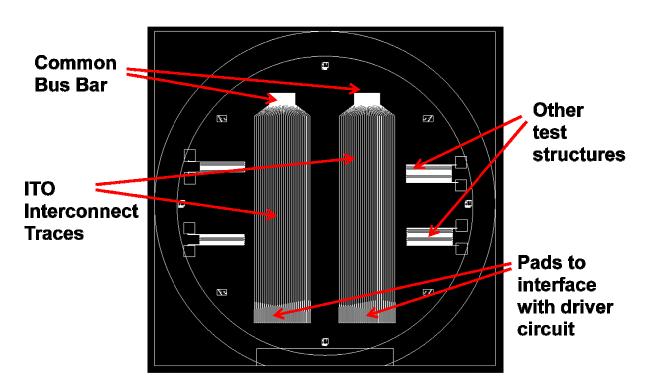

| Table 4.5-1 Configuration of ITO traces                                          | 115 |

| Table 5.1-1 Parts List of dedicated test system                                  | 118 |

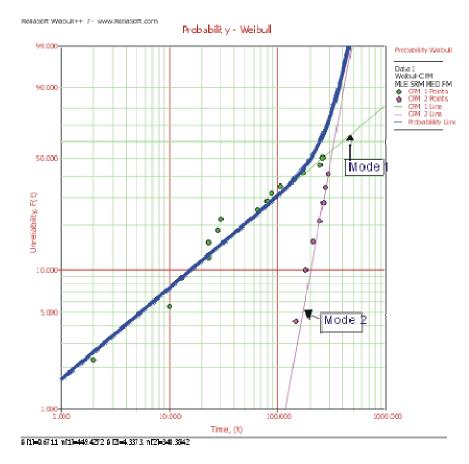

| Table 7.5-1 Comparison of Weibull and Lognormal goodness of fit                  | 171 |

| Table 7.5-2 Weibull parameter estimation for 15um trace data                     | 172 |

# List of Figures

| Figure 1.1.1-1 Breakdown of an image on a CRT display                              | 6    |

|------------------------------------------------------------------------------------|------|

| Figure 1.1.1-2 Cross section of cathode ray tube                                   |      |

| Figure 1.1.1-3 Shadow mask of cathode ray tube                                     | 8    |

| Figure 1.1.2-1 Optical stack up of an Active Matrix Liquid Crystal Display         | 9    |

| Figure 1.2.1-1 Cross section of Organic Light Emitting Device (OLED)               | . 11 |

| Figure 1.2.1-2 Operation of an Organic Light Emitting Device                       | . 12 |

| Figure 1.2.2-1 Cross section of Electrophoretic display                            | . 14 |

| Figure 1.2.2-2 Electrophoretic display in an electronic paper application          | . 14 |

| Figure 1.3-1 Picture of electrophoretic display manufactured by FDC                | . 15 |

| Figure 1.3.1-1 Cross section of Standard Flexible Display                          | . 16 |

| Figure 1.3.1-2 Photograph of display on stainless steel substrate                  | . 18 |

| Figure 1.3.2-1 Schematic Diagram of gate/source (row/column) drive signals         |      |

| Figure 1.3.3-1 Diagram of one pixel                                                | . 20 |

| Figure 1.3.3-2 Schematic diagram of pixel                                          | . 21 |

| Figure 1.3.4-1 Cross section of entire pixel                                       |      |

| Figure 1.3.4-2 Detailed cross section of thin film transistor                      | . 22 |

| Figure 1.3.5-1 Gate layer after etching process                                    | . 23 |

| Figure 1.3.6-1 I <sub>DS</sub> versus V <sub>DS</sub> characteristics of TFT       | . 25 |

| Figure 1.3.6-2 I <sub>DS</sub> versus V <sub>GS</sub> characteristics of TFT       | . 25 |

| Figure 1.4-1 Pictures of wrist display conformed one time to a set radius          |      |

| Figure 1.4-2 Example of field use conditions for flexible displays                 |      |

| Figure 1.5-1 Example of failure condition "line outs"                              |      |

| Figure 1.6-1 Diagram of FMEA Elements                                              |      |

| Figure 1.8-1 Schematic Diagram of SPICE Model                                      |      |

| Figure 1.8-2 SPICE Model Output Showing Correct Operation                          |      |

| Figure 1.8-3 SPICE Model Output Showing Failure Condition                          |      |

| Figure 2.1.1-1 SEM Micrograph of Cracks in ITO Thin Film                           |      |

| Figure 2.1.1-2 Cracks in Film of Gate Line Interconnects                           |      |

| Figure 2.1.2-1 Diagram Showing Bridging Material Inside a Crack                    |      |

| Figure 2.2-1 Common Types of Fracture in Thin Films                                |      |

| Figure 2.2.1-1 De-lamination of Thin Film Under Compression                        |      |

| Figure 2.2.2-1 Initial Flaw and Growth of Crack in Thin Film Under Tension         |      |

| Figure 2.2.3-1 Channel Cracking in Thin Film Under Tension                         |      |

| Figure 2.2.3-2 Steady State Growth of Channel Crack                                |      |

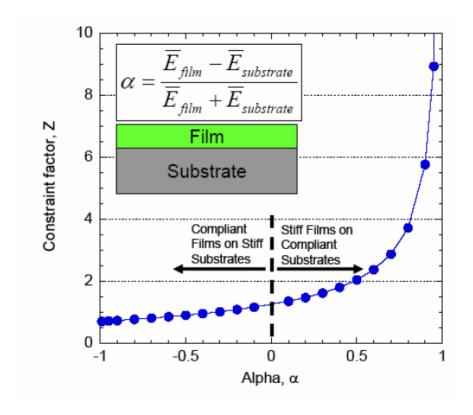

| Figure 2.2.3-3 Z as a Function of $\alpha$ with $\beta = \alpha/4$ [Lu 2006]       |      |

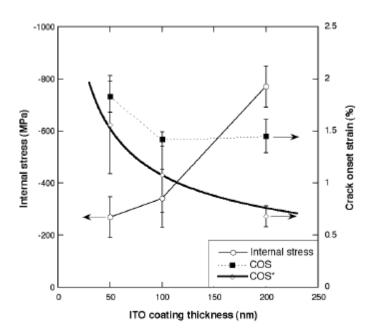

| Figure 2.2.3-4 Impact of film thickness on intrinsic crack onset strain            |      |

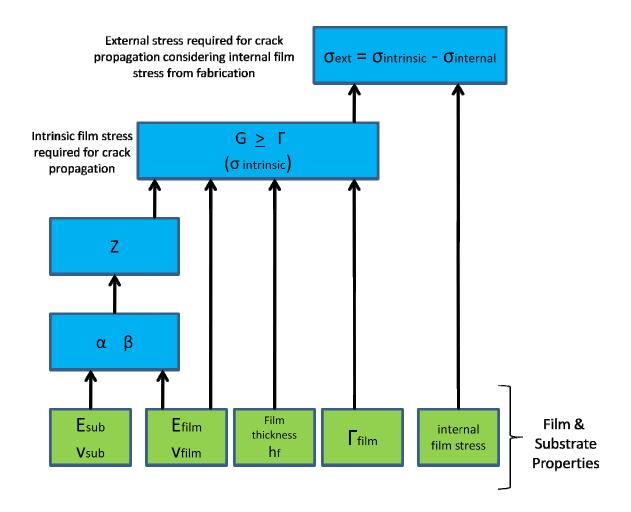

| Figure 2.2.3-5 Relationship of Film and Substrate Properties to crack propagation. |      |

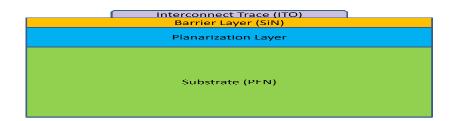

| Figure 2.3-1 Cross section of device layers critical to failure mechanism          |      |

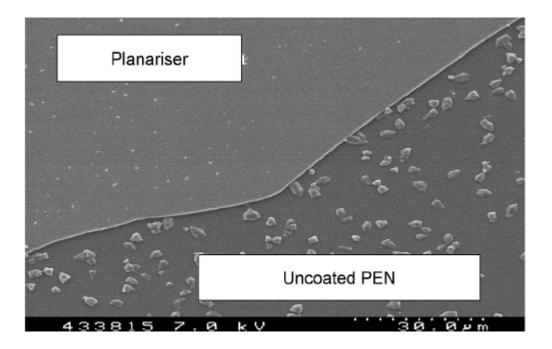

| Figure 2.3.1-1 Surfaces of PEN film (Planarized versus Unplanarized)               |      |

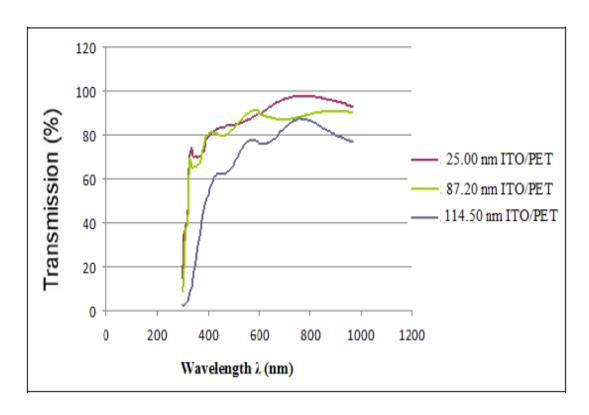

| Figure 2.3.3-1 Optical transmittance (T) of ITO films deposited on PET             |      |

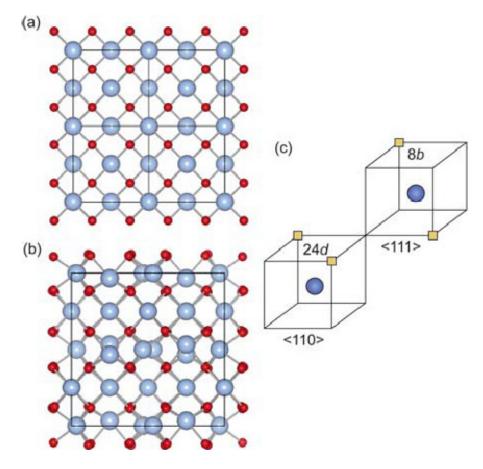

| Figure 2.3.3-2 Structures of (a) fluorite, (b) bixbyite, and (c) anion vacancies   |      |

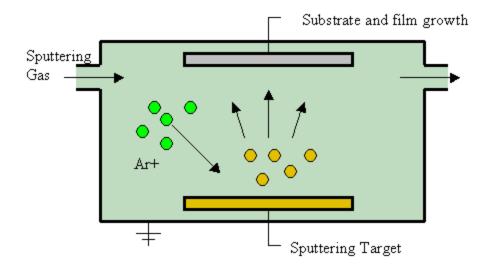

| Figure 2.3.3-3 Diagram of sputtering process                                       |      |

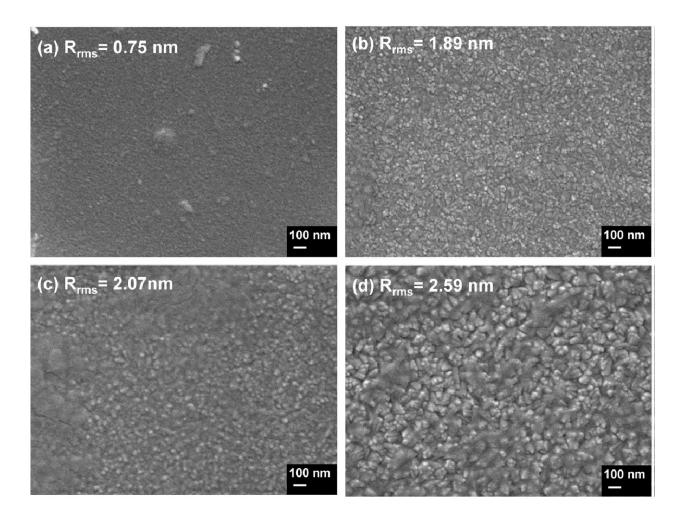

| Figure 2.3.3-4 SEM micrographs of varying ITO film thicknesses                     |      |

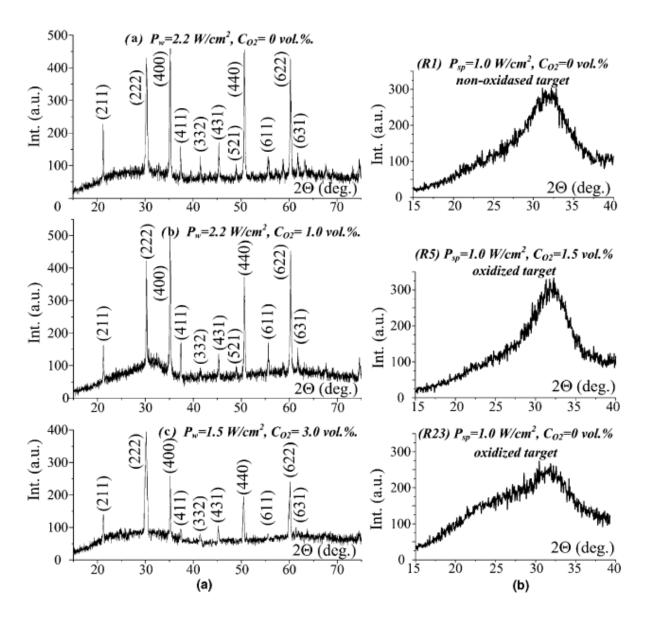

| Figure 2.3.3-5 XRD of ITO deposited by RF (a) and DC (b) magnetron sputtering.     |      |

| 2                                                                                  |      |

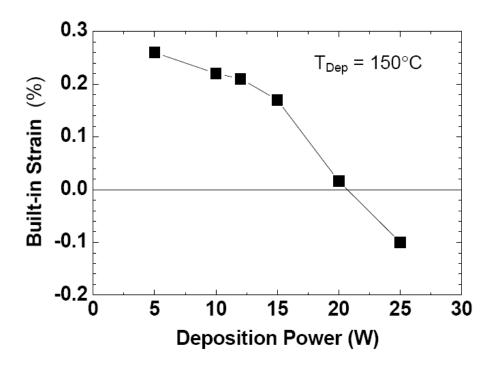

| Figure 2.4.1-1 Relationship between Deposition Power and Built-in Strain                 | . 70 |

|------------------------------------------------------------------------------------------|------|

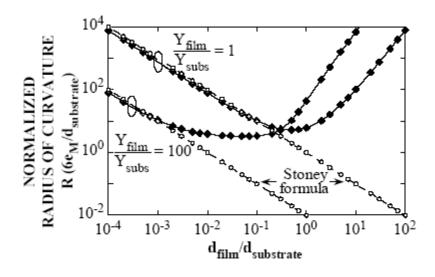

| Figure 2.4.3-1 Stoney formula versus Equation 2.4.3-2                                    | . 72 |

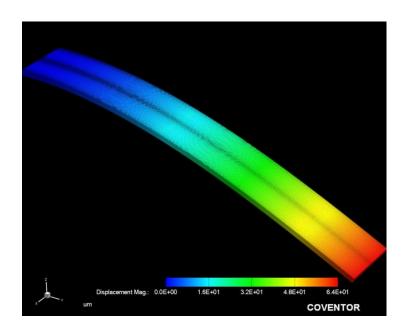

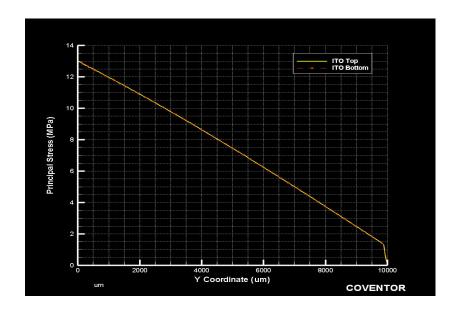

| Figure 2.4.4-1 Coventor Finite Element Model of a single ITO strip                       | . 74 |

| Figure 2.4.4-2 Principal built-in internal stress in ITO film from fabrication           | . 74 |

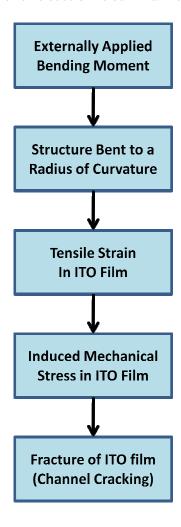

| Figure 2.5-1 Relationship of Applied Bending Moments to Film Fracture                    | . 75 |

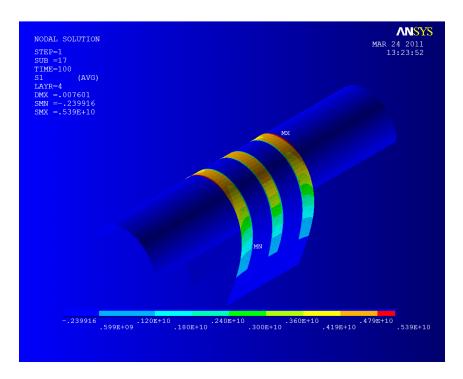

| Figure 2.5.2-1 ANSYS FEA of Structure Bent to a Radius of 0.25 Inches                    | . 77 |

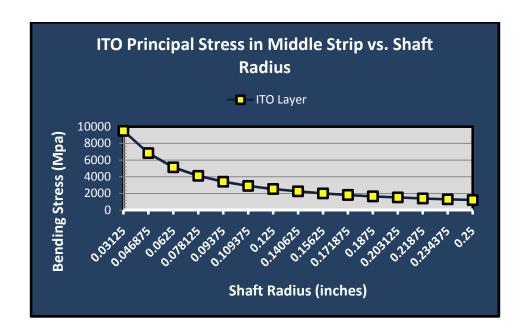

| Figure 2.5.2-2 Principal Stress as a Function of Bending Radius                          | . 78 |

| Figure 3.1-1 Graphical representation of historical COS                                  | . 84 |

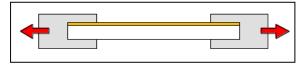

| Figure 3.1.1-1 Overview sketch showing uniaxial testing method                           | . 85 |

| Figure 3.1.1-2 Detailed mounting sketch for uniaxial testing method                      |      |

| Figure 3.1.2-1 Sketch of two point bending method                                        | . 86 |

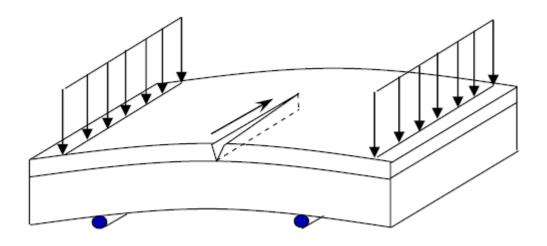

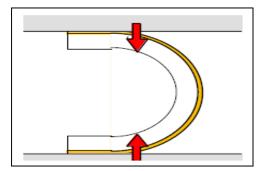

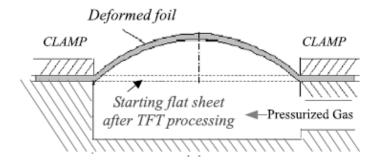

| Figure 3.1.3-1 Sketch of bulge test method                                               | . 87 |

| Figure 3.1.3-2 Polyimide foil with a-Si/SiN islands after deformation                    | . 87 |

| Figure 3.1.4-1 Cracking of ITO under % strain: 0 (a); 1.28 (b); 1.42 (c); 3.42 (d)       | . 89 |

| Figure 3.1.4-2 Fragmentation of SiOx coating under strain: $2.6\%$ (a) and $3.6\%$ (b) . | . 90 |

| Figure 3.1.6-1 Fragmentation patterns of ITO with increasing strain                      | . 92 |

| Figure 3.2-1 Sketch of cyclic mandrel test method                                        | . 94 |

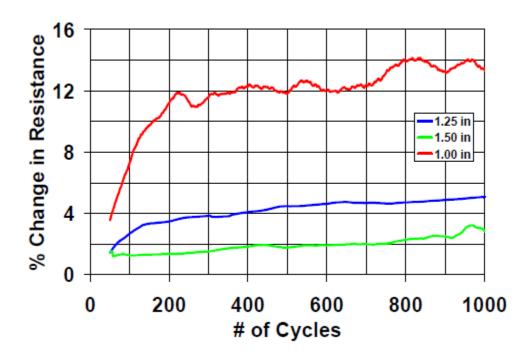

| Figure 3.2-2 Resistance change per cycle for three mandrel sizes                         | . 95 |

| Figure 3.2-3 Resistance change per cycle showing three regimes of change                 | . 95 |

| Figure 4.1-1 Graphical example of component life at different stress levels              | 100  |

| Figure 4.4.1-1 Generic Profile for Constant Amplitude Cyclic Loading                     | 111  |

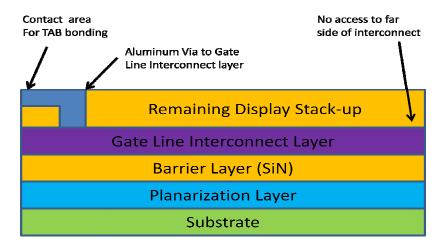

| Figure 4.5-1 Cross Section Showing no Access to Far Side of Interconnect Layer.          | 113  |

| Figure 4.5-2 Custom Mask Layer to Fabricate Test Structures.                             | 114  |

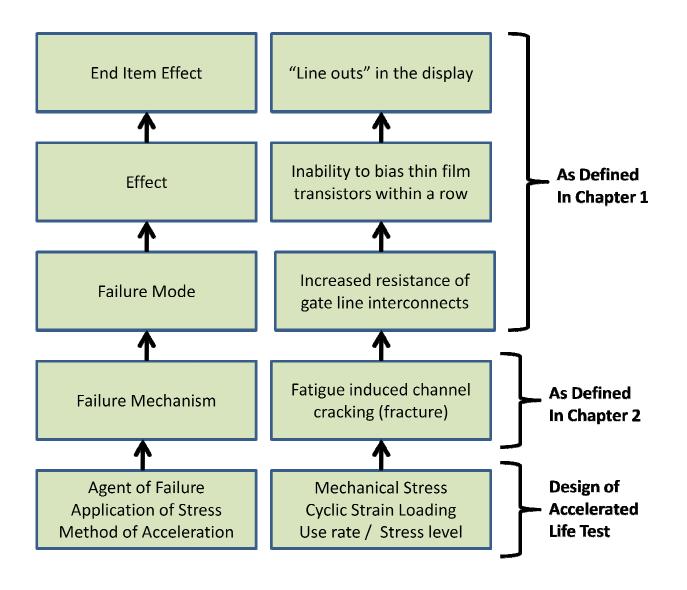

| Figure 4.6-1 Relationship of Accelerated Life Test to Effect of the Failure Mode         | 116  |

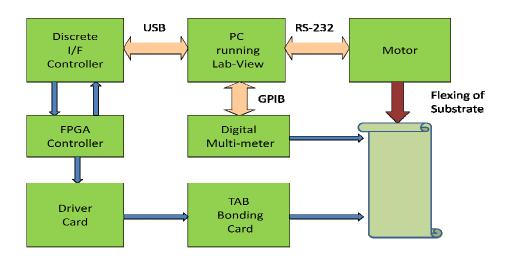

| Figure 5.1-1 Block diagram of dedicated test system                                      | 117  |

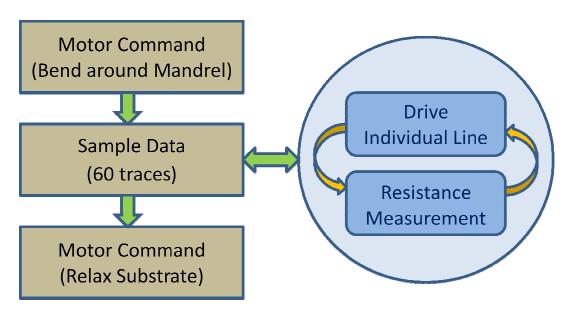

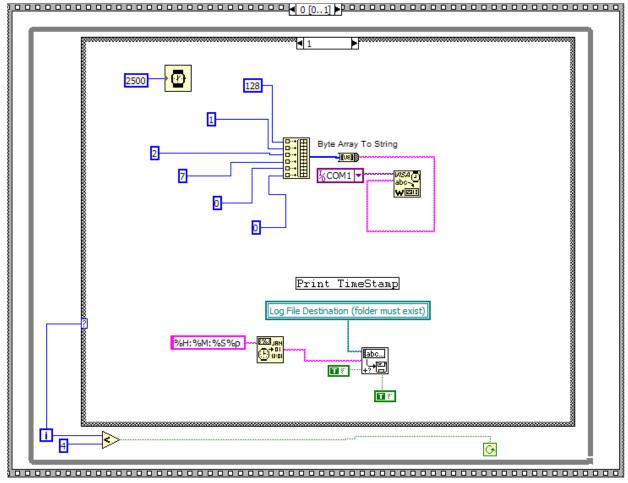

| Figure 5.2-1 Flow diagram of Labview program                                             | 119  |

| Figure 5.2.1-1 Labview Bend command and time stamp.                                      |      |

| Figure 5.2.2-1 Discrete Interface Controller                                             |      |

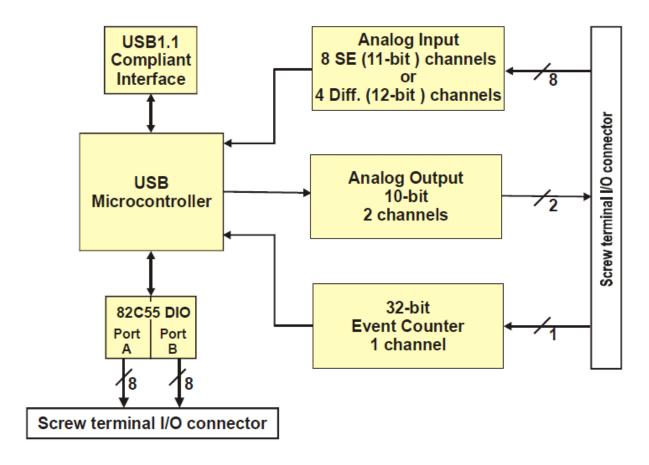

| Figure 5.2.2-2 Functional block diagram of Discrete Interface Controller                 | 122  |

| Figure 5.2.3-1 Block diagram of FPGA circuit card.                                       |      |

| Figure 5.2.3-2 Screen shot of Labview program waiting for sample command                 | 124  |

| Figure 5.2.3-3 Screen shot of Labview program obtaining resistance reading               |      |

| Figure 5.2.3-4 Timing diagram of the FPGA operation.                                     |      |

| Figure 5.2.4-1 Screen shot of Labview storing data to log file                           |      |

| Figure 5.2.4-2 Labview commanding servo to return to relaxed position                    | 126  |

| Figure 5.3-1 Schematic diagram of driver circuit for trace numbers 0 and 1               |      |

| Figure 5.3-2 Photograph of driver card in circuit                                        |      |

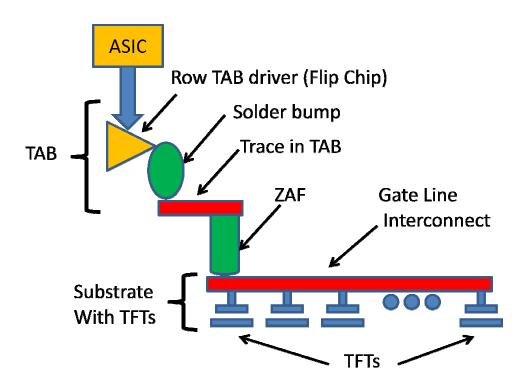

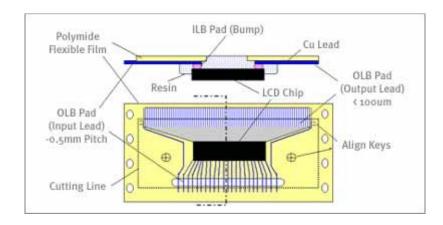

| Figure 5.4-1 TAB outline diagram and cross section                                       | 129  |

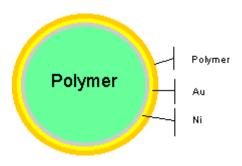

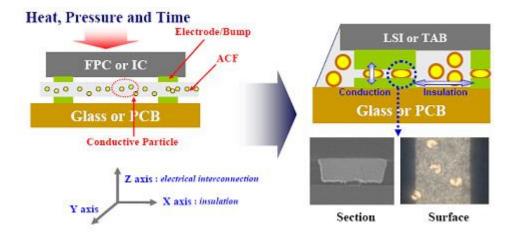

| Figure 5.4-2 Cross section of ACF polymer sphere                                         | 130  |

| Figure 5.4-3 ACF before and after bonding process                                        |      |

| Figure 5.4-4 Picture of TAB bonding card without substrate attached                      |      |

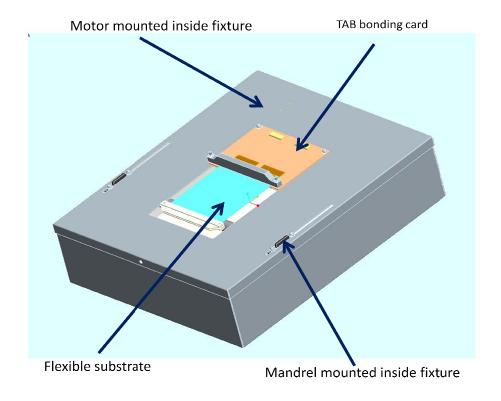

| Figure 5.5-1 Pro-E three dimensional model of mechanical fixture                         |      |

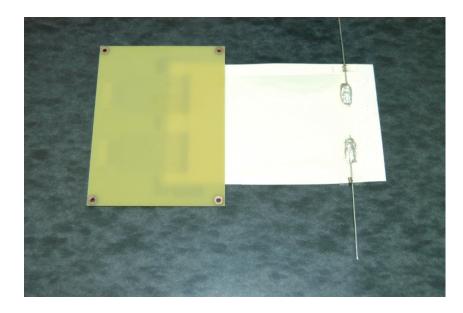

| Figure 5.5-2 Leads attached to the common bus bar on the flexible substrate              |      |

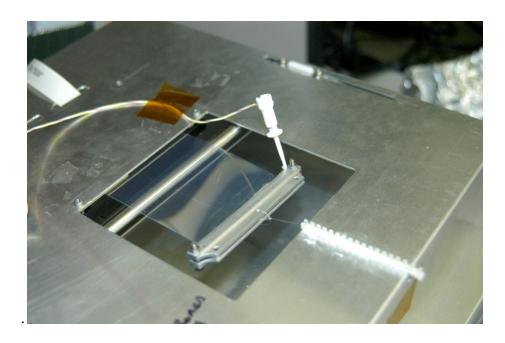

| Figure 5.5-3 Fixture with substrate mounted and mandrel installed                        |      |

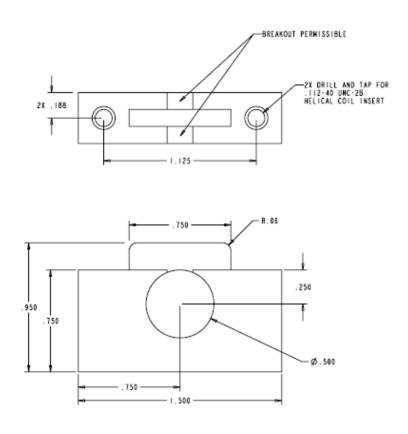

| Figure 5.5-4 Picture of mandrels and insert drawing                                      |      |

| Figure 5.5-5 Drawing for the Mandrel Inserts                                             | 136  |

| Figure 5.5-6 Stepper motor mounted inside the fixture                             | 137 |

|-----------------------------------------------------------------------------------|-----|

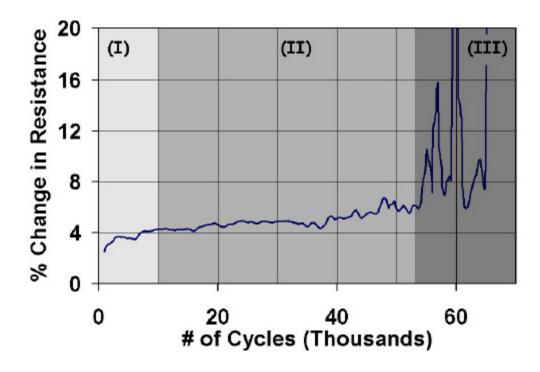

| Figure 6.3-1 Resistance versus cycles for 15um trace                              | 146 |

| Figure 6.4.1-1 Simulated Influence of Mandrel Radius on Cycles to Failure 1       | 147 |

| Figure 6.4.2-1 Simulated Influence of Trace Width on Resistance Change            | 148 |

| Figure 7.2.1-1 Development of compound life-stress model                          | 156 |

| Figure 7.3.1-1 Example S-N Diagram                                                | 160 |

| Figure 7.3.2-1 Example Strain-Life Curve                                          | 162 |

| Figure 7.3.3-1 Crack growth rate as a function of stress intensity factor         | 163 |

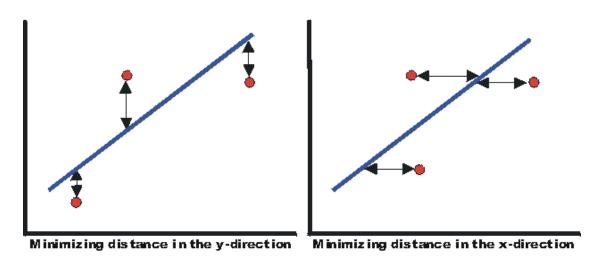

| Figure 7.4.1-1 Regression Analysis in both y-axis and x-axis                      | 166 |

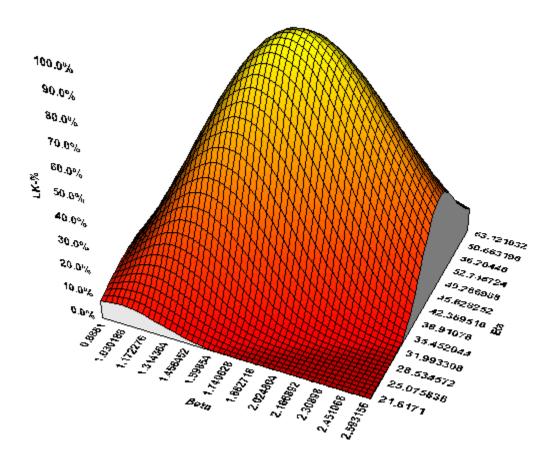

| Figure 7.4.2-1 Maximum likelihood function surface for a two parameter Weibull 1  | 169 |

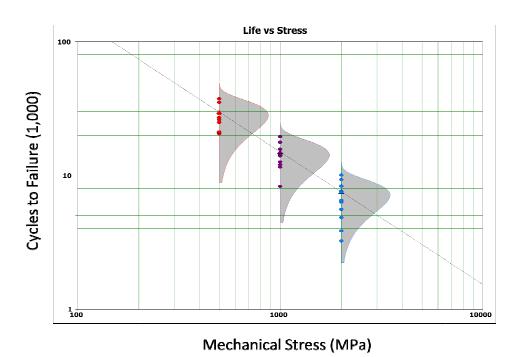

| Figure 7.5-1 Life-stress plot of 15um traces                                      | 172 |

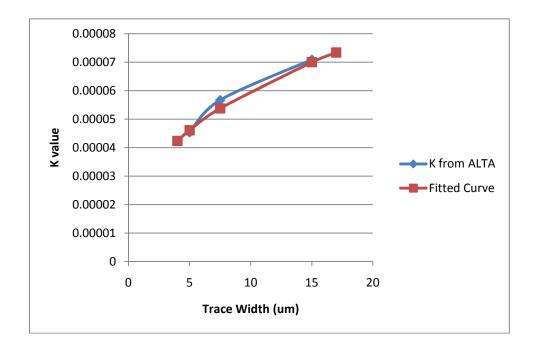

| Figure 7.5-2 Plot of K model parameter as a function of trace width               | 173 |

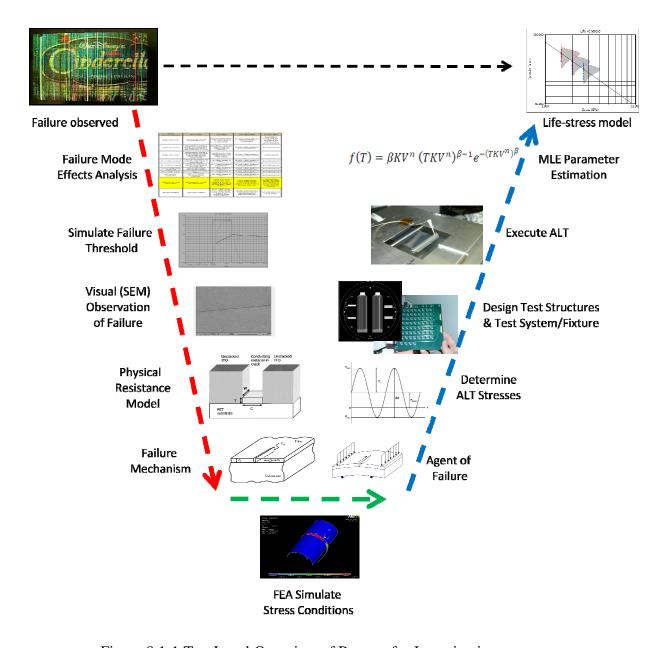

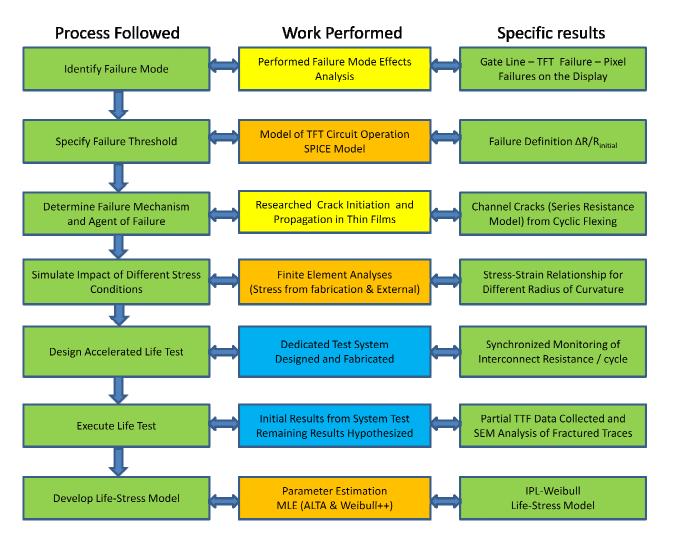

| Figure 8.1-1 Top Level Overview of Process for Investigation                      | 177 |

| Figure 8.1-2 Block diagram of process, work, and results                          | 178 |

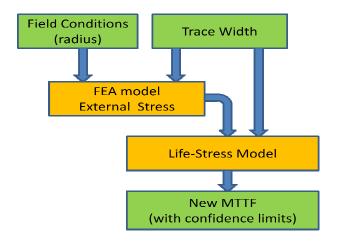

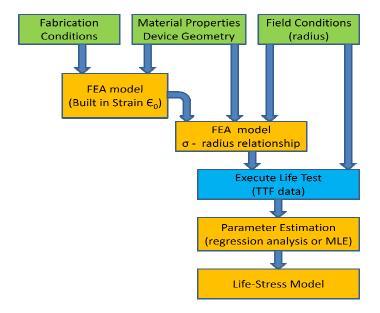

| Figure 8.2-1 Impact of field conditions and trace width on MTTF                   | 181 |

| Figure 8.2-2 Method for qualifying potential future interconnect designs          | 181 |

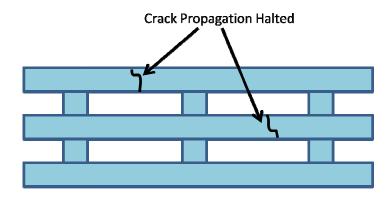

| Figure 8.3-1 Redundant parallel lines mitigates the impact of crack propagation 1 | 183 |

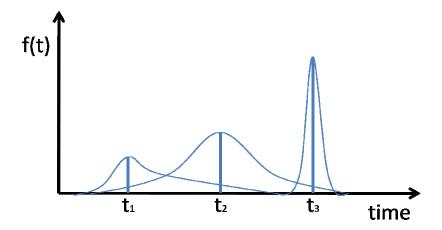

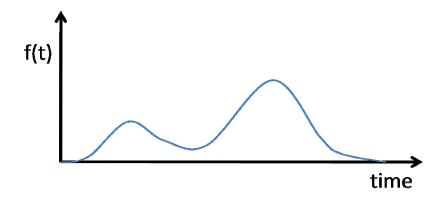

| Figure 8.3-2 Probability density functions of three competing failure modes 1     | 184 |

| Figure 8.3-3 Weibull plot of two competing failure modes                          | 185 |

| Figure 8.3-4 PDF of a system with competing failure modes                         | 186 |

## **Chapter 1: Introduction**

## 1. Overview

The evolution of display technology has seen significant strides over the past 100 years. Starting from the initial black and white cathode ray tubes the technology was relatively stagnant until the Active Matrix Liquid Crystal Displays (AMLCD) that started in the 1980s. Then next major paradigm shift in displays is in making them flexible so as to open up entire new avenues for applications that have yet to be considered. Along with this new shift in display technology comes with it significant hurdles with respect to reliability.

The follow sections start with a general background to displays and continue through the process of identifying the failure mode to be investigated and concluding with the contribution of this work. Sections 1.1 and 1.2 provide a history of display technologies from its humble black and white beginnings to the most recent technologies that are enabling the transition to flexible displays. A detailed theory of operation of the specific flexible display that is under study for this investigation is provided is section 1.3. Sections 1.4 and 1.5 discuss the field use conditions unique to flexible displays and the resulting failures as observed by the end users. An analysis of the failure modes that underlie these conditions is performed in section 1.6 as well as the identification of the one failure mode relevant to this investigation is given in section 1.7. A circuit model is used to simulate the performance of the display in order to determine the failure threshold (section 1.8). This chapter concludes with a

formal statement of the problem followed by the motivation and contribution of this thesis, sections 1.9 and 1.10 respectively.

## 1.1. History of Display Technologies

There have been numerous display technologies over the years; however the following sub-sections shall highlight the most prominent technologies to include the cathode ray tube and the liquid crystal display.

## 1.1.1. Cathode Ray Tube

The cathode ray tube is the oldest display technology. It was first proposed in 1908 and by January 1926 a mechanical version called a "televisor" was demonstrated [Campbell-Swinton 1908]. By the mid 1930s, manufacturers developed screens with 343 lines of data presented at 30 frames per second. The image is generated by controlling the luminance of a matrix of pixels (the smallest element in a display image). These pixels are arranged in a series of rows and columns on the surface of a screen as shown in Figure 1.1.1-1 from University of Colorado Physics 2000 website.

Figure 1.1.1-1 Breakdown of an image on a CRT display

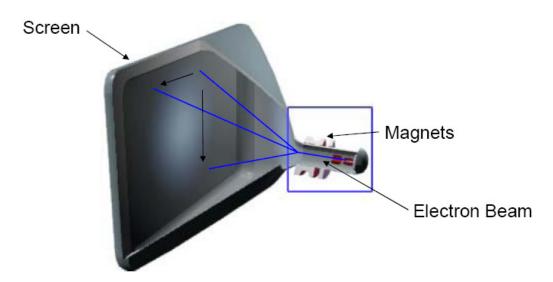

With the advent of color, each pixel is made up of three sub-pixels (red, green, and blue) the combination of intensity for each sub-pixel determines the overall color spectrum for that pixel. A CRT is made up of a vacuum tube with three electron guns (one for each color) at the rear or cathode end of the tube. A high voltage (anode) is placed at the display face of the CRT for accelerating the electrons from the three guns. The beam passes through a series of magnetics (yokes) which deflect the beam both horizontally and vertically onto the display surface as show in Figure 1.1.1-2.

Figure 1.1.1-2 Cross section of cathode ray tube

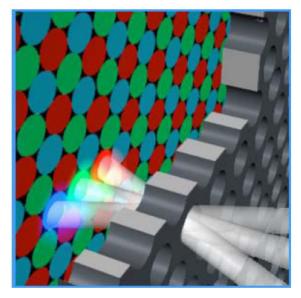

A shadow mask is used to align the beam from the red gun to only hit red sub-pixels, likewise for green and blue pixels as evident in *Figure 1.1.1-3*. When the beam strikes the sub-pixel the phosphor is illuminated in that particular color – the higher the current, the brighter it glows. The beam continues scanning the screen and by the time the phosphor intensity starts to fall off, the beam has already scanned the rest of the display and strikes the sub-pixel again. The observer of the display sees the image due to a property of our eyes called persistence of vision.

Figure 1.1.1-3 Shadow mask of cathode ray tube

The positive attributes of a CRT are high color saturation, wide viewing angle, low manufacturing cost, and reliability. The negative attributes include poor focus, amount of required mounting depth, and weight of the end item product. The liquid crystal display was the next major shift in display technology that targeted the mounting depth and weight problems of the CRT.

## 1.1.2. Liquid Crystal Displays

The term liquid crystal refers to a state of matter that has properties of both a liquid and a solid. In 1963, RCA discovered that light passing through a liquid crystal is affected by an electric field [Williams 1963]. By 1968, RCA made the first display device that leveraged this new technology [Heilmeyer 1968].

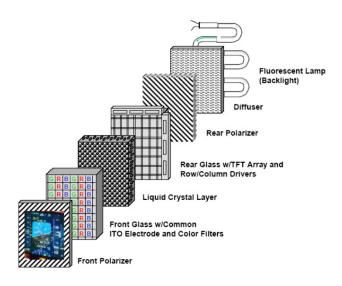

An LCD uses a similar premise for a color perception technology as the CRT in that the screen is made up of a matrix of sub-pixels (red, green, and blue). Instead of a cathode ray, each pixel is uniquely addressed by row and column drives that apply a voltage to the gate of a thin film transistor for that particular sub-pixel. These transistors are routed on one surface of glass, which contain the gate and drain. The source (or third terminal of the transistor) is on a separate layer of glass spaced in close proximity to the gate-drain layer. A front and rear polarizer are included in the optical stack to rotate the light 90 degrees along with a backlight to provide the luminance as shown in Figure 1.1.2-1.

Figure 1.1.2-1 Optical stack up of an Active Matrix Liquid Crystal Display

Liquid crystal material is sandwiched between the two layers of glass. Liquid crystals are compounds with long, rod like molecules and in an unbiased state, the molecules arrange themselves in a loosely ordered fashion with their long axes parallel. When a

drive voltage is applied to the gate of a transistor, an electric field is produced between the source and drain and this field. This field causes the molecules to rearrange themselves vertically (in parallel with the field) and light is allowed to pass straight through.

Positive attributes of the AMLCD are sharpness, lightweight, and thin profile. The negative attributes are a narrow viewing area, moderate video response (due to the response time of the liquid itself), higher manufacturing costs, and lower brightness.

### 1.2. Advanced Display Technologies Enabling Flexibility

Flat panel displays have been in commercial use for decades. The technology involves the fabrication of thin film transistors on a glass substrate. In recent years, there has been a tremendous push to manufacture displays on flexible substrates. The benefits of this approach include the ability to lend themselves to roll-to-roll fabrication as well as impart flexibility into the end item product.

Recently there have been advances in display technology that are not only improving the performance but also enabling the possibility of making displays flexible. The following subsections highlight the most prominent advances over the past two decades with respect to three major types of Electro-Optic Materials

- Emissive

- Reflective

- Transmissive

## **1.2.1.** Emissive Displays

Kodak first discovered organic materials that glowed in response to electrical currents in the late 1970's. Research continued through the 80's with the first efficient small-molecule OLED device being invented by Kodak in 1987 [Tang 1987 and Hack 2002]. The first color generated during this early research was green. By 1989, the Kodak research group demonstrated color improvements using fluorescent dyes, or dopants, to boost the efficiency and control of color output.

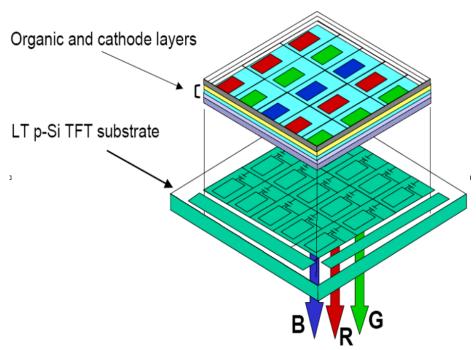

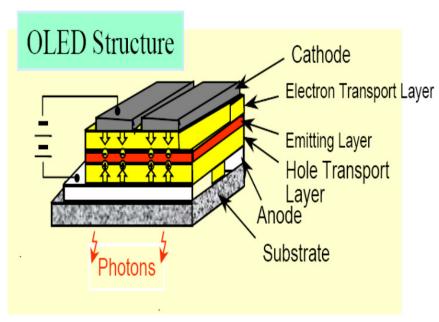

OLEDs are a fundamentally different technology from the CRT or AMLCD. An OLED is an electronic device similar in operation to a diode, but it is made by sandwiching a series of organic thin films between two conductors as reflected in Figure 1.2.1-1.

Figure 1.2.1-1 Cross section of Organic Light Emitting Device (OLED)

The operation of an OLED is much simpler than a cathode ray tube or an AMLCD. When a potential difference exists across the device, an electric current flows through the organic material and light is emitted. Figure 1.2.1-2 shows the operation of an OLED with current flowing from the cathode through the organic layers to the anode.

Figure 1.2.1-2 Operation of an Organic Light Emitting Device

OLED displays offer faster response time over LCDs (eliminates blurry images). This is due to an electric current driving the OLED versus a voltage driving the liquid crystal molecules (10µs verses 10ms). Wider viewing angle, higher contrast, higher brightness, better resolution, and lower power all make OLED displays very attractive to designers and consumers alike.

The reasons for the better performance lies in that OLEDs control the actual generation of light at the source level. An LCD's viewing angle is low due to the

optical characteristics of liquid crystal molecules varying depending upon the angle at which they are viewed. OLEDs emit at the source and spread the light uniformly in all directions to produce viewing angles similar to a CRT. LCD contrast limitations are based on the inability to control the passing of polarized light from 0% to 100%. OLED displays can achieve this based on precise control of the electric current passing through the pixel.

#### 1.2.2. Reflective Displays

Under the heading of reflective display technologies, there are several types that lend themselves to the advent of flexibility to include polymer dispersed liquid crystals, cholesteric liquid crystals, bichromic ball composites, and encapsulated electrophoretics. Since the technology employed for this study involves encapsulated electrophoretics, most of the discussion shall cover this topic.

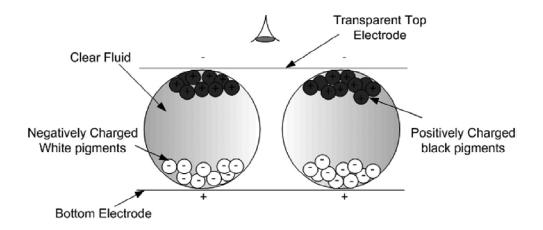

Electrophoresis is the translation of objects that are charged in a specific suspending dye fluid and their response to an electric field applied across that fluid. The objects are charged pigment particles contained in a thin film between electrodes. Optical contrast is obtained by moving the particles to either the top or bottom surface of the thin film as shown in Figure 1.2.2-1 [Dalisa 1977].

Figure 1.2.2-1 Cross section of Electrophoretic display

This technology lends itself to low power applications and sunlight readable since it uses ambient lighting to reflect back off the surface of the display. Figure 1.2.2-2 is an example of an electrophoretic display being used as electronic paper.

Figure 1.2.2-2 Electrophoretic display in an electronic paper application

#### 1.2.3. Transmissive Displays

Liquid crystals are the still the main choice for today's transmissive flat panel displays on glass substrates. Novel processes are being developed in order to paint liquid crystals onto flexible substrates. Detailed discussions on this topic are outside the scope of this research, but the main attributes of this approach involve photo enforced stratification [Quian 2000].

## 1.3. Theory of Operation

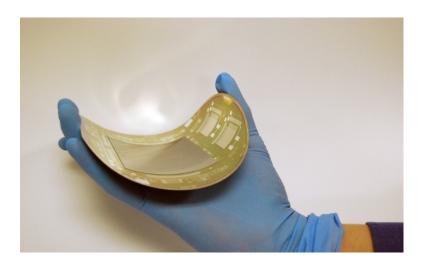

The following subsections provide a detailed discussion on the specific technologies employed for the flexible display used for this research. The topics include the basic fabrication steps, pixel design, the drive circuit, thin film transistor stack up, and the interconnects. Figure 1.3-1 is a picture taken of the end item product developed and manufactured at the Flexible Display Center (FDC) in Tempe, AZ a center sponsored by the Army Research Labs.

Figure 1.3-1 Picture of electrophoretic display manufactured by FDC

### **1.3.1.** Basic Fabrication Steps

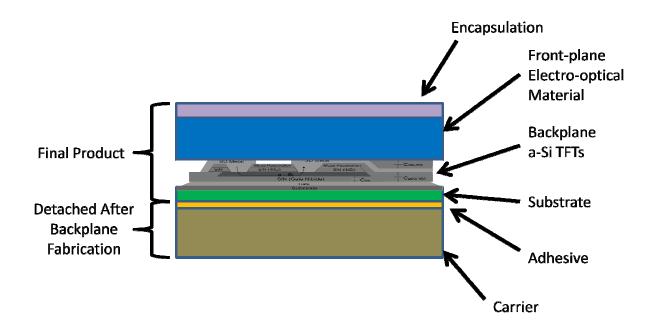

Figure 1.3.1-1shows the cross section of the display. Since the fabrication of a flexible display requires unique processing steps, the following paragrpahs provide a high level description of the fabrication sequences along with the terminology that shall be used throughout this document to ensure consistency since these terms are routinely interposed in industry.

Figure 1.3.1-1 Cross section of Standard Flexible Display

Fabrication starts with a carrier to ensure stiffness and prevent bowing during the processing steps so that the geometries are maintained throughout manufacturing. The FDC has experimented with different carrier made out of different materials such as

Silicon and Aluminum, but for this research Aluminum was used as the carrier material.

The substrate is bonded to the carrier using a proprietary adhesive. The FDC has also experimented with different substrate materials. Initially, stainless steel was used and since then plastic substrates have been introduced such as Polyethylene Terephthalate (PET) and Polyethylene Napphalate (PEN). The substrate material used for this research was PEN and more specifics of the material are provided in Chapter 2 of this thesis.

The backplane consists of the drive electronics that allow for the biasing of the electro-optical material (front-plane). On the backplane, an active matrix array of thin film transistors (TFT) are fabricated using amorphous Silicon (a-Si) as the main active material for the transistor. Specifics of the transistor composition are provided in section 1.3.4. The transistor controls the amount of voltage applied to an individual pixel element of the display and thereby controlling the response or how bright an individual pixel can be. Once the fabrication of the backplane electronics is complete, the need to maintain tight geometries is no longer pertinent and the substrate is debonded from the carrier.

The next step in the display fabrication is the application of the front-plane. Here the electro-optical (EO) material is deposited on the top surface of the backplane. Depending on the type of display (Emissive, Reflective, Transmissive) different electro-optical materials may be used. The most common materials used by the FDC are Electro-phoretic and organic semiconductor materials.

The cathode layer is applied to the top surface of the front plane in order to provide the ability to bias the EO material. In addition, the top surface of the display is encapsulated by a transparent material that prevents moisture ingress into the display since moisture has detrimental effects on the EO materials – especially if organic materials are used.

Figure 1.3.1-2 is a picture of the display fabricated on a stainless steel substrate instead of PEN that has been debonded from the carrier. The center of the wafer is the location of display with the electrophoretic material attached to the TFT backplane. Note that there are other test structures on the outlying areas of the wafer that will be cut out prior to final assembly of the display.

Figure 1.3.1-2 Photograph of display on stainless steel substrate

## 1.3.2. Electrical Operation of Display

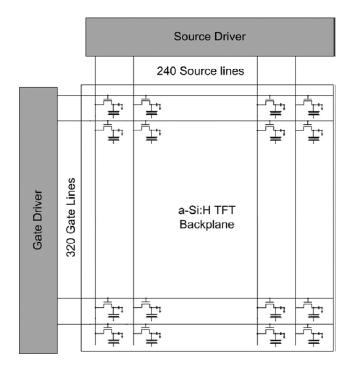

The display is made up of an array of 320 x 240 pixels. Each pixel in the display is addressed in the matrix by row and column signals that represent gate and source connections of the drive transistor in the TFT backplane for each pixel as shown in

Figure 1.3.2-1. The drivers implement shift registers that increments the addressing of each row one at a time. Within a row time the source (column) drivers translate the image data and apply the appropriate voltage to each TFT.

Figure 1.3.2-1 Schematic Diagram of gate/source (row/column) drive signals

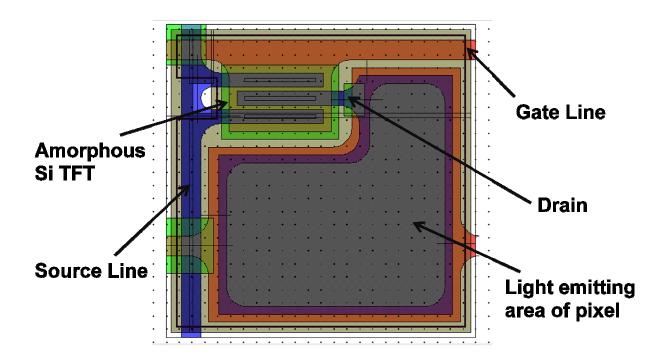

### 1.3.3. Pixel Layout

A pixel is composed of two main elements. The first element is the individual pixel drive circuit, for this specific display type it is composed of one amorphous silicon thin film transistor (a-Si TFT). The second element of a pixel is the area dedicated to biasing the electro-optical material. Figure 1.3.3-1 represents the physical device geometry of the pixel using standard semiconductor deposition techniques. This figure identifies the gate line interconnects that are of specific interest in this investigation. Spacing between grid points is  $10\mu m$ , therefore the pixel dimensions are  $240 \mu m \times 240 \mu m$ .

Figure 1.3.3-1 Diagram of one pixel

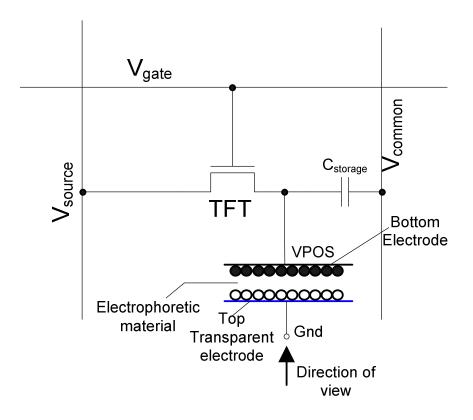

Operation of a pixel starts with a voltage applied to the gate of the thin film transistor which acts as a switch to transfer the image data (voltage) from the source line to the bottom electrode. The storage capacitor holds the voltage until the next frame of the image is loaded. This voltage is able to bias the electrophoretic material sandwiched between the bottom electrode and the top transparent electrode of the display as shown in Figure 1.3.3-2.

Figure 1.3.3-2 Schematic diagram of pixel

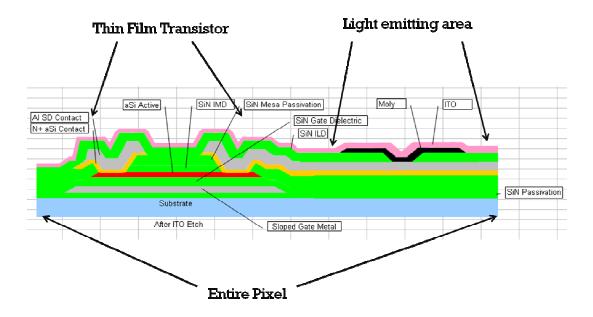

## 1.3.4. Thin Film Transistor

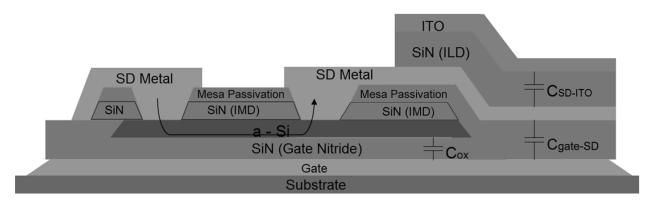

The amorphous Silicon thin film transistor is a bottom gate staggered structure. Figure 1.3.4-1 shows the cross section of the entire pixel with both the TFT on the left hand side and the light emitting area on the right hand side.

Figure 1.3.4-1 Cross section of entire pixel

A more detailed view of just the thin film transistor portion is provided in Figure 1.3.4-2. The fabrication process involves starting with a PEN substrate and patterning the gate metal. Three thin films are deposited (gate dielectric, a-Si:H, and back channel protection dielectric). The source and drain via openings are created by openings through the back channel protection dielectric to connect to the top metal. Next, the source/drain metal to include a low resistance n+ contact layer is deposited [Venugopal 2007].

Figure 1.3.4-2 Detailed cross section of thin film transistor

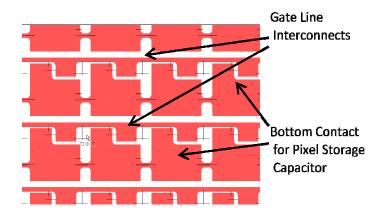

#### 1.3.5. Gate Line Interconnects

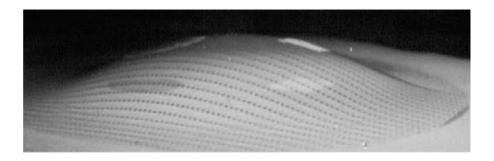

A DC magnetron sputtering system is used to deposit the gate material. Photo resist is spin coated on and then the gate layer mask is used for the exposure step. Figure 1.3.5-1 shows the resulting layer after etching. There are two circuit elements that comprise this layer. The first element is the gate (row) line interconnects that connect from the gate driver to each transistor. The second element becomes the bottom contact for the pixel storage capacitor. This also is the bottom electrode of the storage capacitor for each pixel.

Figure 1.3.5-1 Gate layer after etching process

#### 1.3.6. Transistor Operation

In order to better understand the failure modes of a display, it is essential to understand the operational characteristics of the thin film transistors. Operational characteristics of TFTs fabricated on glass are well understood and documented. On the other hand, electrical performance of TFTs fabricated on flexible substrates are less than ideal vary considerably due to the special processing considerations required due to the introduction of different substrate materials.

For rigid AMLCD displays the thin film transistors are deposited on glass and therefore can be fabricated at conventional process temperatures of (250-350C). This temperature range is the optimum for creating high quality hydrogenated amorphous silicon (a-Si:H). Unlike glass, plastics have a low heat resistance and therefore the deposition temperatures are usually at or below 150C. This lower deposition temperature results in inferior performance characteristics for the amorphous silicon [Sazonov 2000].

This lower temperature results in more dangling bonds of Silicon in the deposited film. Both Hydrogen and/or Helium dilutions are used in during the low temperature deposition process to attach to the dangling bonds and improve the electrical performance of the active region of the TFT [Parsons 2000]. For this investigation, the Flexible Display Center deposits the amorphous Silicon with a Hydrogen dilution at 150C.

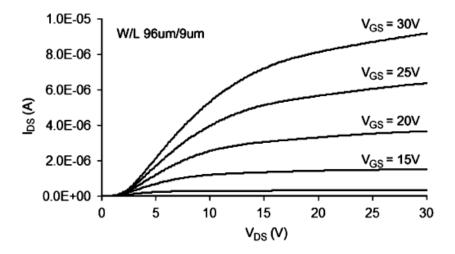

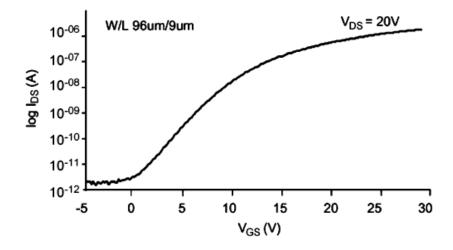

Transistor operation is usually characterized by a plot of drain to source ( $I_{ds}$ ) current as a function of the voltage applied at the gate of the transistor ( $V_{gs}$ ). Several factors influence this function as defined in Equation 1.3.6-1. These factors include the mobility as denoted by  $\mu$ , the capacitance as denoted by  $C_i$ , the dimensions of the active region – width and length (w and l), and the voltage threshold denoted by  $V_{th}$ .

$$I_{DS} = \mu C_i \frac{w}{2l} (V_{GS} - V_{th})^2$$

(1.3.6-1)

The FDC conducted tests on the fabricated transistors and determined the mobility is in the range of  $0.1-0.2~\text{cm}^2/~V\cdot s$  with an off state leakage current of approximately 10pA providing an on/off ratio of  $10^6$ . Figure 1.3.6-1 and Figure 1.3.6-2 show the  $I_{DS}$  characteristics of the fabricated transistors.

Figure 1.3.6-1  $I_{DS}$  versus  $V_{DS}$  characteristics of TFT

Figure 1.3.6-2  $I_{DS}$  versus  $V_{GS}$  characteristics of TFT

Another unfavorable characteristic of amorphous thin film transistors fabricated at low temperatures on flexible substrates is the shift in threshold voltage through the life of the device. There are two main factors contributing to this shift in threshold voltage. The first is charge injection in the gate insulator which is the Silicon Nitride deposited on top of the substrate. The second is the creation of charged defect states (commonly called dangling bonds) in the amorphous silicon conducting channel. Over time this shift shall impact the performance of the overall display, but the above two factors are beyond the scope of this research.

## 1.4. Field Conditions for Flexible Displays

With the advent of making displays flexible, a whole new set of aspects are required when considering field use conditions. In addition, depending on the processes involved, handling to during initial fabrication may need to be considered as well. In some field use instances, the displays are shaped one time during system level assembly/integration to a conformed shape with a set radius of curvature that does not change. Figure 1.4-1 is an example of a wrist display assembly, whereby the display has been conformed one time to a set shape.

Figure 1.4-1 Pictures of wrist display conformed one time to a set radius

More stressful conditions involve displays that are routinely flexed, rolled, or even folded throughout their lifetime in the field as shown in Figure 1.4-2. The mechanical stresses endured throughout field use pose significant challenges with respect to reliability and device lifetime [Chwang 2003].

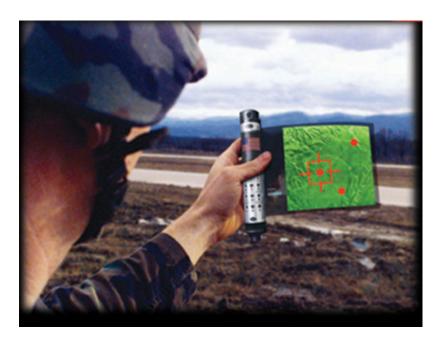

Figure 1.4-2 Example of field use conditions for flexible displays

# 1.5. Reliability Problem as Observed by the End User

Flexible displays provide a whole new set of reliability problems that were never present before with rigid displays. The basis of these problems stems from the fact that the display itself shall be subjected to bending both during initial fabrication as well as field use. Since there is limited reliability data from actual field use, not all of the reliability problems are known at this time. However, one known reliability problem at this time is that of "line outs". This is a term that is used throughout industry to describe the condition of a display that contains either vertical or horizontal lines that can be observed visually by an operator. Depending on the display technology and the image being presented at the time of failure, these lines can be: white, black, red, blue, or green. The red, blue, and green would only be observed in color display since these are the basic primary colors used to make color images. Figure 1.5-1 is a picture of a flexible display with multiple line outs in both the horizontal and vertical directions.

Figure 1.5-1 Example of failure condition "line outs"

# 1.6. Failure Mode and Effects Analysis

In general, a complete Failure Mode and Effects Analysis (FMEA) for an entire display is a lengthy and involved task. Since the scope of this investigation revolves around line outs as observed by the end user, then only those failure modes that propagate and manifest themselves as such shall be considered in this analysis.

There are two main approaches to performing a FMEA. The first approach involves a top down perspective whereby the analyst starts with a block diagram of the system being investigated and correlates failure effects as observed at the system level with failure modes in the system block diagram. An iterative process takes place that involves linking the failure effects and associated high level failure modes to lower level failure modes of the design topology. This process continues until the analyst reaches the required level of identification of failure modes.

The second approach involves a bottom up approach whereby the analyst starts with identifying all the elements/components involved in the display. Once all the elements are identified, then failure modes for each element are characterized and their local impact/effects of the failure condition are determined. This process continues with postulating how the failure effects propagate to the next higher level of system integration. The analysis ends when the investigation determines how a particular low level failure mode manifests itself at the highest level of system integration and can be observed by the end user.

The FMEA performed for this investigation entailed both a top down as well as a bottom up approach for the specific end item observation of horizontal line outs in the display. The results of both were cross correlated and differences were resolved to result in one consolidated FMEA. Figure 1.6-1 is a diagram of the elements/components involved in the display system that contribute to the end item effect of horizontal line outs. Table 1.6-1 is an abridged version of the FMEA that identifies failure modes that contribute to horizontal line outs. The highlighted row in the FMEA table is the specific failure mode being that shall be discussed in greater detail in section 1.7 herein.

Figure 1.6-1 Diagram of FMEA Elements

Table 1.6-1 Failure modes that result in horizontal line-outs

| Display<br>Component/Element         | Failure Mode                                                                                                       | Local Effect                                                                                                            | Next Higher Effect                                                                                                   | End Item Effect                                                                                                            |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Display Driver ASIC                  | Internal Failure causing gross timing errors                                                                       | Incorrect signals fed to<br>shift registers for both<br>Row and Column<br>synchronizing                                 | Row and Column data are incorrect and not-synchronized                                                               | Depending on severity of failure - could result in intermittent line outs to entire picture unreadable                     |

| Display Driver ASIC                  | Internal failure causing a<br>specific Row command to<br>not get fed into the Row<br>shift register Driver circuit | Specific Row signal not<br>being driven - no<br>voltage applied to<br>entire Row                                        | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Display Driver ASIC                  | Internal failure causing a specific Column command to not get fed into the Column shift register Driver circuit    | Specific Column signal<br>not being driven - no<br>voltage applied to<br>entire Column                                  | No Gate voltage applied to<br>TFTs on an entire Column                                                               | Vertical Line out                                                                                                          |

| Row TAB Driver Circuit               | Open Circuit condition on<br>a specific output signal of<br>driver flip chip                                       | No voltage applied to Row                                                                                               | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Row TAB Driver Circuit               | Degraded Voltage on a specific output signal of driver flip chip                                                   | Low voltage applied to a specific row                                                                                   | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Row TAB Solder Bump<br>to Flip Chip  | Cracked solder bump - open circuit condition                                                                       | No voltage applied to Row                                                                                               | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Row TAB Flex Traces                  | Open condition in TAB<br>Flex traces                                                                               | No voltage applied to Row                                                                                               | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Row TAB ZAF<br>Connection            | Open ZAF condition<br>between TAB and<br>Substrate                                                                 | No voltage applied to Row                                                                                               | No Gate voltage applied to TFTs on an entire row                                                                     | Horizontal Line out                                                                                                        |

| Substrate -Row Line<br>Interconnects | High impedance of Gate line Interconnects                                                                          | Voltage drop across interconnect lines resulting in too low of voltage with respect to the Threshold Voltage of the TFT | Drive voltage on the Source of the TFT that represents the display image is not transferred to the Drain of the TFT. | Horizontal line through the display starting where the gate voltage is too low and continuing to the end of the substrate. |

| Internal TFT failure                 | Open Gate-condition                                                                                                | Drive voltage on the Source of the TFT that represents the display image is not transferred to the Drain of the TFT.    | Inability of the transistor<br>to adequately bias the<br>electroluminescent<br>material of the pixel                 | Individual pixels out on the display                                                                                       |

# 1.7. Identification of Specific Failure Mode

As identified in Table 1.6-1, there are ten unique failure modes that could contribute to an end item effect of a horizontal line out as observed by the end user. Note that failure modes specific to the thin film transistors were not part of the 10 identified in Table 1.6-1. The reason for this is that both the bottom up approach and the top down approach did not yield any TFT failure modes that resulted in line outs. Catastrophic TFT failure modes resulted in individual pixel failures and gradual parameter drift failures that would affect all the TFTs in the display (such as voltage threshold drift) resulted in overall effects in the display performance and not an individual line out.

An investigation into all of these failure modes and specific failure mechanisms would be too broad of an investigation. Hence, it was decided that this investigation would focus on one particular failure mode that has been highlighted in the FMEA table.

This failure mode is high impedance of the gate line interconnects. The local effect of this condition is that the voltage as seen at the gate of a transistor is not high enough with respect to the TFT's threshold voltage. Another perspective of this condition as seen from the gate driver would be that the voltage threshold of the TFT would appear to be increasing. Hence, in keeping the gate voltage constant, the increased impedance of the gate line interconnect could be viewed as an increase in threshold voltage even though the internal threshold voltage of the TFT has not shifted.

The next higher effect of this failure mode is that the TFT does not adequately turn on and therefore the drive voltage coming from the column driver TAB (connected to the source of the TFT) does not get transferred to the drain side of the TFT. Hence, the end item effect is that the display image data initiating from the column TAB drivers does not bias the individual pixels in a particular row of the display. The end visual result as observed by the user is a "line out".

### 1.8. Criteria for Failure

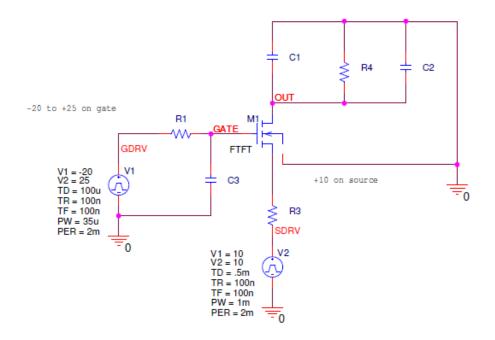

Now that a specific failure mode has been identified per section 1.7, the criteria for failure needs to be ascertained. An electrical circuit model was employed to simulate the behavioral characteristics of the TFT with increasing gate line impedance, the model program used is called Simulated Program with Integrated Circuit Emphasis (SPICE). Figure 1.8-1 is a schematic diagram of the TFT along with the pixel load as well as the gate voltage drive and the source voltage drive. Due to the proprietary nature of the design, circuit element values have been removed from the figure.

Figure 1.8-1 Schematic Diagram of SPICE Model

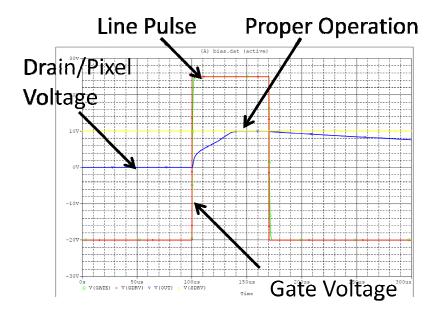

V1 is the gate driver voltage for an entire line and V2 is the source driver voltage for a column of pixels. R1 is the gate line resistance and C3 is the capacitance on the gate line. R3 is the source line resistance and M1 represents the TFT. On the Drain side of the TFT – C1 is the holdup capacitance and R4 in parallel with C2 represent the electrical equivalent circuit for the pixel. The circuit was simulated with the resistance value of R1 starting at its nominal value of 300k. The requirement is that the TFT turns on and transfers the 10V source drive to the drain in order to adequately drive the pixel within the 70uS line rate. Figure 1.8-2 shows proper operation of the circuit whereby at time equals 100uS the line pulse starts as defined by the red line. During this pulse, the blue drain/pixel voltage starts to ramp up from 0 volts to the 10V value as supplied from the yellow source line within the required line rate timeframe as shown by the red line at 170uS.

Figure 1.8-2 SPICE Model Output Showing Correct Operation

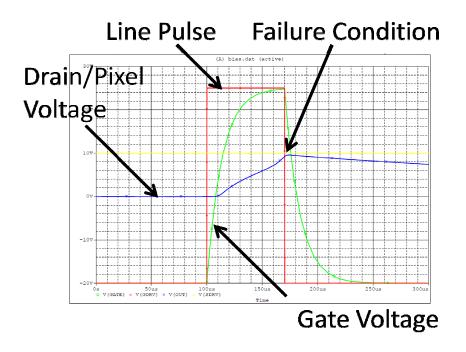

Figure 1.8-3 is the output of the SPICE when the gate line resistance is increased higher and higher beyond its nominal value. The failure condition is identified in the figure by the arrow pointing to the blue Drain/Pixel voltage line. In this figure the voltage does completely reach the source voltage of 10V within the line pulse window of 70uS. The value resistance value of the gate line where this threshold is reached is 450k Ohms.

Figure 1.8-3 SPICE Model Output Showing Failure Condition

## 1.9. Statement of Problem

Given the myriad of reliability hurdles facing the adequate implementation of flexible displays in rugged field use environments, this investigation shall delve into understanding the particular failure condition observed by end users as "line outs".

Based on the FMEA of section 1.6 several failure modes can manifest themselves as line outs, but only the failure mode of high impedance of the gate interconnect lines as identified in section 1.3.5 shall be of concern to this investigation. This impedance was modeled in SPICE as R1 in Figure 1.8-1 and simulation has determined that the threshold of failure is when this resistance exceeds 450k Ohms.

The problem being addressed by this thesis is: What is an appropriate process for rapidly determining the life-stress relationship of gate line interconnects and using this relationship in the qualification of current and future flexible display designs? In order to address this problem, there are several questions that this investigation will address:

- Given complex geometries, what is the best method to model the stresses?

- Should the model consider built in stresses from fabrication?

- How should a test be designed to obtained failure data in a timely manner?

- How does one select an appropriate model for flexible display failure modes?

- Once the model is determined, how does this aid in qualifying a new design?

#### 1.10. Motivation and Contribution of this Thesis

Making displays flexible have created brand new failure modes as a result of unique failure mechanisms never before encountered with traditional style displays. Due to continuous advancements in flexible display technologies, from novel materials to unique fabrication techniques, it is apparent that a need exists for a method to rapidly test and assess their impact on reliability from a myriad of inter-related conditions. Therefore, the scope of this research has three main contributions.

The first element of this research is the design and fabrication of a dedicated test system to successfully capture dynamic changes in electrical performance of novel flexible test structures under accelerated fatigue stress conditions.

The second contribution of this research is the development and analysis of a finite element model of a specific test structure that is representative of an actual design in use for a current flexible display product.

The third and final contribution of this research is a framework for a methodology of testing and qualifying future multilayer interconnect designs on flexible substrates. This is achieved by a combination of the test system, finite element analysis of the test structure to characterize the failure mechanism, accelerated life testing, and Mean Time to Failure (MTTF) life-stress models.

# Chapter 2: Analysis of Failure Mechanism

## 2. Overview

As defined in chapter 1, the failure mode of this investigation is increased resistance of gate line interconnects that result in the inability to drive thin film transistors required to bias pixels. The end item effect is manifested as "line-outs" visually observed in the display system. Now that the failure mode is succinctly defined, the next step is to understand the failure mechanism that is the root cause for inducing the failure mode observed at the system level. Examples of failure mechanisms vary from material interaction (Ohmic contact degradation), to electrical stress induced (electromigration, electro-static discharge), or to mechanically induced (die fracture from mismatch of thermal expansion coefficients).

This chapter shall identify and characterize the failure mechanism that causes the increased gate line resistance (failure mode). The following subsections provide a walkthrough of the process required to understand the failure mechanism. Section 2.1 is an in-depth analysis of the failure mode complete with micrographs from a Scanning Electron Microscope (SEM) as well as a proposed series resistance model used to characterize the failure mode. Section 2.2 covers fracture of thin films on compliant substrates. The difference between films in compression and tension as well as quantifying a fatigue induced failure shall be covered. Section 2.3 provides a background of the thermo-elastic properties of the materials used for the substrate, insulating layers, and gate line interconnect traces. Section 2.4 calculates the internal

stresses as a result of the fabrication process at elevated temperatures using materials with different coefficients of thermal expansion. Sub-section 2.4.2 is dedicated to a finite element analysis using a program called Coventor that specializes in modeling stresses from fabrication. Section 2.5 provides the background for understanding externally induced stress as a result of bending forces employed during field use conditions. Sub-section 2.5.2 contains the results of ANSYS finite element analyses used to predict stresses under specific field conditions.

### 2.1. Characterization of the Failure Mode

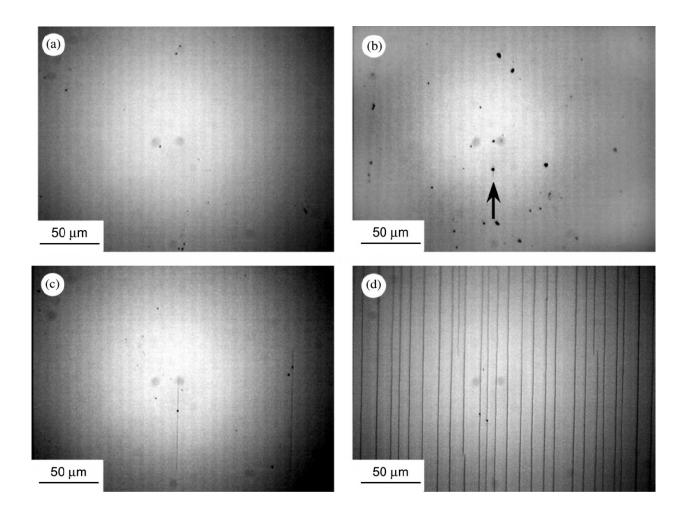

Since the resistance of the gate line interconnect is increasing throughout the life of device in the field, one needs to understand at a microscopic level what is actually happening to create the phenomena. There can be several factors that can influence the resistance of the interconnects such as cracks in the thin film as well as corrosion of the material itself. Corrosion is a concern due to the use of flexible displays in harsh environments. Contamination as a result of the introduction of impurities from raw materials used in the fabrication, the production environment itself, and material handling plays a major role in this process. Once contamination is introduced to the system, the combination of humidity, temperature, and a voltage potential become mechanisms to facilitate the corrosion phenomenon. Research on the influence of scratches of the ITO during fabrication found that the presence of Cl reacts with the moisture to form HCl that then reacts with the Indium Oxide (In<sub>2</sub>O<sub>3</sub>) causing the breaking of bonds of H-Cl and In-O and resulting in In-Cl and O-H bonds. This outcome of this chemical process is the eventual discoloration and structural damage of the ITO film [Leung 2008]. For this investigation, failure analysis techniques were

employed to capture images of the failure condition as well the proposition of a physical resistance model that relates the increasing resistance to mechanical cracks forming in the ITO film.

#### 2.1.1. Cracks in Gate Line Interconnect Thin Film

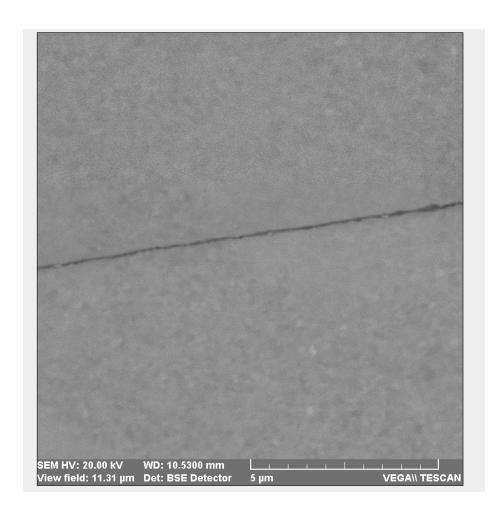

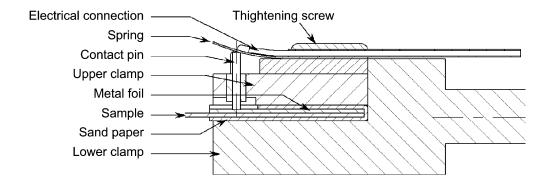

During a root cause investigation, there are several failure analysis tools that can be employed to get a better understanding of the physics behind the failure at the microscopic level. Here a scanning electron microscope (SEM) was used to capture images of the gate line interconnect traces at high magnification. Figure 2.1.1-1 is an image capture from a Vega SEM manufactured by TESCAN at the Materials Analysis Group lab in Norcross, GA. The image was generated using a back scattered electron (BSE) detector with a SEM voltage of 20kV. Using the SEM, it was evident that micro-cracks are being formed in an ITO trace for a gate line interconnect.

Figure 2.1.1-1 SEM Micrograph of Cracks in ITO Thin Film

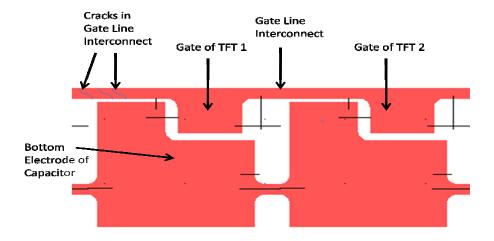

In order to provide perspective of the SEM image in Figure 2.1.1-1 a diagram of the gate line interconnect from chapter 1 has been duplicated herein to show were in the system this crack exists. Figure 2.1.1-2 is taken from the gate mask used during fabrication of the flexible display. The top portion of the diagram is the actual gate line trace used to connect the drive voltage to the gates of two thin film transistors (TFT 1 and TFT 2). Example cracks have been drawn in on the left side of the trace. The bottom portion of the diagram is also part of the same mask, but this is the bottom electrode of a capacitor underneath the pixel area. The capacitor is electrically

isolated from the gate, but shown here since it is part of the same mask used in the photolithography process.

Figure 2.1.1-2 Cracks in Film of Gate Line Interconnects

It is common sense that a crack would increase the resistance of a trace, but a physical model is required in order to characterize the relationship between a crack and the trace resistance as well as the quantity of cracks to the trace resistance.

#### 2.1.2. Series Resistance Model

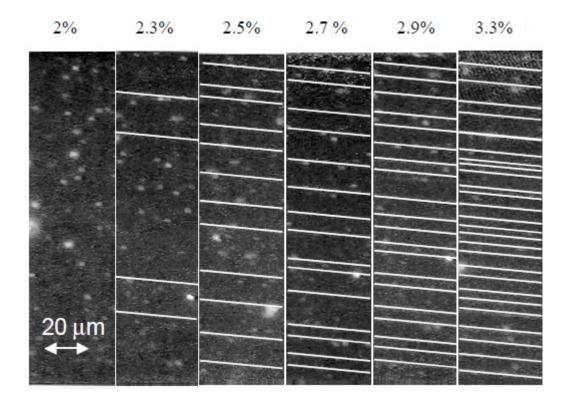

Based on experimental observations of increasing resistance with increasing strain a physical model was developed to corroborate the evidence [Cairns 2000-A]. The main observations of ITO on PET were as follows:

- cracks traverse the entire width of the ITO structure

- ITO resistance increases rapidly when a threshold strain is reached

- resistance increase is synonymous with the initiation of cracks

- density of cracks per unit length of ITO increases rapidly and then saturates

The proposed model states that at some threshold strain the first crack in the ITO layer is formed. The crack is bridged by some minute amount of ITO material and its volume is assumed to be constant, the constant volume allows for a nonlinear increase in resistance of a crack as the width increases. Each crack is also independent of every other crack and therefore the resistance of the sample increases based on the series sum of resistances of each of the cracks, reference Figure 2.1.2-1.

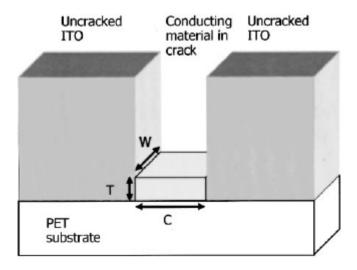

Figure 2.1.2-1 Diagram Showing Bridging Material Inside a Crack

If one treats the cracks as a set of resistors connected in series, then one can ignore the negligible change in resistance of the ITO versus that across the cracks as a function of strain. For each crack, the i<sup>th</sup> resistance is calculated as:

$$R_i = \frac{\rho c_i}{A} = \frac{\rho c_i^2}{V} \tag{2.1.2-1}$$

Here  $\rho$  is the resistance property of the ITO material and Ci is the extent of the

opening of the crack as shown in Figure 2.1.2-1. V is the fixed volume of the ITO material on the substrate surface inside the crack which is the calculated based on the thickness (T), width (W), and the crack opening (C). A is the cross sectional area of the volume based on thickness and width. The length of the bridging layer (C) is assumed to be zero at the instant the crack forms and then with increasing strain, C becomes larger. The length of the bridge as a function of strain is computed as:

$$C_i = D(\varepsilon - \varepsilon_{ci}) \tag{2.1.2-2}$$

Here,  $\varepsilon$  is the instantaneous strain,  $\varepsilon_{ci}$  is the strain at which the ith crack forms, and D is a length scale. Based on the assumption that the volume of ITO in the bridge zone is conserved then the resistance is defined as:

$$R_i = \frac{\rho D^2 (\varepsilon - \varepsilon_{ci})^2}{V} \tag{2.1.2-3}$$

Using n as the total number of cracks at strain  $\varepsilon$ , then the total resistance of all the cracks in the ITO layer is computed as:

$$R_{total} = \sum_{i=1}^{n} \frac{\rho D^{2} (\varepsilon - \varepsilon_{ci})^{2}}{V}$$

(2.1.2-4)

Note that this is the calculated resistance of the cracks and this resistance needs to be added to the original resistance of the ITO material prior to any strain being imposed

to obtain the total resistance of the specimen under test. Given the SPICE model from section 1.8 determined the failure threshold was a trace resistance of 450k Ohms and the average initial trace resistance is approximately 200k Ohms, then the critical resistance to induce failure as a result of cracks is calculated to be approximately 250k Ohms.

This section provides a physical series resistance model that explains the correlation between crack size, number of cracks, and the increase in resistance of the gate line traces with increasing applied strain.

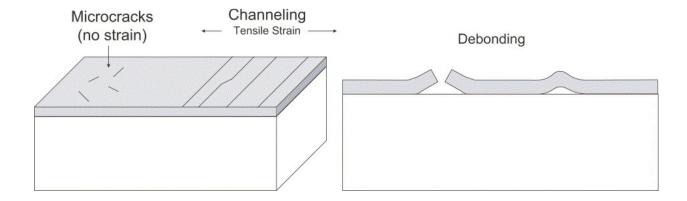

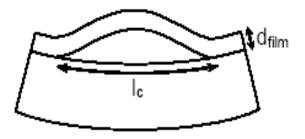

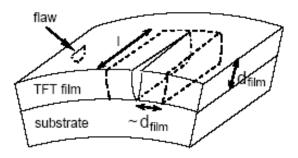

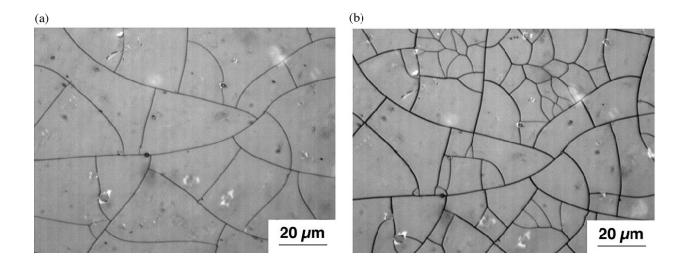

#### 2.2. Fracture of Thin Films

Common failure modes of thin film layered devices involve the growth of micro cracks under stress. The specifics of the fracture mode depend on the substrate modulus, film adhesion, and film cohesion. The two most common types of failures for brittle films on flexible substrates are:

- Film cracking / channeling

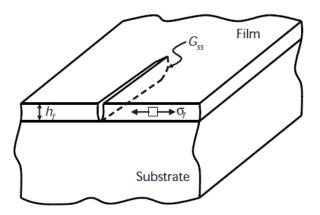

- De-bonding