**ABSTRACT**

Title of Document: FABRICATION AND PROCESS

DEVELOPMENT FOR AN INTEGRATED

OPTICAL MEMS MICROSYSTEM IN

**INDIUM PHOSPHIDE**

Nathan Paul Siwak, Doctor of Philosophy,

2013

Directed By: Professor Reza Ghodssi, Department of

Electrical and Computer Engineering, Institute

for Systems Research

This dissertation presents the design, fabrication, and evaluation of the first monolithically integrated MEMS resonant sensor system realized in the InP-InGaAs material family. The integration of a MEMS sensor along with the facilitating optical interrogation platform provides for increased manufacturing scalability, sensitivity, and reduced measurement noise and device cost. The MEMS device presented in this dissertation consists of an Indium Phosphide (InP) cantilever waveguide resonator whose displacement is measured optically via a vertically integrated laser diode and

waveguide photodetector. All three major components of the sensor were integrated in a single 7.1 µm thick molecular beam epitaxy (MBE) epitaxial growth, lattice matched to an InP substrate. Full fabrication of the integrated MEMS device utilizes 7 projection lithography masks, 4 nested inductively coupled plasma (ICP) etches, and over 60 discrete processing steps. This dissertation focuses on the integration design and the development of specific III-V semiconductor fabrication processes in order to completely fabricate and realize these devices, including specialized ICP etching steps and a MEMS undercutting release etch. The fabricated devices were tested and characterized by investigating the separate component subsystems as well as the total combined system performance. Investigation of device failure and performance degradation is performed and related to non-idealities in the device fabrication and design. A discussion of future work to improve the performance of the system is presented. The work in this dissertation describing the successful fabrication process and analysis of such a complex system is a milestone for III-V based optical MEMS research and will serve as the groundwork for future research in the area of optical MEMS microsystems.

# FABRICATION AND PROCESS DEVELOPMENT FOR AN INTEGRATED OPTICAL MEMS MICROSYSTEM IN INDIUM PHOSPHIDE

By

Nathan Paul Siwak

Dissertation submitted to the Faculty of the Graduate School of the

University of Maryland, College Park, in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

2013

**Advisory Committee:**

Dr. Reza Ghodssi, Chair

Dr. Christopher Richardson

Dr. Christopher Davis

Dr. Neil Goldsman

Dr. Miao Yu, Dean's representative

© Copyright by

Nathan Paul Siwak

2013

## Dedication

To my amazing friends and family for never growing tired of my ever receding "deadlines," my wonderful wife Julie, who is not listed as an author in this work but should be, and last but not least the One who makes all of these things possible.

### Acknowledgements

The author would like to thank Professor Reza Ghodssi for his guidance and support throughout this degree process, and the members of the advisory committee for their helpful suggestions and discussions.

The members of the MEMS Sensors and Actuators Laboratory for their indispensable discussions, suggestions, support, and camaraderie, particularly Mike Fan and Konstantinos Gerasopoulos for all of their advice, personal and professional.

To the researchers in the Molecular Beam Epitaxy (MBE) laboratory at the Laboratory for Physical Sciences (LPS), specifically Dr. Christopher Richardson and Laura Clinger for growing and providing the final working MBE samples for these devices, as well as their significant technical advice and thoughtful comments covering all aspects of this work from inception to completion. Dr. Paveen Apiratikul contributed very helpful discussions and resources on data acquisition and theoretical analysis, and along with Dr. Gyorgy Porkolab, many discussions related to device fabrication.

Dan Hinkel, Scott Horst, and Warren Berk for their help with fabrication, and the many hours of informative and indispensable discussions, assistance, and equipment access during the fabrication of the work presented here.

The LPS and all of the members of the cleanroom staff, Toby Olver, Steve Brown, Sean Flannery, and Russell Frizzel for their assistance in device fabrication procedures, for the many hours of cleanroom training, and access to a working toaster.

## **Table of Contents**

| Dedic  | ion                                                             | ii         |

|--------|-----------------------------------------------------------------|------------|

| Ackn   | vledgements                                                     | iii        |

| Table  | f Contents                                                      | iv         |

| List o | Γablesv                                                         | /ii        |

| List o | Figuresvi                                                       | iii        |

| 1      | Introduction                                                    | . 1        |

| 1.1    | Motivation                                                      | . 1        |

| 1.2    | III-V materials                                                 | . 2        |

| 1.3    | Approach                                                        | 4          |

| 1.4    | Research Accomplishments                                        | 4          |

| 1      | Design of an epitaxial layer structure and optical MEMS devices | s <b>5</b> |

| 1      | Development of fabrication procedures                           | 6          |

| 1      | Testing of each component in the system                         | 6          |

| 1.5    | Dissertation structure                                          | . 7        |

| 2      | Literature Review                                               | 8          |

| 2.1    | History of MEMS technologies                                    | 8          |

| 2.2    | Optical MEMS                                                    | 10         |

| 2      | 2.1 Free-Space optical MEMS                                     | 11         |

| 2      | 2.2 Guided optical MEMS                                         | 15         |

| 2      | 2.3 III-V optical MEMS                                          | 18         |

| 2      | 2.4 III-V integrated photodetectors                             | 23         |

| 2      | 2.5 III-V systems integration                                   | 26         |

| 2.3    | Sensors                                                         | 28         |

| 2      | Non-MEMS chemical sensors                                       | 28         |

| 2      | Micromechanical resonator sensors                               | 30         |

| 2      | 3.3 Cantilever readout                                          | 31         |

| 3      | Theory & Design                                                 | 35         |

| 3.1    | System design overview                                          | 35         |

| 3.2    | Epitaxial layer structure growth                                | 38         |

|        | 1 Pand etmotura                                                 | 20         |

| 3.2.2 | Initial layer structure considerations             | 42  |

|-------|----------------------------------------------------|-----|

| 3.3   | Integrated laser source                            | 42  |

| 3.3.1 | Laser diode design and layout                      | 43  |

| 3.4   | Waveguides                                         | 46  |

| 3.4.1 | Waveguide strain                                   | 46  |

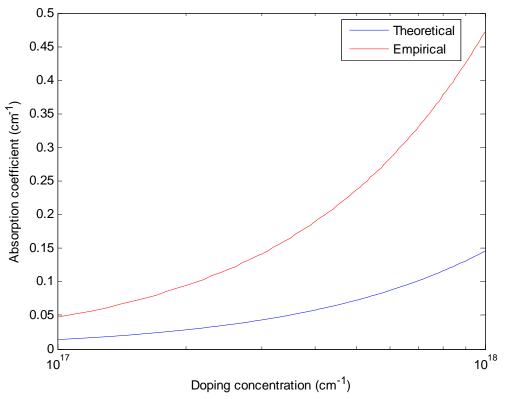

| 3.4.2 | Free carrier absorption                            | 47  |

| 3.4.3 | Cantilever waveguides                              | 50  |

| 3.4.4 | Suspended waveguide design                         | 59  |

| 3.4.5 | Cantilever waveguide resonator design and layout   | 62  |

| 3.5   | Integrated PIN photodiode                          | 64  |

| 3.5.1 | Core-absorber architecture                         | 64  |

| 3.5.2 | Diode response time                                | 66  |

| 3.5.3 | Core-absorber intrinsic region optical performance | 71  |

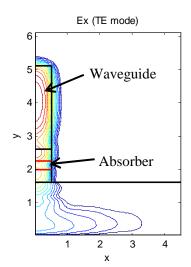

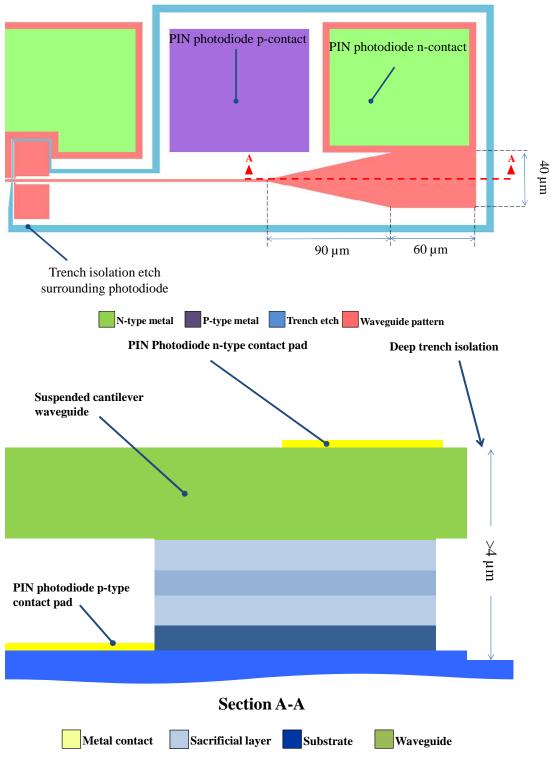

| 3.5.4 | PIN Photodiode design and layout                   | 77  |

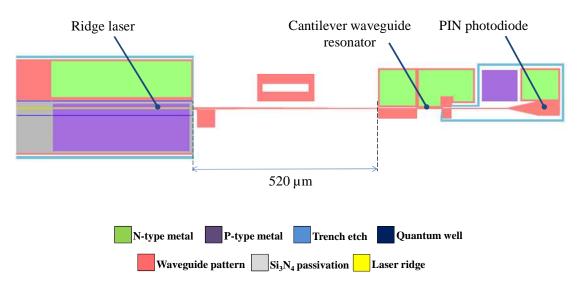

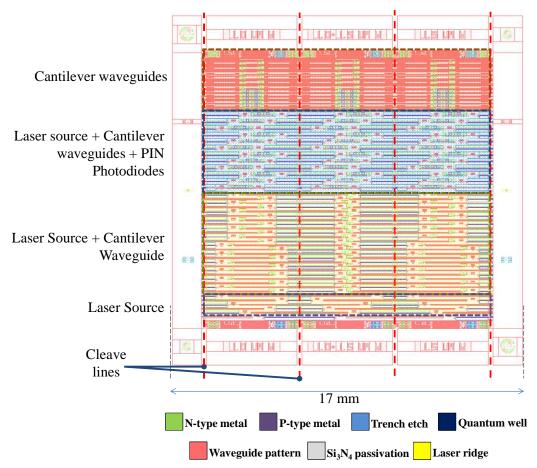

| 3.6   | Final device layout                                | 79  |

| 4     | Fabrication                                        | 82  |

| 4.1   | Introduction                                       | 82  |

| 4.2   | Fabrication process flow                           | 82  |

| 4.3   | Unit process developments                          | 93  |

| 4.3.1 | Photoresist processing                             | 93  |

| 4.3.2 | Dielectric deposition                              | 104 |

| 4.3.3 | Reactive Ion Etching (RIE)                         | 107 |

| 4.3.4 | Inductively coupled plasma (ICP) etching           | 111 |

| 4.3.5 | Metal contact deposition                           | 125 |

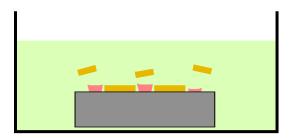

| 4.3.6 | Wet undercut etching and critical point drying     | 136 |

| 4.4   | Fabricated device                                  | 143 |

| 5     | Device testing and analysis                        | 146 |

| 5.1   | Fabrication run 1                                  | 147 |

| 5.1.1 | Testing setup and procedures                       | 147 |

| 5.1.2 | Laser testing results                              | 150 |

| 5.1.3 | Waveguide photodiodes                              | 160 |

| 5.1.4 | Cantilever waveguides                              | 169 |

| 5.1.5 | Cantilever waveguide and PIN photodiode testing    | 170 |

| 5.1.6      | Full system testing                                         | 171 |

|------------|-------------------------------------------------------------|-----|

| 5.1.7      | Results of coupled component testing                        | 172 |

| 5.2        | Fabrication run 2                                           | 183 |

| 5.2.1      | Laser testing results                                       | 184 |

| 5.2.2      | Cryogenic testing setup                                     | 190 |

| 5.2.3      | Cryogenic testing results and further analysis              | 192 |

| 5.3        | Conclusions and future work                                 | 198 |

| 6          | Conclusions                                                 | 204 |

| 6.1        | Summary of dissertation accomplishments                     | 204 |

| 6.2        | Conclusions and final comments                              | 206 |

| Appendix A | A: Processing Recipes                                       | 208 |

| A.1        | Photoresist recipes used                                    | 208 |

| A.2        | RIE recipes used                                            | 210 |

| A.3        | PECVD recipes used (NOVELLUS PECVD Concept deposition tool) |     |

| A.4        | ICP etch recipes used (PlasmaTherm 770 ICP)                 | 212 |

| Bibliograp | ny                                                          | 213 |

## List of Tables

| Table 3.1 Layer structure specification for entire growth, color coded for system-wide function (adapted from [166]) |

|----------------------------------------------------------------------------------------------------------------------|

| Table 3.2. Final dimensions for tether suspensions given equation (3-20) 61                                          |

| Table 3.3. Calculated loss parameters from optical mode simulations                                                  |

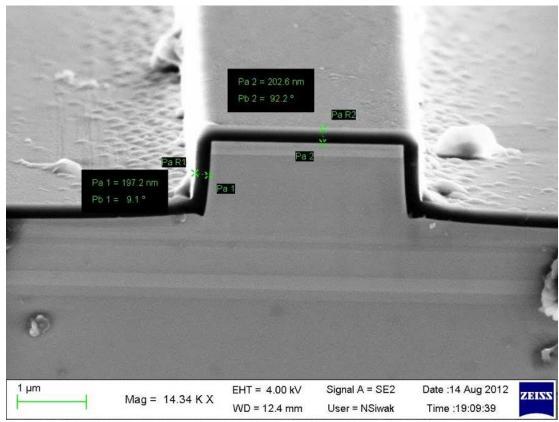

| Table 4.1. Photoresist angle and resulting transferred SiO2 angle with respect to exposure time                      |

| Table 4.2. Etch targets                                                                                              |

| Table 4.3. Correction terms for linear fitting of CTLM data                                                          |

| Table 4.4. Tabulated results from contact resistance surface preparation testing 135                                 |

| Table 4.5. Calculated undercut lateral etch rates for 5 minute etch tests of InGaAs and InGaAsP of epitaxial growth  |

| Table 5.1. Average values for tested lasers before undercut release (sample g1125a 3,4 2B)                           |

| Table 5.2. Average values for tested lasers before undercut release (sample g1125a 3,4 3B)                           |

| Table 5.3. Calculated internal laser parameters                                                                      |

# List of Figures

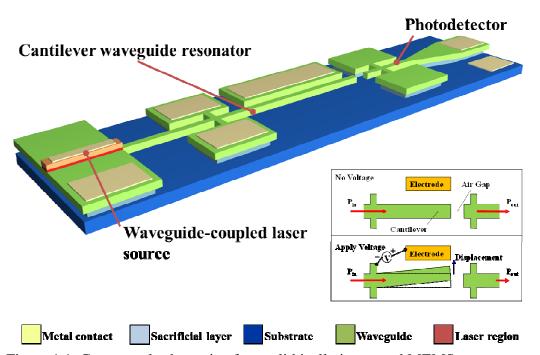

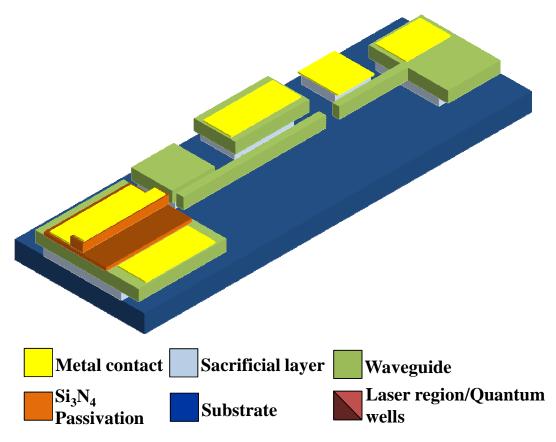

| Figure 1.1. Conceptual schematic of monolithically integrated MEMS resonant sensor with device components notated                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

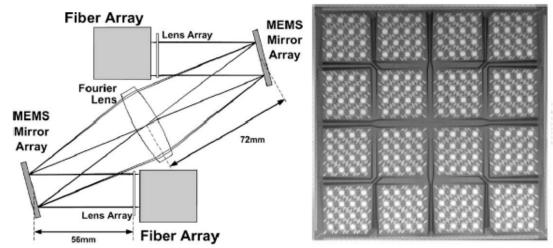

| Figure 2.1 Schematic representation of and optical MEMS beam steering switch and a top down image [67]                                                                                                                                           |

| Figure 2.2. SEM image of tilt mirrors for and optical MEMS add/drop switch [66]. 12                                                                                                                                                              |

| Figure 2.3 Lucent WaveStar LambdaRounter <sup>TM</sup> [52]                                                                                                                                                                                      |

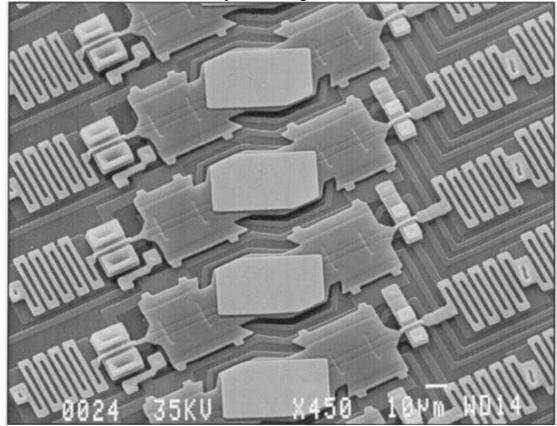

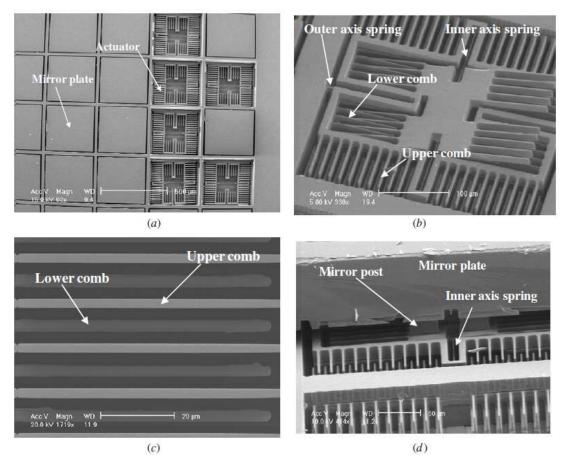

| Figure 2.4. SEM images of multi axis high form factor micromirrors [68] 14                                                                                                                                                                       |

| Figure 2.5 Texas Instruments DMD <sup>TM</sup> [40]                                                                                                                                                                                              |

| Figure 2.6 Example of waveguide switches in GaAs from [91]                                                                                                                                                                                       |

| Figure 2.7 A waveguide switch fabricated in InP [26]                                                                                                                                                                                             |

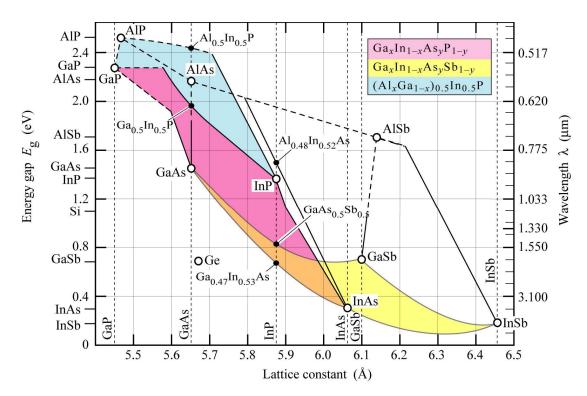

| Figure 2.8 Diagram showing the relationship between material composition, lattice constant, and bandgap for some common III-V compound semiconductors [102] 20                                                                                   |

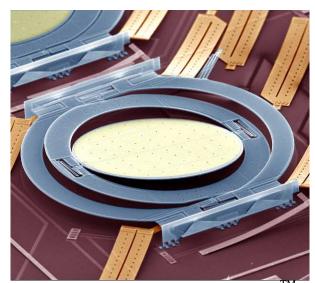

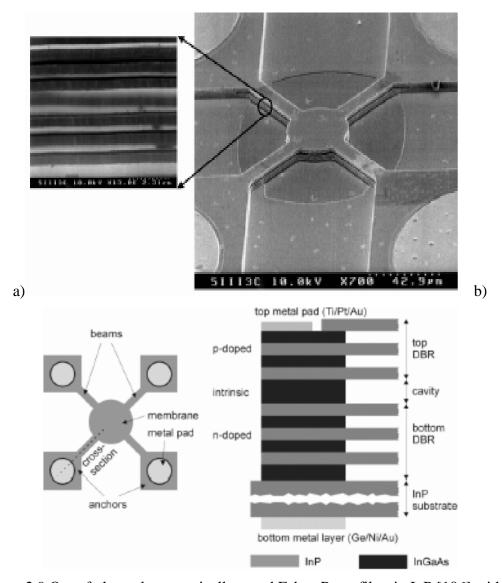

| Figure 2.9 Out of plane electrostatically tuned Fabry-Perot filter in InP [106] with a) SEM showing a device, and b) Schematic design                                                                                                            |

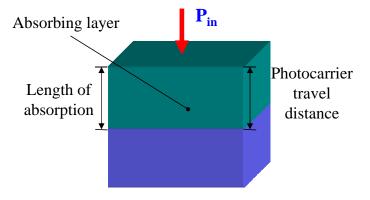

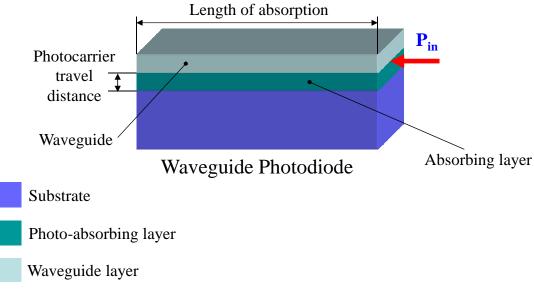

| Figure 2.10 Illustration of differences between a standard surface illuminated photodiode and a side-illuminated PIN waveguide integrated photodiode                                                                                             |

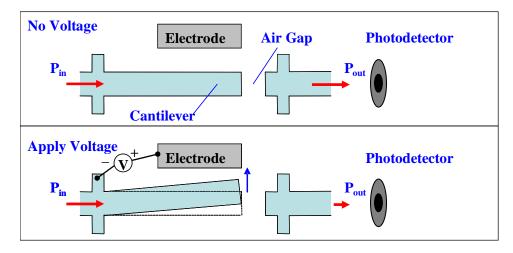

| Figure 2.11 Cantilever waveguide principle of operation                                                                                                                                                                                          |

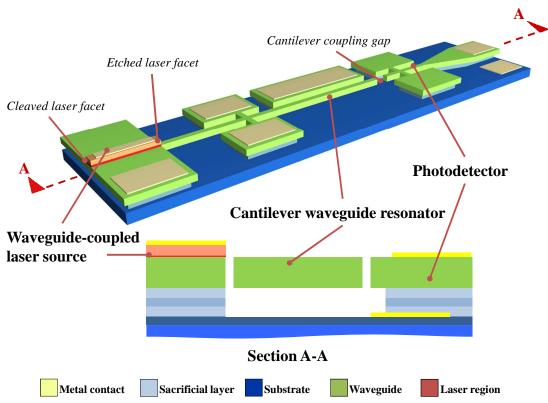

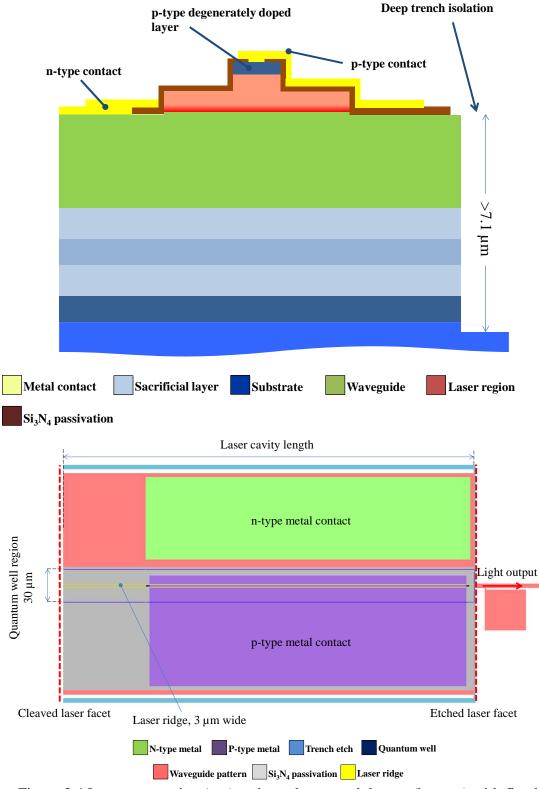

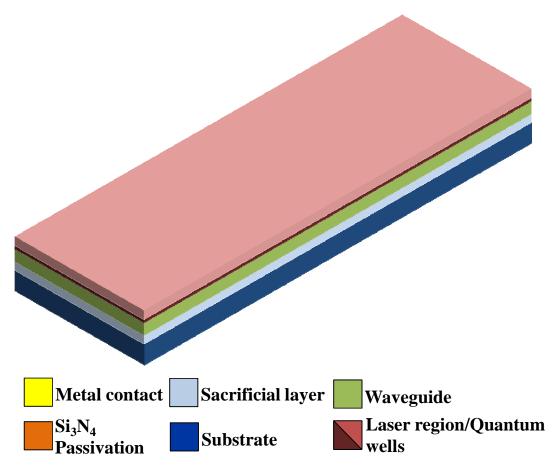

| Figure 3.1. 3-D schematic of sensor system with included Cross-sectional representation                                                                                                                                                          |

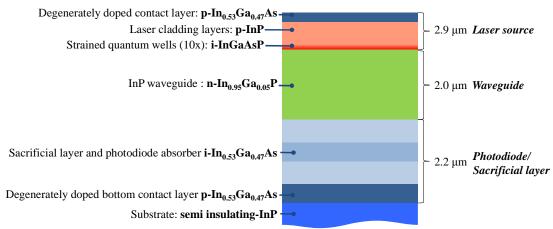

| Figure 3.2. More detailed representation of layer structure cross-section                                                                                                                                                                        |

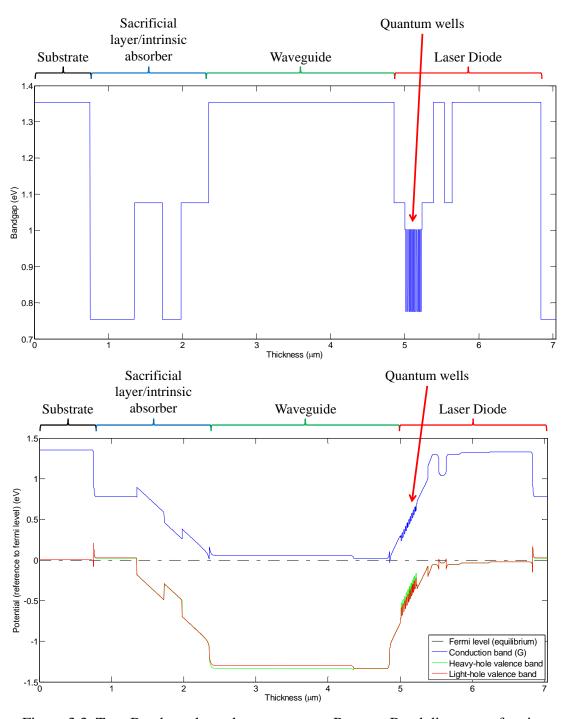

| Figure 3.3. Top: Bandgap throughout structure. Bottom: Band diagrams of entire layer structure showing the Fermi level throughout the structure. Regions of interest are identified with labels                                                  |

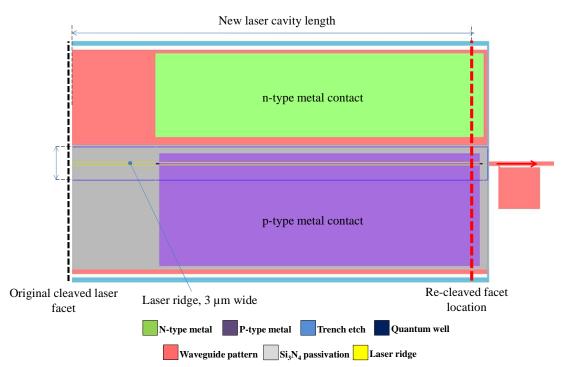

| Figure 3.4 Laser crossection (top) and top-down mask layout (bottom) with fixed dimensions specified                                                                                                                                             |

| Figure 3.5. Left: Released waveguide structures appear buckled due to compressive stress. Right: tensile stress allows for fully suspended intact waveguide structures after release, as can be seen in this doubly clamped waveguide suspension |

| Figure 3.6. Absorption versus doping concentration comparing the empirical formula with theoretical calculations                                                                                                                                 |

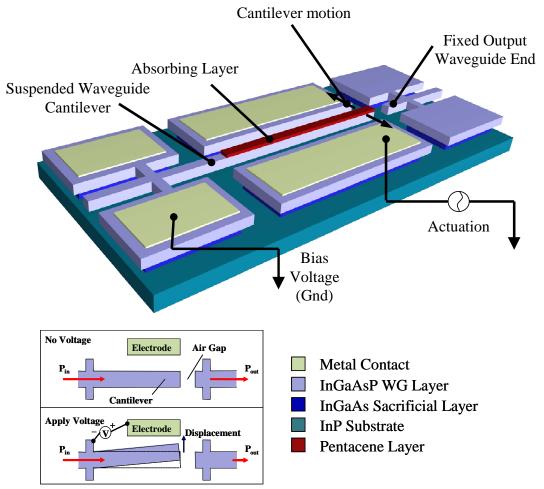

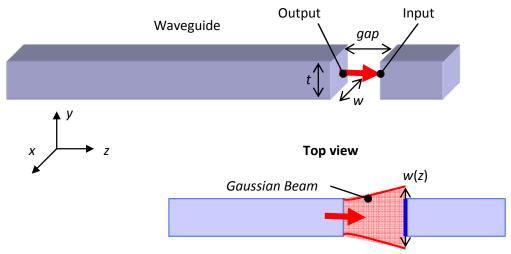

| Figure 3.7 Schematic of device components. Inset: operational principle of the readout mechanism                                                                                                                                                 |

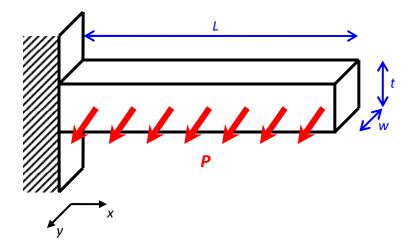

| Figure 3.8 Diagram illustrating parameters relevant to the derivation using the Euler beam equation                                                                                                                                              |

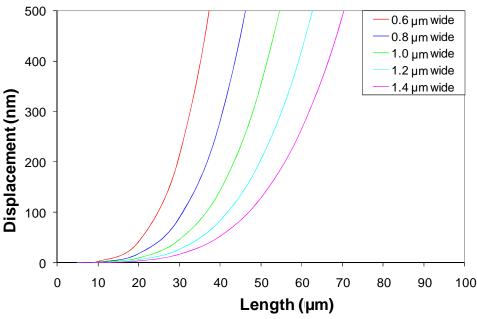

| Figure 3.9 Plot of maximum displacement versus length of cantilever for a variety of cantilever widths, with a cantilever thickness of 2 $\mu$ m                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

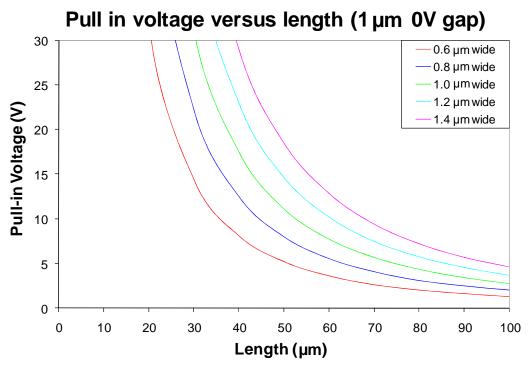

| Figure 3.10 Pull in voltage versus length for two different actuation gap widths 56                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 3.11 Diagram showing relevant dimensions and features for Gaussian beam propagation calculations                                                                                                                                                                                                                                                                                                                                                              |

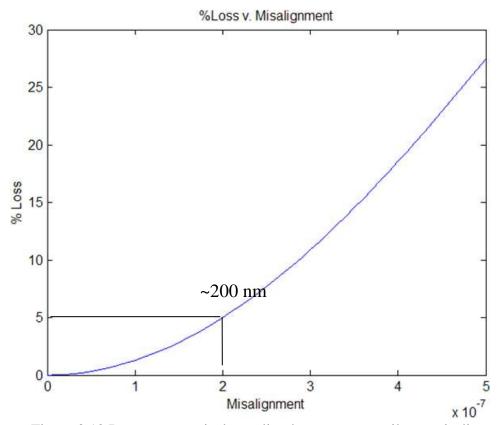

| Figure 3.12 Percentage optical coupling loss versus cantilever misalignment (in meters). Superimposed is the 5% limitation, showing intersection at approximatley 200 nm                                                                                                                                                                                                                                                                                             |

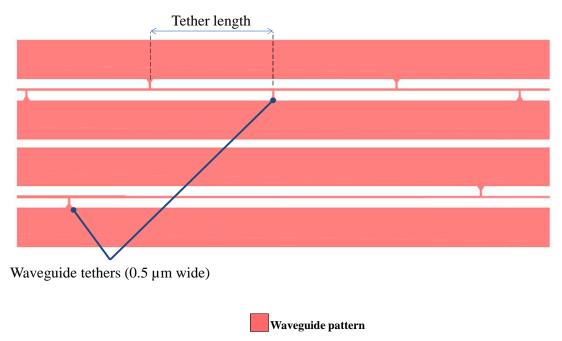

| Figure 3.13. Top-down image of waveguides and tether locations                                                                                                                                                                                                                                                                                                                                                                                                       |

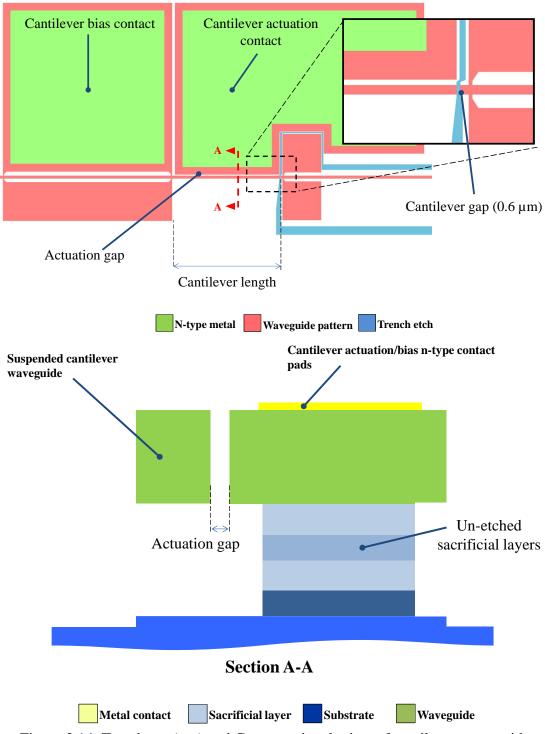

| Figure 3.14. Top-down (top) and Cross-sectional view of cantilever waveguide resonator design with relevant dimensions specified                                                                                                                                                                                                                                                                                                                                     |

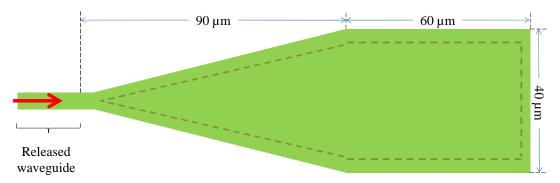

| Figure 3.15 Top-down schematic view of waveguide photodiode. Red arrow indicates incident optical radiation; dotted line indicates the estimate for the extent of the undercut etch.                                                                                                                                                                                                                                                                                 |

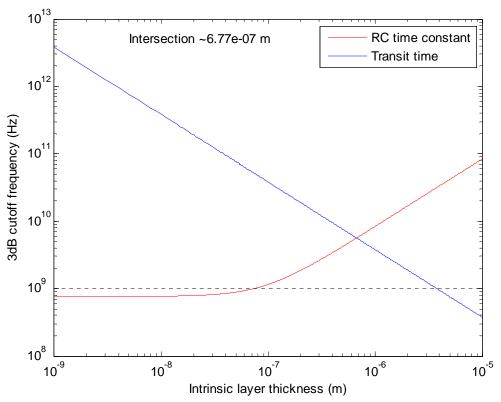

| Figure 3.16. Plot of the 3dB cutoff frequency due to junction capacitance and carrier transit-time versus the intrinsic layer thickness. Dotted line provides a guide for the eye towards 1 GHz                                                                                                                                                                                                                                                                      |

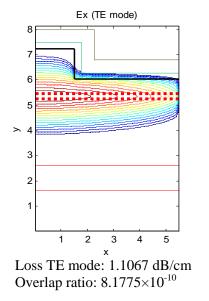

| Figure 3.17. Simulations showing the effect of a single material (left) or a core (right) sacrificial region under the laser ridge of the optical source (indicated by the solid red lines on the plot). The quantum well optical gain region is indicated by the dotted red lines. The green and gray lines represent the passivation and metalization, respectivley. Loss of the fundamental mode is presented in caption and was calculated using equation (3-35) |

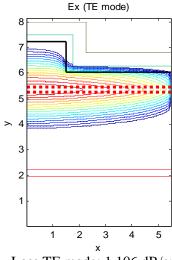

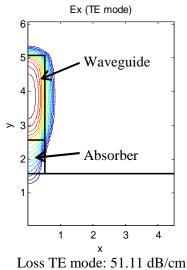

| Figure 3.18. Simulations showing the effect of a single material (left) or a core (right) sacrificial region in the waveguide-coupled PIN photodiode (indicated by the solid red lines on the plot). Loss of the fundamental mode is presented in caption and was calculated using equation (3-35)                                                                                                                                                                   |

| Figure 3.19. Top-down schematic of the photodiode region with relevant dimensions indicated (top) and a cross sectional view of the photodiode region (bottom)                                                                                                                                                                                                                                                                                                       |

| Figure 3.20. Top-down mask layout of the fully integrated laser-cantilever-and photodiode structure                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 3.21. Full die layout with device variations labeled as well as cleave lines indicated                                                                                                                                                                                                                                                                                                                                                                        |

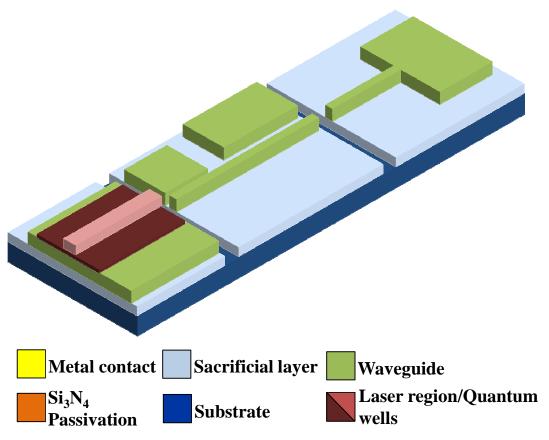

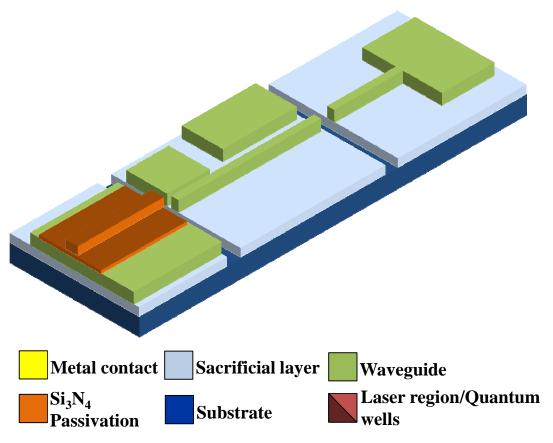

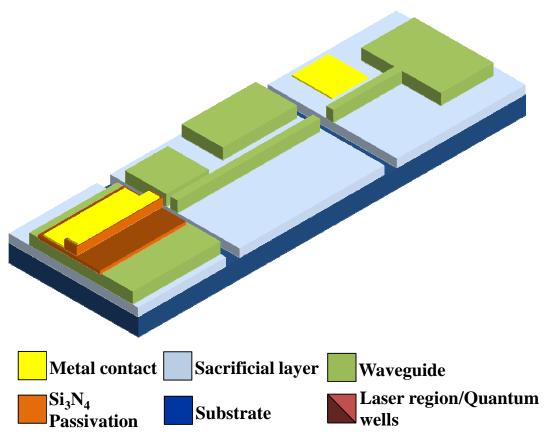

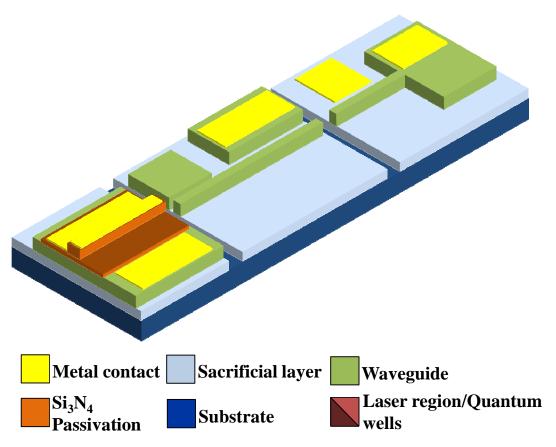

| Figure 4.1. Step 1: Blank Substrate                                                                                                                                                                                                                                                                                                                                                                                                                                  |

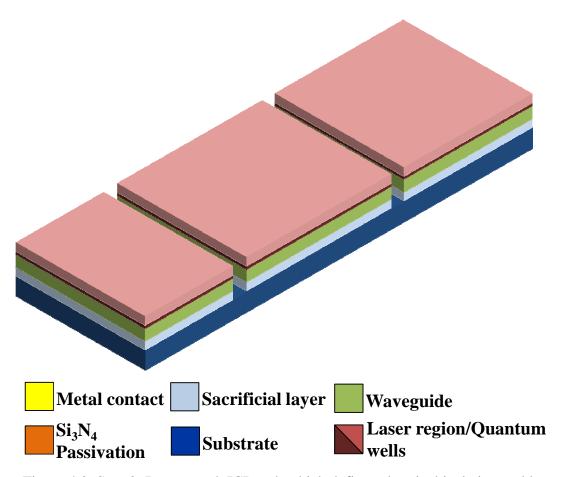

| Figure 4.2. Step 2: Deep trench ICP etch which defines electrical isolation and laser facets.                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 4.3. Step 3: Laser ridge ICP etch which defines the lateral confinement for the laser cavity.                                                                                                                                                                                                                                                                                                                                                                 |

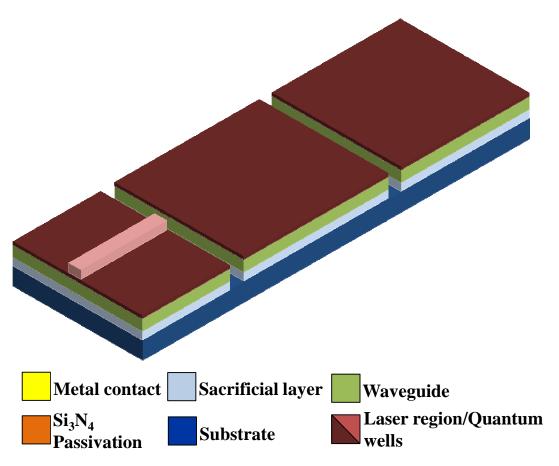

| Figure 4.4. Step 4: Quantum well ICP etch which removes active region over the wafer where it is not needed and defines vias for topside <i>n</i> -type laser contact layers.                                                                                  |

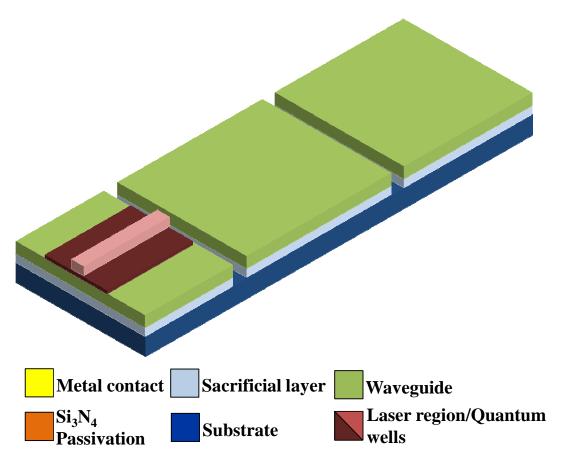

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                |

| Figure 4.5. Step 5: Waveguide and photodiode ICP etch which creates the majority of the device layout and creates vias to buried <i>p</i> -contacts for photodiodes                                                                                            |

| Figure 4.6. Step 6: Nitride passivation to protect and passivate laser region                                                                                                                                                                                  |

| Figure 4.7. Step 7: <i>P</i> -type metal lift-off                                                                                                                                                                                                              |

| Figure 4.8. Step 8: <i>N</i> -type metal lift-off and anneal                                                                                                                                                                                                   |

| Figure 4.9. Step 9: Wafer thinning, cleaving and sacrificial layer removal                                                                                                                                                                                     |

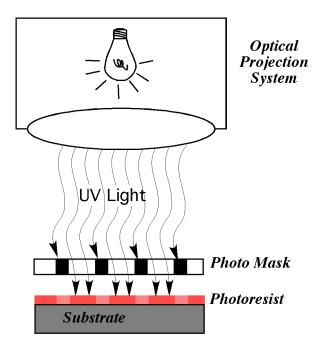

| Figure 4.10. Typical components used in photolithography [190]                                                                                                                                                                                                 |

| Figure 4.11. Diagram illustrating the lift-off procedure for negative photoresist (modified from [191])                                                                                                                                                        |

| Figure 4.12. SEM image of corrugations in the photoresist sidewall due to standing waves [192]                                                                                                                                                                 |

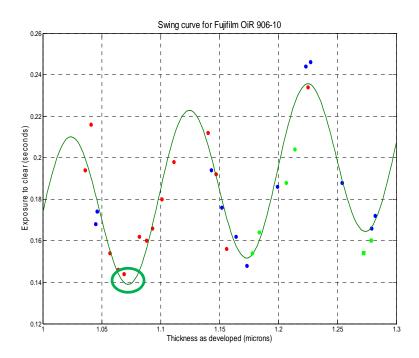

| Figure 4.13. Swing curve of Fujifilm OiR 906-10 performed at LPS by J. Hryniewicz and P. Apiratikul. Green circle indicates thickness target chosen for this process 99                                                                                        |

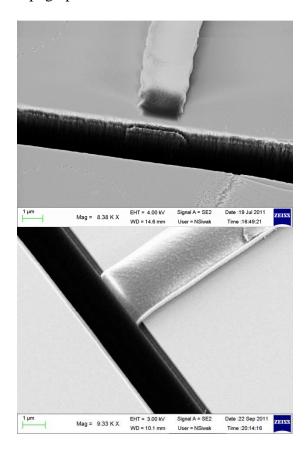

| Figure 4.14. SEM showing the effect of poor photoresist coverage using OiR 906-10 (Left) and good photoresist coverage using OiR 908-35 (Right) on the resulting SiO <sub>2</sub> hardmask pattern. Notice the sloped profile of the poor coverage example 102 |

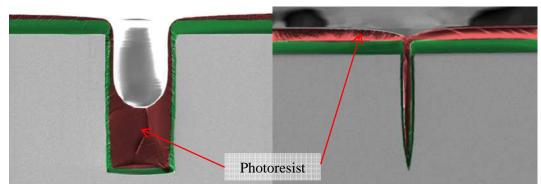

| Figure 4.15. SEM images of OiR 908-35 spin coated over varying etched geometries (colored red), notice how the corner of some areas are still nearly unprotected. Green areas are SiO <sub>2</sub> coatings and grey areas are the underlying substrate        |

| Figure 4.16. SEM crossection of laser ridge, showing Si <sub>3</sub> N <sub>4</sub> passivation coating 107                                                                                                                                                    |

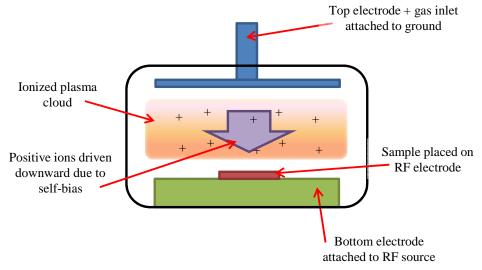

| Figure 4.17. Schematic diagram of reactive ion etching (RIE) chamber 107                                                                                                                                                                                       |

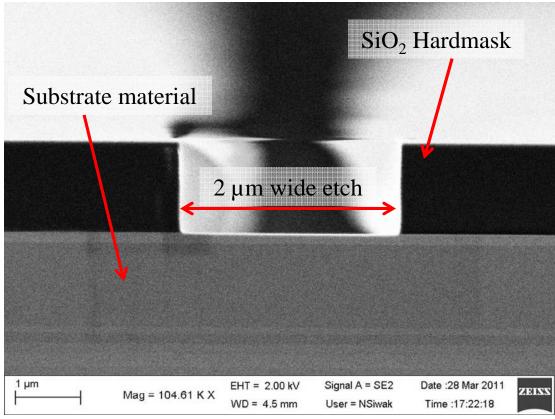

| Figure 4.18. SEM image of a transferred SiO <sub>2</sub> oxide hardmask                                                                                                                                                                                        |

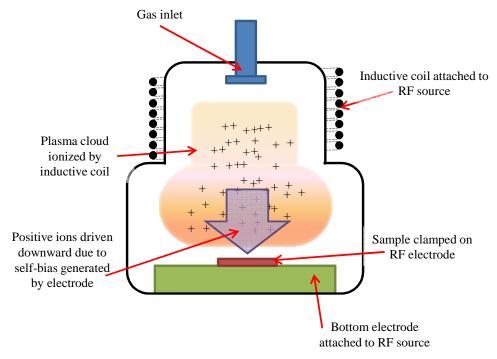

| Figure 4.19. Schematic diagram of ICP etching chamber                                                                                                                                                                                                          |

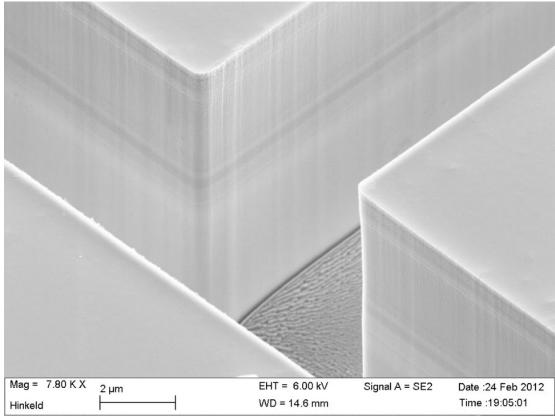

| Figure 4.20. SEM of smooth deep-etched epitaxial sample                                                                                                                                                                                                        |

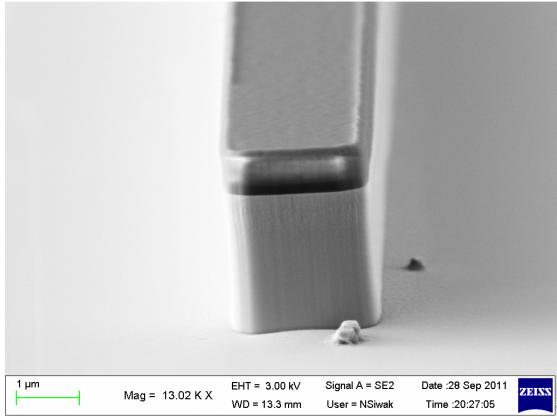

| Figure 4.21. SEM image of slower etch rate with the laser ridge etch pattern. Oxide hardmask has not been removed                                                                                                                                              |

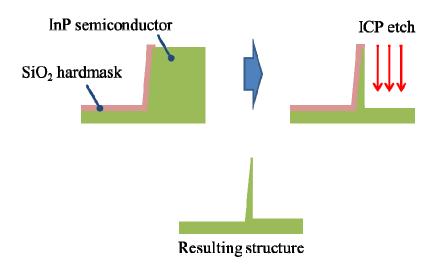

| Figure 4.22. Diagram illustrating the effect of sidewall oxide hardmask on nested etching                                                                                                                                                                      |

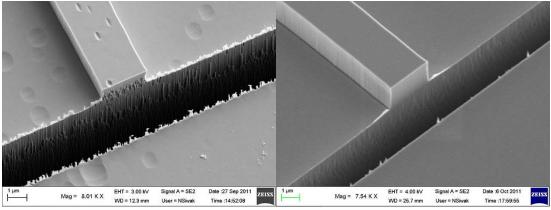

| Figure 4.23. SEM images illustrating the fence structure Left: residues resulting from a poor overetch of the oxide hardmask, and Right: Cleaner edge due to proper hardmask overetch.                                                                         |

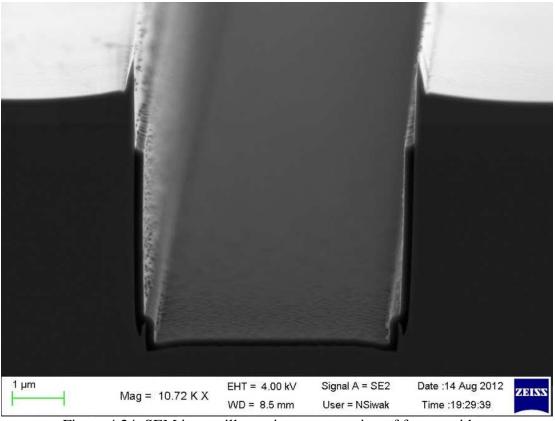

| Figure 4.24. SEM image illustrating a crossection of fence residue                                                                                                                                                                                             |

| Figure 4.25. Diagram illustrating the 4 etches employed and their depth targets relative to the original epitaxial layer structure. 1) Trench etch, 2) Ridge etch, 3) Quantum well etch, 4) Waveguide etch                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

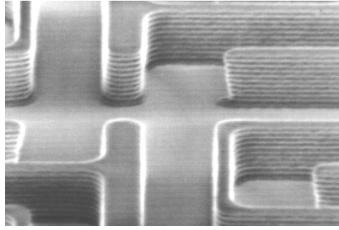

| Figure 4.26. Top-down colorized SEM of entire device, with color coated depth indication after each etching step. Red: Unetched depth, Yellow: Trench etch (#1), Purple: Ridge etch (#2), Blue: Quantum well etch (#3), Green: Waveguide etch (#4).                                                                                                                |

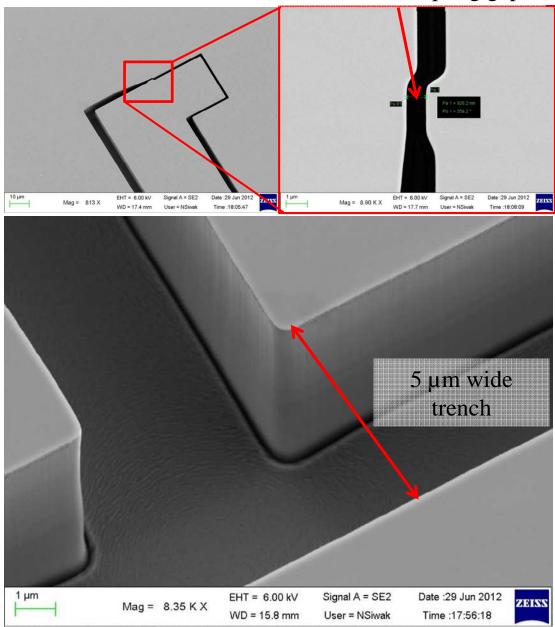

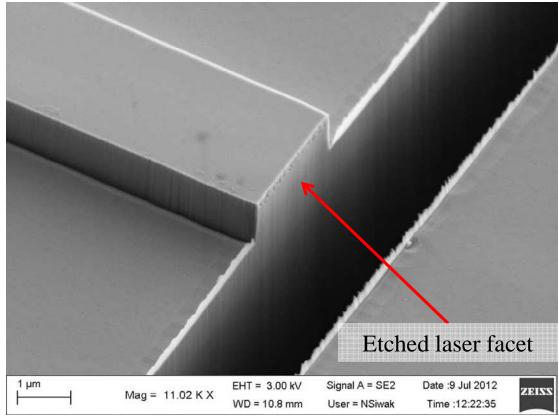

| Figure 4.27. SEM images of the deep ICP trench etch. 122                                                                                                                                                                                                                                                                                                           |

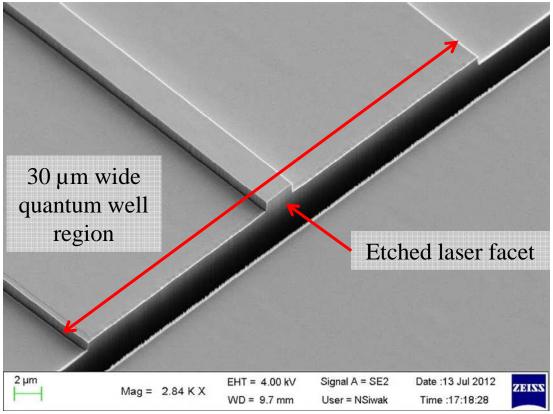

| Figure 4.28. SEM image of laser facet with the defined laser ridge                                                                                                                                                                                                                                                                                                 |

| Figure 4.29. SEM image showing the quantum well etched region centered on the laser ridge                                                                                                                                                                                                                                                                          |

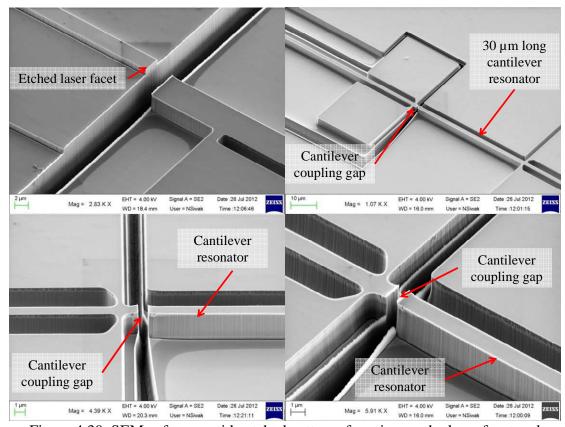

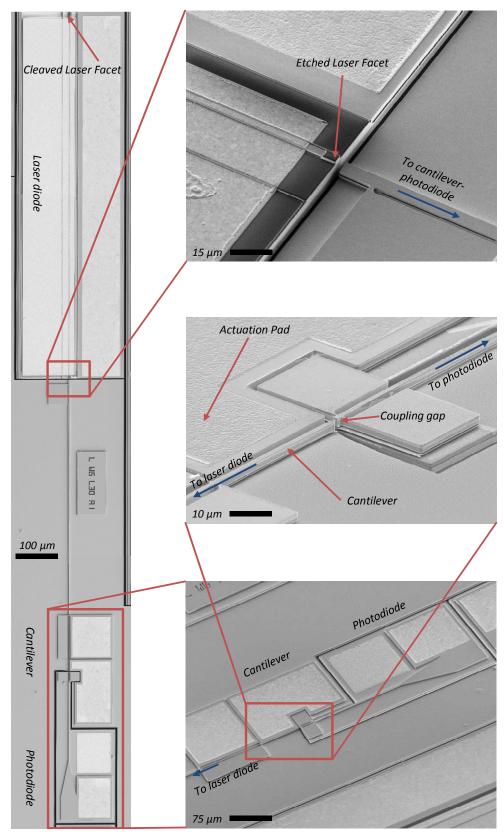

| Figure 4.30. SEMs of waveguide etched patterns focusing on the laser facet and coupled waveguide areas (Top left), the cantilever structures (Top right), and around the cantilever gap defined by the first trench etch (Bottom row)                                                                                                                              |

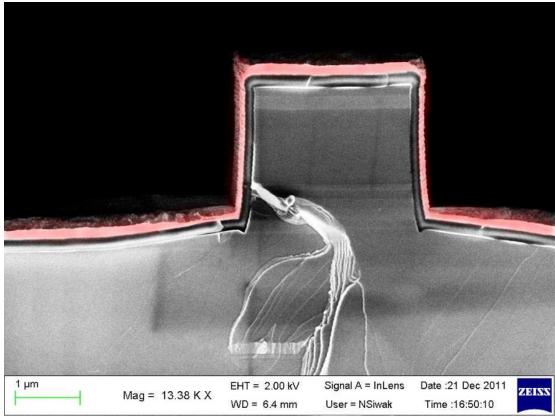

| Figure 4.31. SEM image of metallization (tinted red) achieving continuity from the bottom to the top of the narrow laser ridge structure via planetary evaporation 127                                                                                                                                                                                             |

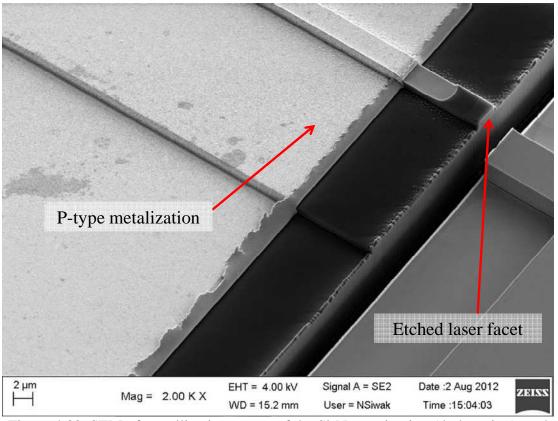

| Figure 4.32. SEM of metallization on top of the $Si_3N_4$ passivation (dark region), and covering the laser ridge.                                                                                                                                                                                                                                                 |

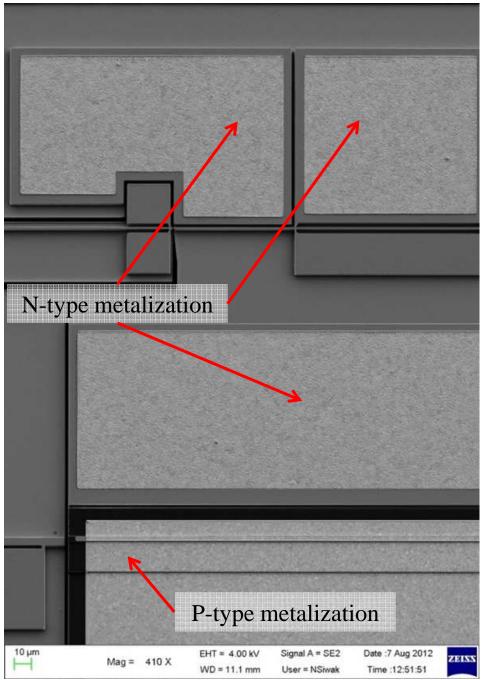

| Figure 4.33. SEMs of $n$ -metallization after annealing steps are completed. Left shows the rough morphology of the metal contact pads in the cantilever. Right shows the laser region with $p$ -contacts over top of the dark $Si_3N_4$ passivation. Notice the difference in surface roughness between the $n$ and $p$ contact metals                            |

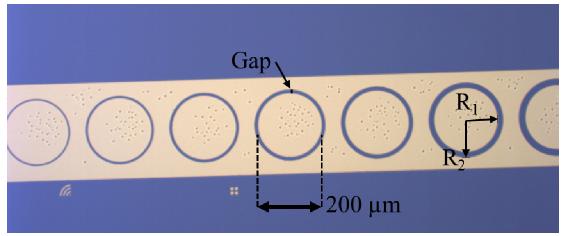

| Figure 4.34. Optical micrograph showing CTLM metalized pattern used for contact resistance and sheet resistivity tests.                                                                                                                                                                                                                                            |

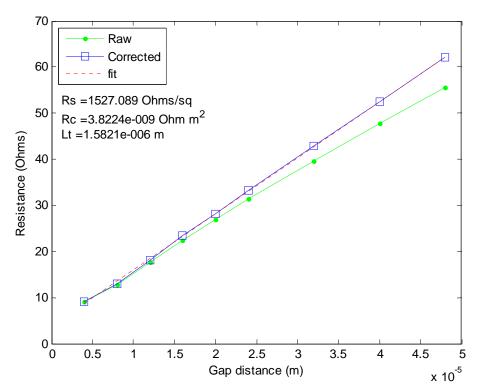

| Figure 4.35. Example data from CTLM measurements showing raw and corrected data for a set of measurements                                                                                                                                                                                                                                                          |

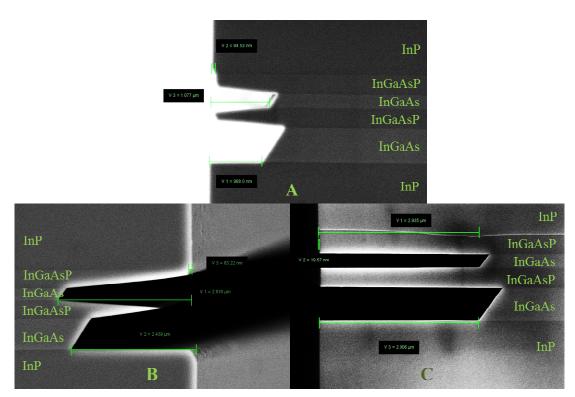

| Figure 4.36. Cross-sectional SEM images of undercut samples with layers labeled A) H <sub>3</sub> PO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O, B) H <sub>2</sub> SO <sub>4</sub> :H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O, C) HF:H <sub>2</sub> O <sub>2</sub> :H <sub>2</sub> O                                                      |

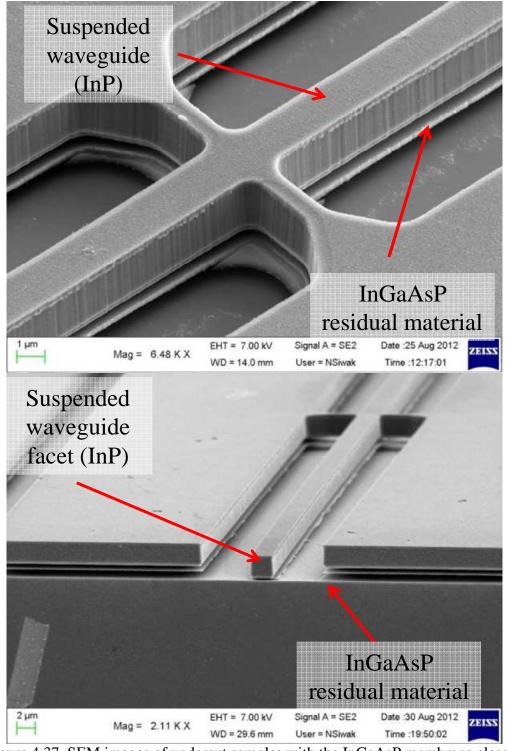

| Figure 4.37. SEM images of undercut samples with the InGaAsP membrane clearly visible beneath the waveguides                                                                                                                                                                                                                                                       |

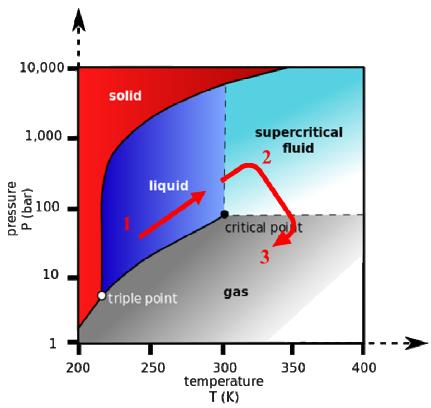

| Figure 4.38. Phase diagram of CO <sub>2</sub> showing the critical point and the supercritical point dry process. 1) Liquid CO <sub>2</sub> is pumped into the chamber, the temperature and pressure increased beyond the critical point 2) once in the supercritical fluid phase, the pressure is reduced until the gas phase is achieved. Adapted from [221] 142 |

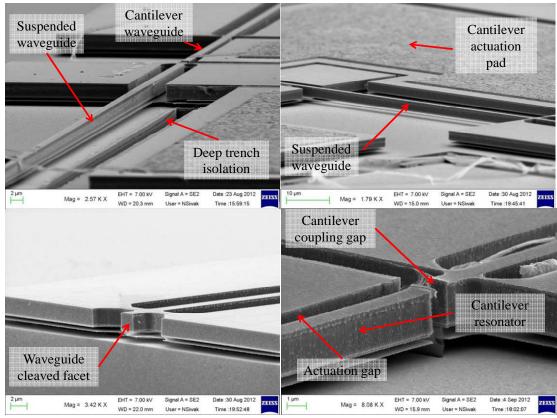

| Figure 4.39. SEMs of various undercut and CO <sub>2</sub> critical point dried cantilevers and waveguides                                                                                                                                                                                                                                                          |

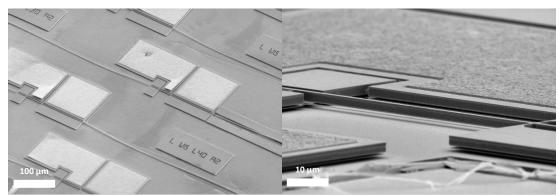

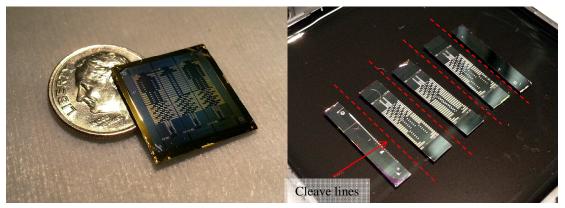

| Figure 4.40. Photographs of completed die (left), and a thinned and cleaved die into the 3 chips (right)                                                                                                                                                                                                                                                           |

| Figure 4.41. SEMs of completed device showing the relative locations of laser light source, cantilever waveguide, and photodiodes                                                                                                                                                                                                                                  |

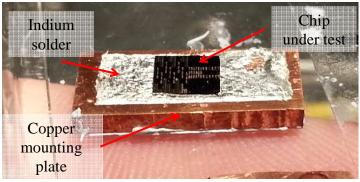

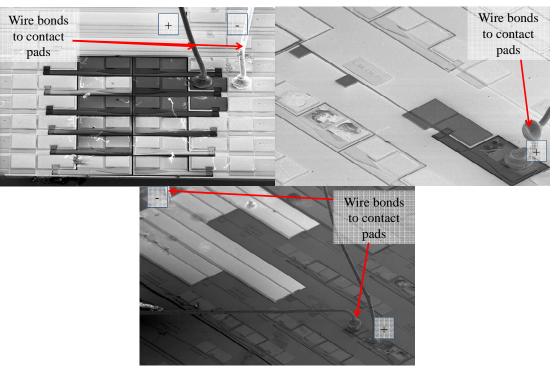

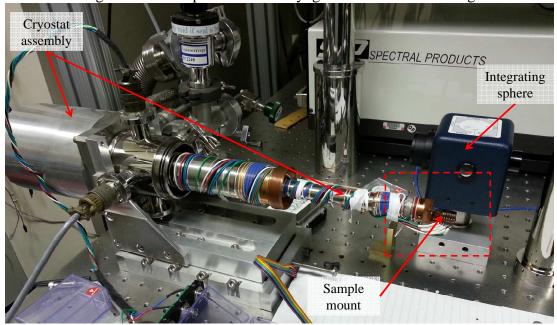

| Figure 5.1. Standard sample mounting                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

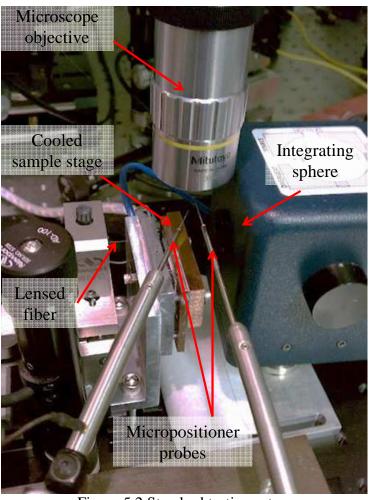

| Figure 5.2 Standard testing setup. 148                                                                                                                                                                         |

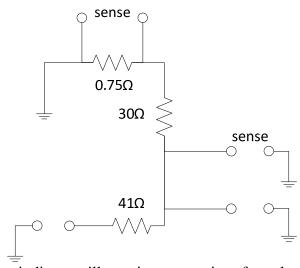

| Figure 5.3. Circuit diagram illustrating connections for pulsed testing setup 150                                                                                                                              |

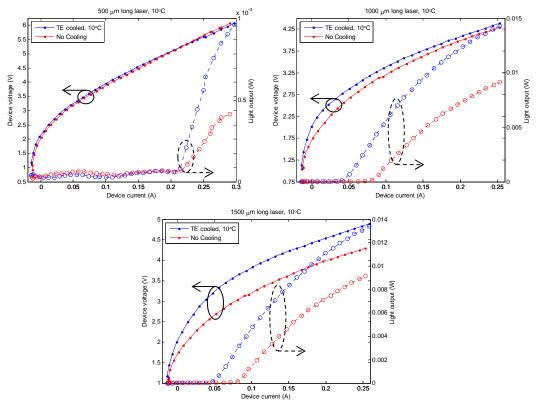

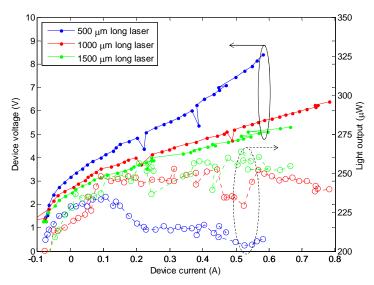

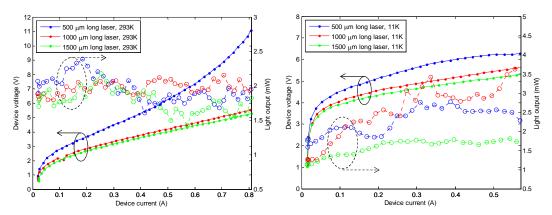

| Figure 5.4. LIV measurements of working lasers with only passive cooling to the copper heatsink (no cooling) and actively cooled to $10^{\circ}$ C. All three lengths are represented: 500, 1000, 1500 $\mu$ m |

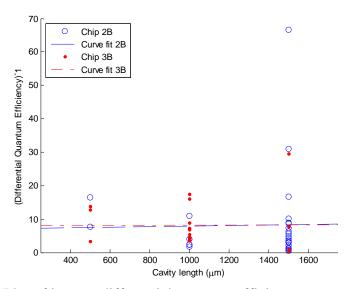

| Figure 5.5. Plot of inverse differential quantum efficiency versus cavity length 155                                                                                                                           |

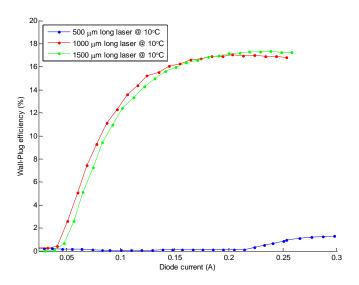

| Figure 5.6. Plot of the wall plug efficiency versus the diode current                                                                                                                                          |

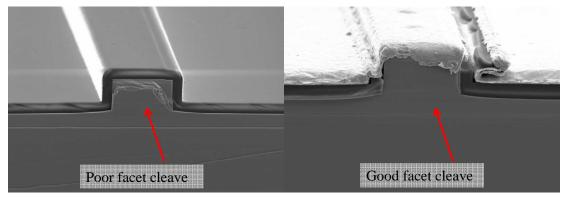

| Figure 5.7. SEM images showing examples of a cracked facet and smooth facet after cleaving                                                                                                                     |

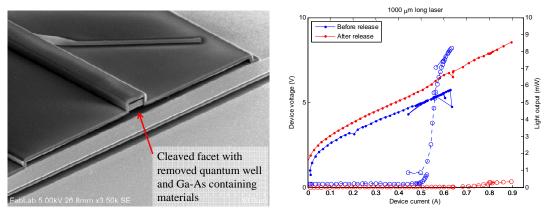

| Figure 5.8. Left: SEM showing cleaved laser facet with completely removed InGaAsP quantum well regions. Right: L-I-V characteristics of the same laser diode before and after the undercut release             |

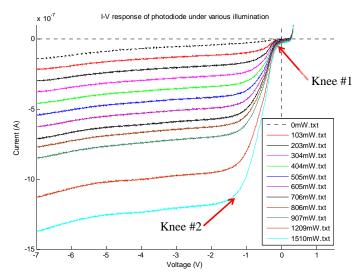

| Figure 5.9. I-V curves of photodiode reverse bias characteristics under varied illumination intensities, top: semilog, bottom: linear                                                                          |

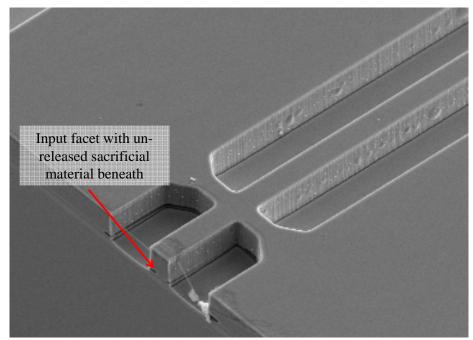

| Figure 5.10. SEM of input waveguide facet showing un-released absorber at the input                                                                                                                            |

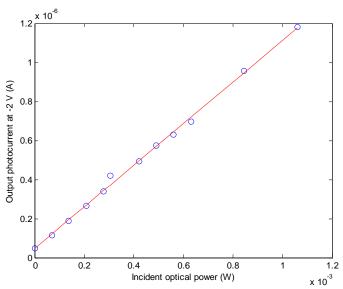

| Figure 5.11. Output photocurrent at -2V revers bias versus input incident optical power                                                                                                                        |

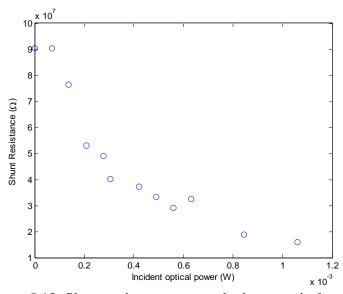

| Figure 5.12. Shunt resistance versus the input optical power                                                                                                                                                   |

| Figure 5.13. Linear I-V characteristics of the photodiode under various illumination powers                                                                                                                    |

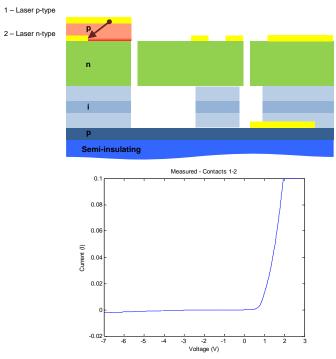

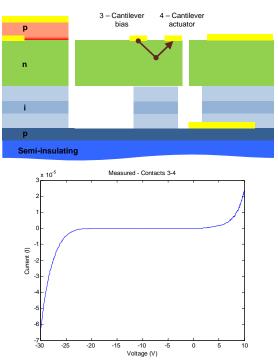

| Figure 5.14. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured                                       |

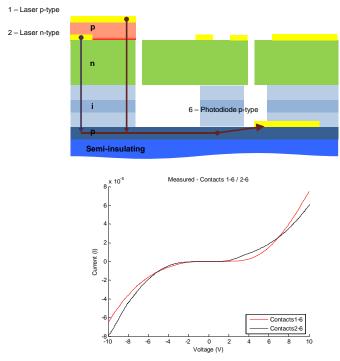

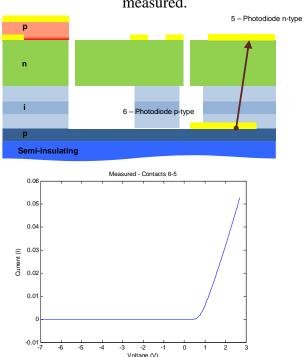

| Figure 5.15. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured                                       |

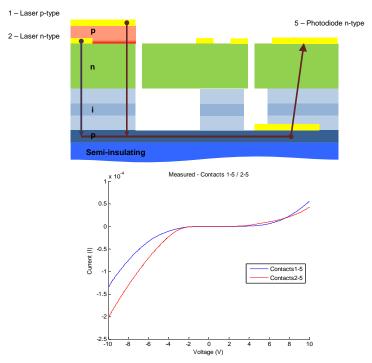

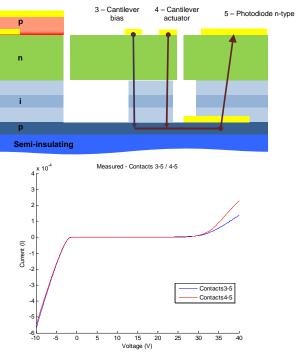

| Figure 5.16. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured.                                      |

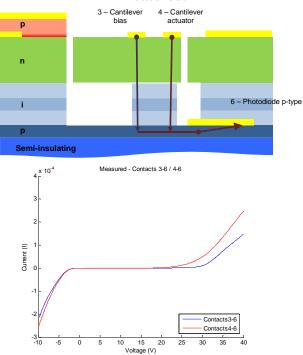

| Figure 5.17. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured.                                      |

| Figure 5.18. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured.                                      |

| Figure 5.19. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.20. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured                                              |

| Figure 5.21. Device cross-section and numerated contact points. Numbers on cross-section coincide with labels on graphs. Red arrow indicates current path being measured.                                             |

| Figure 5.22. Voltage contrast SEM imaging of devices, showing current pathways through in-situ voltage application. Dark areas have positive voltage applied, and light areas have negative voltage applied           |

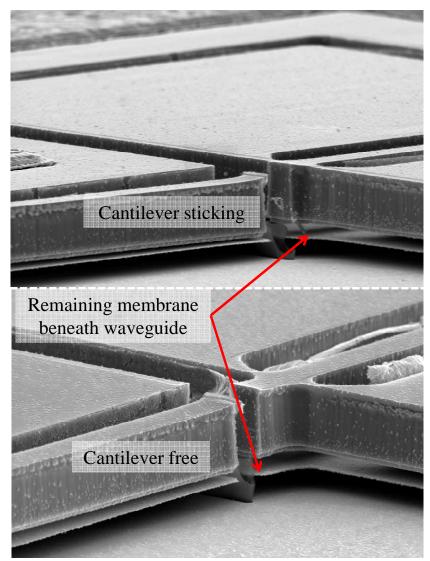

| Figure 5.23. SEM images of released cantilever tips showing unetched layer beneath                                                                                                                                    |

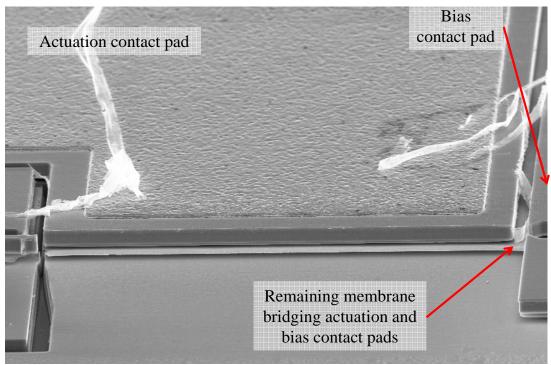

| Figure 5.24. SEM of actuation-bias contact pad region with cantilever resonator removed, showing the underlying membrane and the bridging of the separation gap                                                       |

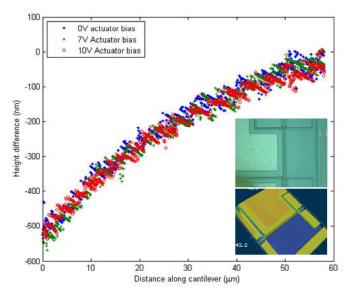

| Figure 5.25. Plot of normalized height along the top of the cantilever during applied voltage. Right side is clamped portion of the cantilever. Inset shows microscope and false-color 3D image from optical profiler |

| Figure 5.26. Example of LIV curves for second fabrication run devices                                                                                                                                                 |

| Figure 5.27. SEM of before and after Si <sub>3</sub> N <sub>4</sub> removal via RIE etching. Residual dielectric can be seen deep in the trench, indicating removal of the coating 185                                |

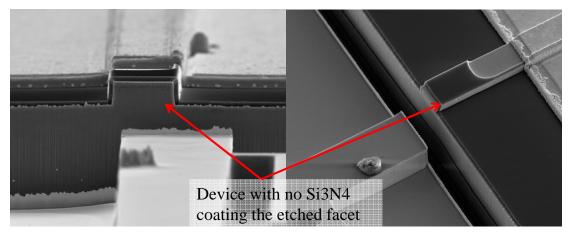

| Figure 5.28. SEM of device with misalignment errors that left it natively un-coated.                                                                                                                                  |

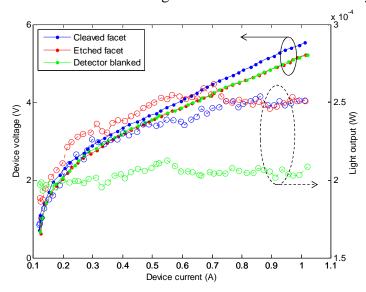

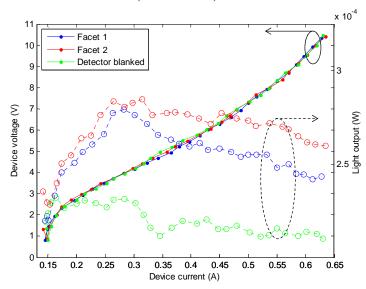

| Figure 5.29. LIV curves of a device that has had the nitride removed, measured at each facet and with the detector blanked.                                                                                           |

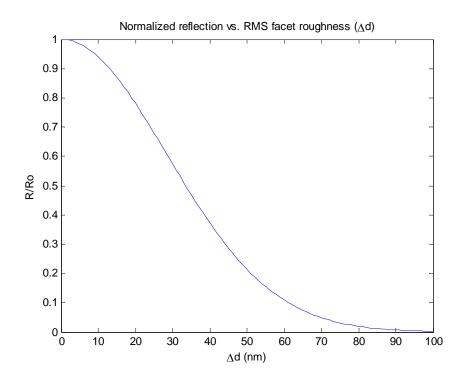

| Figure 5.30. Facet reflectance versus the RMS roughness of the laser facet for the case of the fabricated laser diodes                                                                                                |

| Figure 5.31. Top down diagram illustrating the location of the re-cleaved laser facet (not to scale)                                                                                                                  |

| Figure 5.32. LIV curves for a device that has two cleaved facets. Output power shown from both sides of the laser, as well as a plot of the detector input blanked. 189                                               |

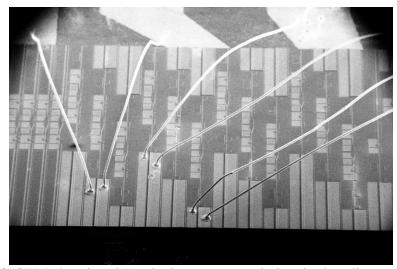

| Figure 5.33. SEM showing three devices connected via wire bonding, notice one of each laser length is connected for cryo-testing                                                                                      |

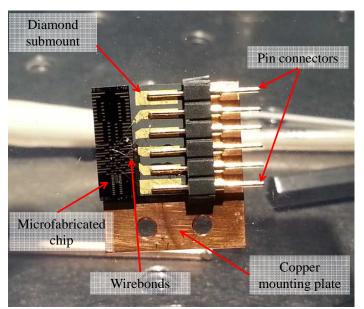

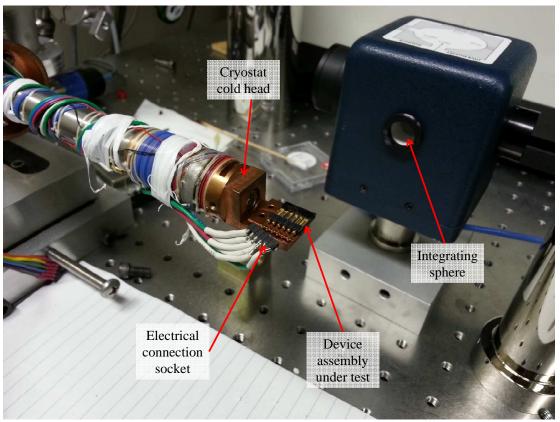

| Figure 5.34. Sample mount for cryogenic and vacuum testing                                                                                                                                                            |

| Figure 5.35. Full cryogenic testing setup, dotted line references close up of the coldhead in Figure 5.36                                                                                                             |

| Figure 5.36. Close-up image of the coldhead assembly with sample attached 192                                                                                                                                         |

| Figure 5.37. LIV plots of three laser cavities at room temperature (Left) and cryogenically cooled to 11K (Right)                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

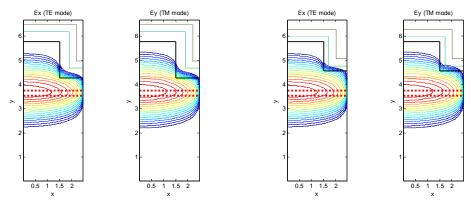

| Figure 5.38. Output of modesolver simulations for (left) Fabrication run 1 and (right) Fabrication run 2. Dotted lines indicate the location of the quantum well gain region green lines indicate the Si <sub>3</sub> N <sub>4</sub> coating, and the brown lines on top indicate the gold contact material |

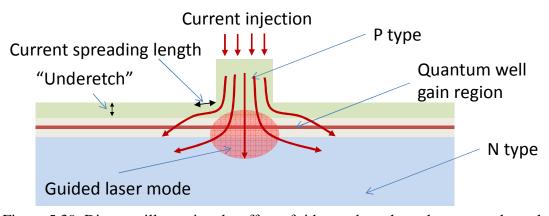

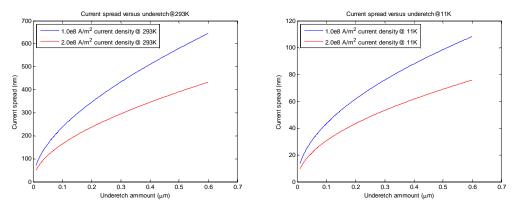

| Figure 5.39. Diagram illustrating the effect of ridge underetch on the current through the guided laser mode in the gain region                                                                                                                                                                             |

| Figure 5.40. Plots of simulated current spreading versus underetch amount at multiple temperatures                                                                                                                                                                                                          |

### 1 Introduction

### **Motivation**

The need to monitor the environment and detect various chemicals is a critical task for industrial, military, and homeland defense applications. Recent developments around the world, such as terrorism and bioterrorism, beg the need for devices which can be used to screen and measure levels of toxins in a variety of situations. Biological hazards such as anthrax and the flu virus pose serious challenges for sensing technologies [1]. In addition to these biological hazards, chemical sensors are also sought for the detection and prevention of exposure to chemical warfare agents which have been common on the modern battlefield [2]. Additionally, chemical monitoring in industrial applications and emissions measurement have both continued to be areas of research requiring sensors that can be readily deployable and able to withstand severe operating conditions.

In each of these cases, detecting and identifying agents quickly and accurately while maintaining a system with low power, minimal infrastructure, high sensitivity, and portability is highly desired. Recent sensing methodologies which are common for these applications have been focused on technologies utilizing thermal sensors, capacitance sensors, and optical transmission [3-6]. These devices have the benefit of being readily fabricated and simple to implement and use. Integrating these components with electronics and other devices has been a major thrust in the development of these devices and has been the subject of much research in this area.

The integration of sensor systems can present a number of difficulties stemming from various packaging and interfacing schemes, which are often conflicting in their requirements. MEMS technology is ideal in terms of providing infrastructure and materials for systems-based approaches. With fabrication technologies and devices directly compatible with conventional silicon technology, MEMS has been a multi-disciplinary and diverse field in the study of systems engineering and integration. This makes MEMS technology ideal for the development of these future sensor systems, as the importance of portability and mass production become more important. Cantilever-based MEMS sensors are prime candidates to be used as portable chemical sensors due to their relative simplicity [7], flexibility [8, 9], and compatibility with conventional processes [10, 11].

#### III-V materials

III-V materials have long been studied for use in high performance electronic and optical systems. With the development of epitaxial growth, it has allowed researchers to grow compound semiconductors with nearly arbitrary composition, and thus exhibiting widely varied material characteristics. With the ability to dictate properties such as the bandgap, refractive index, and fabrication selectivity of each individual layer has come the broadened scope and vision for researchers and the expansion of the field of compound semiconductors into previously unexplored territories.

The initial push for the use of compound semiconductors stemmed from the very high electron mobilities, mean-free-paths and the direct-bandgap electronic

structure possessed by III-V semiconductors over traditional silicon based technology [12]. Many authors have highlighted the high speed transistor technologies made possible through the development of InP-GaAs compound semiconductor epitaxy. Devices such as HEMT's [13], MODFET's [14], and integrated optical receivers/HEMT's [15] are made possible through the unique electronic properties of III-V semiconductors.

A primary advantage of III-V materials is their tailorable direct bandgap via the growth process that enables growth of material exhibiting optical gain. GaAs was one of the frontrunners in this field of solid-state optics with a maximum bandgap wavelength of ~870nm, sufficient for early generation communication systems. With the transition to longer wavelength communications technologies, particularly 1.55  $\mu$ m, InP soon emerged as an alternative material system to enable the fabrication of longer-wavelength active devices (1.660  $\mu$ m – 0.925  $\mu$ m) [16, 17]. The continued quest for high speed communications technologies combined with the ability to create active optical elements and high speed electronics in InP simultaneously brought about the first monolithic integration of these optical and electrical components; such as high speed optical receivers and modulators [15].

In recent years, microelectromechanical systems (MEMS) using InP-based materials have been investigated to augment these optical networks [18]. A number of examples have been reported in literature of optical modulators and demultiplexers [19-24], couplers [25, 26] all designed in III-V materials to facilitate monolithic integration of these optical components with photodetectors and sources.

### Approach

The approach of this dissertation is to take advantage of the versatility of III-V semiconductors to facilitate the monolithic integration of a MEMS resonant sensor, as depicted below in Figure 1.1. A novel interrogation technique will be used to measure a MEMS resonant sensor that includes the use of an on-chip light source, and an on-chip photodiode. This work builds upon previous work [26-32] which served to develop each component of this system separately, with the culmination of ultimately integrating them on one chip.

Figure 1.1. Conceptual schematic of monolithically integrated MEMS resonant sensor with device components notated.

### Research Accomplishments

This dissertation seeks to explore the monolithic integration of optical sources and photodetectors with passive waveguides developed in the Indium Phosphide (InP) material system to establish a **single-chip** resonator sensor utilizing a novel readout

technique. These sensors are intended to be general-purpose, functioning as a microbalance sensor to measure chemical reactions, vapors, radiation, or fluid flow. The bulk of the research work performed for this project lies in the design of the integration scheme and the development of the fabrication procedures utilized to realize the integrated system.

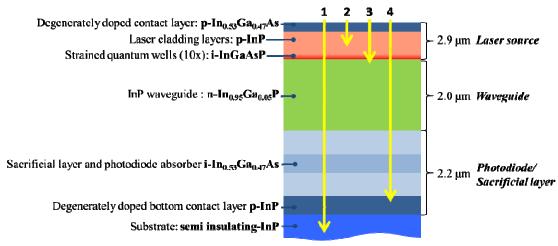

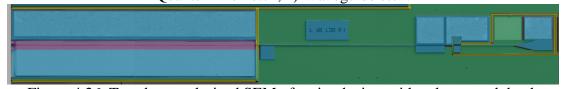

# 1.1.1 Design of an epitaxial layer structure and optical MEMS devices

A vertically offset monolithic integration scheme was designed for the integration of a multiple quantum well laser source, an optical MEMS cantilever resonator sensor, and a waveguide integrated PIN photodiode within a single epitaxial growth. The system is designed to be implemented on one InP wafer with epitaxially grown layers to create each of the independent subsystems and also link them together into a functioning device. Multiple quantum well lasers were designed to emit at 1.55 µm wavelength, below the bandgap energy of the InGaAsP waveguide lying beneath this region. The InGaAsP-InP waveguide region is designed to function as a waveguide, as well as a cantilever resonator and is created with slight tensile strain. These waveguides are clad with an underlying InGaAs sacrificial material that can be removed to create released moveable structures. This sacrificial cladding has a lower bandgap energy than the emitted wavelength and thus is designed to be the intrinsic absorber region for the final photodiode component of the system. An epitaxial layer growth incorporating these elements was established and characterized in-house at the Laboratory for Physical Science (LPS). This design provides a more simple alternative to more complex integration methodologies, both hybrid and monolithic.

### 1.1.2 Development of fabrication procedures

Fabrication processes were developed and established in order to realize the first physical implementation of a fully integrated optical MEMS microsystem. Dielectric deposition techniques, metallization, and other fabrication steps were all performed on an InP substrate first, and then on epitaxially grown substrates. A significant effort was made in establishing inductively coupled plasma (ICP) etching steps that were utilized for the definition of laser facets, waveguides and deep electrical isolation trenches. Each fabrication step needed to be carefully optimized in the perspective of being compatible with each section of the epitaxial growth and each additional fabrication step. This successful fabrication process with such a complex epitaxial growth is a milestone for III-V based optical MEMS research.

### 1.1.3 Testing of each component in the system

Each component of the fabricated microsystem was tested separately in an attempt to verify the operation of each subsystem. Characterization of each: laser, waveguide, and photodiode, was carried out with standard methods and procedures and compared with literature. The complete system was tested together in various environments ranging from cryogenic to ambient and the performance was analyzed and evaluated. Failure analysis was performed in order to better understand the critical parameters involved in the system-wide integration of these subsystems.

### Dissertation structure

This dissertation is structured as follows: A literature review of optical MEMS technologies, monolithic optical integration, and sensor methodologies will be presented in section 2, meant to give a background of the current technologies available for monolithically integrated optical MEMS and sensor systems. The design of an epitaxial layer structure for this integrated system, cantilever waveguide resonators, and PIN photodiodes with relevant simulations and modeling will be presented in section 3. Section 4 covers the fabrication of the microsystem, with details covering each unit-process developed to enable the final structure. Testing elements such as setup and experimental procedures with the associated results of laser diodes, cantilever waveguides, and PIN diode results will be presented in the context of the two major fabrication runs accomplished with epitaxial growths in section 5. The data analysis and further discussion of the results from both of these fabrication runs will also be given in section 5. Finally section 6 will present a brief summary of the results, future work, and a final conclusion.

### 2 Literature Review

### History of MEMS technologies

Micro-electro-mechanical Systems (MEMS) are traditionally described as the integration of mechanical elements with electronics on the microscale. Electronic components often are forced to interact with the environment through the use of external sensors and actuators. Combining these two separate functionalities via multi-chip packages or other interconnection and packaging techniques introduce unwanted parasitic effects, particularly as circuits and electronic equipment continue to be miniaturized. MEMS technology aims to address these shortcomings, which often lead to reduced sensitivity and increased power consumption, by miniaturizing external sensors to the point of integrating them directly alongside the IC control and readout circuitry [33, 34].

Arguably more important however, MEMS take advantage of the high volume and parallel fabrication which make the IC fabrication industry so cost effective for high volume production [33]. IT is the hope that this approach will greatly reduce the cost of sensors, increase sensor reliability, and decrease assembly complication. Due to their small size, a number of sensing or actuating functions can be integrated monolithically in the same device, further reducing cost, chip size, and increasing functionality [35]. All of these factors contribute to making MEMS sensors more attractive than many of their macro counterparts [36] and have continued to drive the continues investment in this technology both in academia and industry.

There have been a number of MEMS commercialization successes which capitalize on the aforementioned high volume production, most notably accelerometers, gyroscopes, projection systems, and pressure sensors [37]. The MEMS mechanical elements in these examples are generally fabricated using techniques common with standard IC fabrication such as lithography and dry etching. Certain cases however require more specialized tools and processes in order to realize. These techniques, generalized in the term "micromachining," consist of primarily two basic processes: bulk micromachining and surface micromachining.

Bulk micromachining indicates that the fabrication process involves removing large portions of the substrate, in most cases silicon, to fabricate a mechanical structure [38]. Most commonly, wet etching processes are used in bulk micromachining due to their high etch rates and ease of implementation. Examples such as the anisotropic etchants potassium hydroxide (KOH), tetramethylammonium hydroxide (TMAH), and ethylenediamene pyrocatecol (EDP) and the isotropic hydrofluoric, nitric, and acetic acid (HNA) etchant [35] are common in bulk removal. In addition to wet etching, some "dry" etching processes have been developed to perform the same tasks without the added complexity of drying fragile mechanical devices after wet processing. Xenon diflouride (XeF<sub>2</sub>) gas is used to etch silicon isotropic ally, and other fluorine chemistries are used in conjunction with plasma etching systems to etch isotropically. Deep Reactive Ion Etching (DRIE) provides an anisotropic plasma etch, however is a special case of bulk removal as a cyclic etching technique.

Surface micromachining processes involve releasing thin layers of material that have been deposited and patterned on top of the substrate and tend to be more compatible with the traditional IC fabrication processes due to their smaller scale. An illustrative and common example of surface micromachining is associated with the fabrication of CVD polysilicon structures. A sacrificial layer such as silicon dioxide (SiO<sub>2</sub>) is deposited on the substrate due to its high selectivity in a hydrofluoric acid (HF) etch compared to bulk silicon and polysilicon. On top of the SiO<sub>2</sub> sacrificial layer, a layer of polysilicon is deposited. Once it is deposited, the sacrificial layer is removed via a number of undercutting techniques, yielding a thin, released structure made from deposited films. Modern accelerometers utilize this fabrication method. Examples of silicon on insulator (SOI) substrates utilizing a similar fabrication scheme are very common, however with the added advantage of a single-crystal suspended mechanical layer as opposed to the amorphous polysilicon.

### **Optical MEMS**

MEMS research has expanded greatly since the early 1980's and has generated a number of specializations, one of which is the field of micro-optomechanical systems (MOEMS). Optical MEMS are a subset of the MEMS research field which specifically deals with light generation and manipulation using microscale structures and elements. As mentioned in section 0, these devices are designed and intended to take advantage of the highly parallel fabrication methods inherent in IC fabrication technologies. Many different technological focuses lie in the scope of optical MEMS with current research focus on display technologies [39, 40], biomedical imaging [41, 42], miniaturized camera lenses [43], FTIR spectrometers

[44, 45], astronomy [46, 47], photonic integrated circuits (PIC's) [48, 49], free-space optical routing and beam steering [50-52], and tunable lasers [53-56] to name a few examples.

A large number of materials are used in the development of these devices, such as: silicon, polymers, or III-V direct bandgap semiconductors. The selection of the materials depends on the application and level of system integration desired. Optical MEMS can be generalized into two major categories of system architectures: free-space and guided.

### 2.1.1 Free-Space optical MEMS

As the name suggests, free-space optical MEMS devices process light by using mirrors and refractive elements. Common examples of free-space optical MEMS are optical switches and routers for fiber communications applications, laser scanning mirrors, micro lens technologies, and interferometers [57, 58]. Devices targeted for communications technologies are considered beneficial for very large scale applications such as backbone networks due to their flexibility and scalability with data format and port count, relative wavelength insensitivity, and also for their relative low power consumption compared to traditional macroscale counterparts [57]. Free-space switches also benefit from high throughput and protocol transparency for transport. These beam routing examples showcase designs which incorporate simple "on-off" mirrors which block or transmit light [59, 60]; however some work has concentrated more on beam steering devices [40, 50-52, 61, 62 2003, 2003, 2003, 63-65]. An elegant example of an optical MEMS free-space router was initially reported by Ford *et al* [66] and later finalized by Neilson *et al* [67], and

describes two arrays of 2-axis beam steering mirrors which utilize microlens arrays to help collimate the beams as they are propagated through the system (Figure 2.1).

Figure 2.1 Schematic representation of and optical MEMS beam steering switch and a top down image [67].

Figure 2.2. SEM image of tilt mirrors for and optical MEMS add/drop switch [66].

Other examples of multi axis tilt mirrors exist [68], however the importance of this specific device is that it was designed in the context of a complete system for use

with industry standard single mode fibers, at 1.55 µm wavelengths. propagating single-mode beams for such a distance (257 mm), care must be taken to reduce beam divergence and loss from the mirrors and internal components. A microlens array and other free space optics are essential to achieving the low insertion loss in this system in preventing this excessive divergence in the propagating beams. Beyond costs associated with commercializing such a system, the major drawback to this configuration is slow switching speed and crosstalk and loss that can be experienced during beam switching. Notable examples of commercial free-space optical MEMS are the LambdaRouter<sup>TM</sup> [52], and the Texas Instruments Digital Mirror Device<sup>TM</sup> (DMD<sup>TM</sup>) [40]. The LambdaRouter<sup>TM</sup> is a predecessor to the devices shown in [67] and in the same way uses arrays of analog, tilt-able, two axis micromirrors to perform non-blocking transmission through free space onto another array of positionable mirrors which then direct the beams to the output port. More recent versions of these multi-axis deflectable mirrors exist such as those reported by Kim *et al* [68].

Figure 2.3 Lucent WaveStar LambdaRounter<sup>TM</sup> [52].

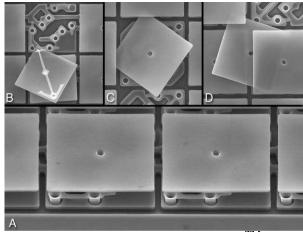

Figure 2.4. SEM images of multi axis high form factor micromirrors [68].

The Texas Instruments DMD<sup>TM</sup> spatial light modulator (SLM) (Figure 2.5), possibly one of the most ubiquitous and successful examples of optical MEMS devices, is a projection device which uses an array of binary tilting micromirrors to reflect pixels to a screen or surface. These mirrors tilt in a way to generate an on/off pixel to a final projected image. In conjunction with a color wheel and via fast switching, colorized and moving images are projected onto a screen after reflecting from this dynamic pixel array through focusing optics. This technology has been used for everything from consumer electronics displays [69] to complex 3D maskless lithography tools [70] and benefits from its very simple operational principle.

Figure 2.5 Texas Instruments DMD<sup>TM</sup> [40].

Scanning micromirrors are used to scan laser beams over surfaces for either display [71-73] or imaging technologies [44]. These devices typically utilize resonant structures in order to achieve high raster speeds and large mirror displacements. Biomedical applications are often targeted with these single scanning mirrors due to their small size and low power consumption, making them ideal for endoscopic and in-vivo imaging applications [74].

Although these devices have a number of applications and have seen commercial success, the eventual integration of these devices with external components can be difficult due to their out-of-plane operation. Intricate and custom packages are needed to fully implement real-world examples of these devices, particularly those intended for communications applications. This increase in packaging complexity increases future cost, decreases multi-device integration, and ultimately limits deployment possibilities.

### 2.1.2 Guided optical MEMS

Due to their out-of-plane operation, free-space optical MEMS do not lend themselves toward the integration of multiple components onto a single substrate

without extraneous post-processing (something which has proven to be a critical driver for the success of the IC industry). Utilizing a guided-optics architecture provides more control over light routing on chip, and opens up a number of additional technological applications such as refractive index sensing, and nonlinear optics. Free-space optical MEMS often experience less optical loss than the guided optical MEMS devices. This is due to the reduced surface roughness of planar surfaces compared to that of etched sidewalls or waveguides in most guided optical MEMS, which cause scattering losses. High throughput via multiple optical channels can be limited with guided optics due to the limited options for reconfiguring optical pathways and the wavelength dependent optical dispersion. When considering these technologies from a systems integration perspective however, these drawbacks are offset by the fact that in-plane guided optics are easier to combine with other optical elements, and allow for more control over the routing of light signals since their paths are lithographically defined, rather than straight-line propagation. This approach therefore leads to the potential for high levels of integration [75] due to this in-plane optical propagation which is easier to package with other components.

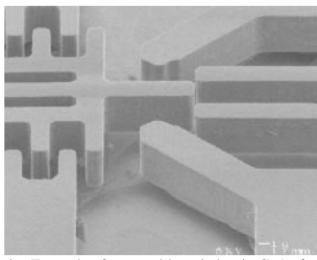

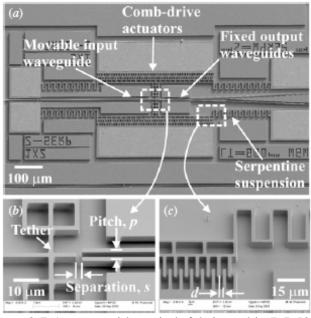

For communications applications, a large majority of waveguide optical MEMS are optical switch implementations. The basic switch architectures consists of an actuated moving waveguide or fiber cantilever which couples light from an input port into several output ports via the waveguide movement. Coupling between waveguides is usually achieved via butt coupled cantilever-like devices [26, 76-81] or evanescently coupled parallel waveguides and other resonant structures [82-87].

There have been a number of high throughput switches constructed and proposed using guided optical MEMS switches, but due to insertion losses, most require complex solutions like index matching fluids to allow for off and on-chip coupling. For example, Ollier *et al* [80] demonstrated seven 1×2 switches which have been cascaded into a 1×8 optical switch. The insertion loss of this device was measured to be 1.5 dB, and was achieved only after using index matching fluid in the gap region over which the light was traveling in free space. Other examples of 1×*n* optical waveguide switches are present in the field of optical MEMS [38, 57, 81, 88-90]; relevant examples of two of these devices are shown in Figure 2.6 and Figure 2.7. These two examples are particularly important because they utilize III-V compound semiconductors in their construction, which will be discussed in the next section.

Figure 2.6 Example of waveguide switches in GaAs from [91]

Figure 2.7 A waveguide switch fabricated in InP [26].

### 2.1.3 III-V optical MEMS

Integration of components is a common theme in the design and implementation of optical MEMS, as it was in standard MEMS technologies, and serves as the driving force behind much of the research development. The integration of optical components is often not as straightforward as the integration of electronic counterparts. Optical components often require a variety of different materials, interconnects, and strict alignment tolerances which increases the complexity of this task. Monolithic integration, which has been demonstrated repeatedly in MEMS [92-95], is even more difficult to achieve. Optical MEMS devices fabricated from III-V direct-bandgap semiconductors have the distinct advantage to allow for both passive and active optoelectronics within a single substrate. Many optical components rely on physically cleaved crystal planes to create optical quality reflectors and facets; promoting multi-chip integration solutions rather than a single chip. With improved fabrication methods and materials, systems can be constructed without the need for

cleaving and aligning multiple chips; creating new possibilities for monolithic fabrication of optical MEMS systems.

III-V materials for MEMS and optical MEMS have been pursued due to the control over specific material properties (stress, bandgap, lattice constant) when performing epitaxy of the compound semiconductors providing for the development of mechanical and active optical elements within the same substrate. Additionally, etch selectivity is easily achieved between different compositions of lattice matched materials allowing for the development of etch stops, sacrificial layers, and single crystal device layers. These properties are made possible through the growth of single-crystal substrates by way of molecular beam epitaxy (MBE) and metalorganic vapor phase epitaxy (MOVPE). Examples of materials that can be grown with varying bandgaps and lattice constants is illustrated in Figure 2.8. While there have been a many MEMS devices developed in these III-V material systems which take advantage of the piezoelectric properties [96-99], high electron mobility [100], or thermoelectric properties [101], the majority of examples take advantage of the configurable optical properties of these materials.

Figure 2.8 Diagram showing the relationship between material composition, lattice constant, and bandgap for some common III-V compound semiconductors [102].

A large number of III-V semiconductor compounds are direct-bandgap materials, making them suitable for the generation and detection of light. Furthermore these devices can be grown with variable bandgaps and compositions with the same lattice constant (see Figure 2.8), providing for optical, mechanical, and chemical tunability. Various devices can be created by growth of these materials.

The devices shown in Figure 2.6 and Figure 2.7 utilize the wet etch selectivity in order to fabricate suspended structures critical for optical MEMS devices by growing etch selective layers between a bottom substrate and top waveguide layer. Bakke *et al* and utilize GaAs/AlGaAs [79] while Pruessner *et al* and InP/InGaAs [26]. For each of these examples and others as well, the InP and GaAs layers are grown on the top of a single crystal sacrificial layer which is removed to facilitate suspended structures [103, 104]. Pruessner *et al* has created other devices such as evanescent

couplers using a similar material system [30]. High-quality, low loss, single crystal waveguides are created in this architecture by utilizing atomically smooth, lattice matched sacrificial layers.

Chemical etching selectivity, tight thickness control, and atomic-level surface roughness is exploited in the fabrication of optical filters and distributed Bragg reflectors (DBR). Tunable filters utilizing Fabry-Perot cavities have been widely implemented [103, 105-109]. Fabry-Perot filters are constructed in this architecture with distributed Bragg reflector (DBR) mirrors in the plane of the substrate in order to take advantage of the atomic smoothness and the tight control over layer thicknesses inherent in epitaxy. A sacrificial material can be grown between subsequent single-crystal semiconductor slabs, which allow for the creation of air cavities to facilitate DBRs and Fabry-Perot cavities. Irmer *et al* [106] demonstrates an example of one of these devices (Figure 2.9), and illustrates the wide tunability of these moveable mirror devices (142 nm).

Figure 2.9 Out of plane electrostatically tuned Fabry-Perot filter in InP [106] with a) SEM showing a device, and b) Schematic design.

## 2.1.4 III-V integrated photodetectors

III-V semiconductors are traditionally used for opto-electronics applications due to their direct bandgap and high electron mobilities. Particularly, highly sensitive photodiodes are one of the many conventional applications of these materials. They are ideally suited for these devices because of the control over the material's direct bandgap, allowing for heterostructures with differing bandgaps to be grown in tandem, enhancing device applications.

Planar silicon photodetectors located at the surface of a substrate suffer from limited absorption volumes and only capture a fraction of the incident photon flux, as the depletion region created in this type of geometry is small. Buried diode configurations, which have larger depletion regions beneath the surface of the semiconductor, experience reduced incident flux due to the slight absorption in the top semiconductor layers before reaching the depletion region where recombination occurs. III-V semiconductors along with epitaxial growth allow for semiconductor regions with varying bandgaps and indices of refraction. This sort of control over the semiconductor properties allows one to make the top semiconductor layers of a planar photodiode to be transparent to the incident radiation, while maintaining absorption properties in some of the underlying material. Heterostructure surface illuminated PIN diodes are made in this configuration.

A major bandwidth limiting factor in normal incidence illuminated PIN photodiodes (see Figure 2.10) is the transit time of the photogenerated carriers through the intrinsically doped photon absorption region and to the P and N doped sides of the diode. Reducing the thickness of the absorption layer will clearly

decrease the time of transit from the p to the n type regions, but simultaneously reduces the absorption crossection encountered by incoming radiation, reducing the responsivity of the photodiode. This raises a clear disadvantage to obtaining high bandwidth and high quantum efficiency simultaneously [110, 111].